Datasheet STM32F405xx, STM32F407xx - 9

| Описание | ARM Cortex-M4 32b MCU+FPU, 210DMIPS, up to 1MB Flash/192+4KB RAM, USB OTG HS/FS, Ethernet, 17 TIMs, 3 ADCs, 15 comm. interfaces & camera |

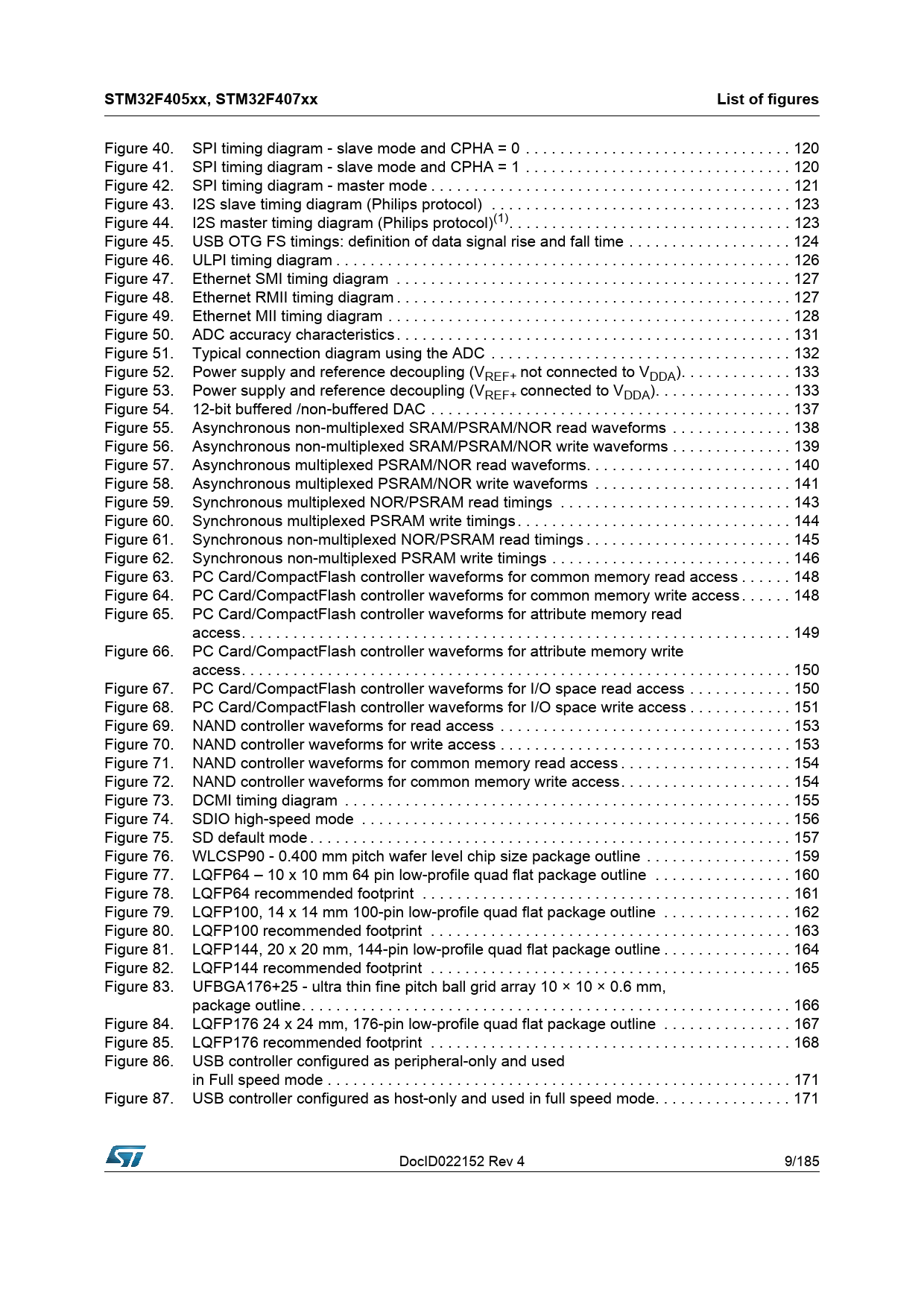

| Страниц / Страница | 185 / 9 — STM32F405xx, STM32F407xx. List of figures |

| Формат / Размер файла | PDF / 5.6 Мб |

| Язык документа | английский |

STM32F405xx, STM32F407xx. List of figures

Текстовая версия документа

link to page 120 link to page 120 link to page 121 link to page 123 link to page 123 link to page 124 link to page 126 link to page 127 link to page 127 link to page 128 link to page 131 link to page 132 link to page 133 link to page 133 link to page 137 link to page 138 link to page 139 link to page 140 link to page 141 link to page 143 link to page 144 link to page 145 link to page 146 link to page 148 link to page 148 link to page 149 link to page 150 link to page 150 link to page 151 link to page 153 link to page 153 link to page 154 link to page 154 link to page 155 link to page 156 link to page 157 link to page 159 link to page 160 link to page 161 link to page 162 link to page 163 link to page 164 link to page 165 link to page 166 link to page 167 link to page 168 link to page 171 link to page 171

STM32F405xx, STM32F407xx List of figures

Figure 40. SPI timing diagram - slave mode and CPHA = 0 . 120 Figure 41. SPI timing diagram - slave mode and CPHA = 1 . 120 Figure 42. SPI timing diagram - master mode . 121 Figure 43. I2S slave timing diagram (Philips protocol) . 123 Figure 44. I2S master timing diagram (Philips protocol)(1). 123 Figure 45. USB OTG FS timings: definition of data signal rise and fall time . 124 Figure 46. ULPI timing diagram . 126 Figure 47. Ethernet SMI timing diagram . 127 Figure 48. Ethernet RMII timing diagram . 127 Figure 49. Ethernet MII timing diagram . 128 Figure 50. ADC accuracy characteristics . 131 Figure 51. Typical connection diagram using the ADC . 132 Figure 52. Power supply and reference decoupling (VREF+ not connected to VDDA). 133 Figure 53. Power supply and reference decoupling (VREF+ connected to VDDA). 133 Figure 54. 12-bit buffered /non-buffered DAC . 137 Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . 138 Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . 139 Figure 57. Asynchronous multiplexed PSRAM/NOR read waveforms. 140 Figure 58. Asynchronous multiplexed PSRAM/NOR write waveforms . 141 Figure 59. Synchronous multiplexed NOR/PSRAM read timings . 143 Figure 60. Synchronous multiplexed PSRAM write timings . 144 Figure 61. Synchronous non-multiplexed NOR/PSRAM read timings . 145 Figure 62. Synchronous non-multiplexed PSRAM write timings . 146 Figure 63. PC Card/CompactFlash controller waveforms for common memory read access . 148 Figure 64. PC Card/CompactFlash controller waveforms for common memory write access . 148 Figure 65. PC Card/CompactFlash controller waveforms for attribute memory read access. 149 Figure 66. PC Card/CompactFlash controller waveforms for attribute memory write access. 150 Figure 67. PC Card/CompactFlash controller waveforms for I/O space read access . 150 Figure 68. PC Card/CompactFlash controller waveforms for I/O space write access . 151 Figure 69. NAND controller waveforms for read access . 153 Figure 70. NAND controller waveforms for write access . 153 Figure 71. NAND controller waveforms for common memory read access . 154 Figure 72. NAND controller waveforms for common memory write access. 154 Figure 73. DCMI timing diagram . 155 Figure 74. SDIO high-speed mode . 156 Figure 75. SD default mode . 157 Figure 76. WLCSP90 - 0.400 mm pitch wafer level chip size package outline . 159 Figure 77. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline . 160 Figure 78. LQFP64 recommended footprint . 161 Figure 79. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline . 162 Figure 80. LQFP100 recommended footprint . 163 Figure 81. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline . 164 Figure 82. LQFP144 recommended footprint . 165 Figure 83. UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline. 166 Figure 84. LQFP176 24 x 24 mm, 176-pin low-profile quad flat package outline . 167 Figure 85. LQFP176 recommended footprint . 168 Figure 86. USB controller configured as peripheral-only and used in Full speed mode . 171 Figure 87. USB controller configured as host-only and used in full speed mode. 171 DocID022152 Rev 4 9/185 Document Outline Table 1. Device summary 1 Introduction 2 Description Table 2. STM32F405xx and STM32F407xx: features and peripheral counts 2.1 Full compatibility throughout the family Figure 1. Compatible board design between STM32F10xx/STM32F4xx for LQFP64 Figure 2. Compatible board design STM32F10xx/STM32F2xx/STM32F4xx for LQFP100 package Figure 3. Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package Figure 4. Compatible board design between STM32F2xx and STM32F4xx for LQFP176 and BGA176 packages 2.2 Device overview Figure 5. STM32F40x block diagram 2.2.1 ARM® Cortex™-M4F core with embedded Flash and SRAM 2.2.2 Adaptive real-time memory accelerator (ART Accelerator™) 2.2.3 Memory protection unit 2.2.4 Embedded Flash memory 2.2.5 CRC (cyclic redundancy check) calculation unit 2.2.6 Embedded SRAM 2.2.7 Multi-AHB bus matrix Figure 6. Multi-AHB matrix 2.2.8 DMA controller (DMA) 2.2.9 Flexible static memory controller (FSMC) 2.2.10 Nested vectored interrupt controller (NVIC) 2.2.11 External interrupt/event controller (EXTI) 2.2.12 Clocks and startup 2.2.13 Boot modes 2.2.14 Power supply schemes 2.2.15 Power supply supervisor Figure 7. Power supply supervisor interconnection with internal reset OFF Figure 8. PDR_ON and NRST control with internal reset OFF 2.2.16 Voltage regulator Figure 9. Regulator OFF Figure 10. Startup in regulator OFF mode: slow VDD slope - power-down reset risen after VCAP_1/VCAP_2 stabilization Figure 11. Startup in regulator OFF mode: fast VDD slope - power-down reset risen before VCAP_1/VCAP_2 stabilization 2.2.17 Regulator ON/OFF and internal reset ON/OFF availability Table 3. Regulator ON/OFF and internal reset ON/OFF availability 2.2.18 Real-time clock (RTC), backup SRAM and backup registers 2.2.19 Low-power modes 2.2.20 VBAT operation 2.2.21 Timers and watchdogs Table 4. Timer feature comparison 2.2.22 Inter-integrated circuit interface (I²C) 2.2.23 Universal synchronous/asynchronous receiver transmitters (USART) Table 5. USART feature comparison 2.2.24 Serial peripheral interface (SPI) 2.2.25 Inter-integrated sound (I2S) 2.2.26 Audio PLL (PLLI2S) 2.2.27 Secure digital input/output interface (SDIO) 2.2.28 Ethernet MAC interface with dedicated DMA and IEEE 1588 support 2.2.29 Controller area network (bxCAN) 2.2.30 Universal serial bus on-the-go full-speed (OTG_FS) 2.2.31 Universal serial bus on-the-go high-speed (OTG_HS) 2.2.32 Digital camera interface (DCMI) 2.2.33 Random number generator (RNG) 2.2.34 General-purpose input/outputs (GPIOs) 2.2.35 Analog-to-digital converters (ADCs) 2.2.36 Temperature sensor 2.2.37 Digital-to-analog converter (DAC) 2.2.38 Serial wire JTAG debug port (SWJ-DP) 2.2.39 Embedded Trace Macrocell™ 3 Pinouts and pin description Figure 12. STM32F40x LQFP64 pinout Figure 13. STM32F40x LQFP100 pinout Figure 14. STM32F40x LQFP144 pinout Figure 15. STM32F40x LQFP176 pinout Figure 16. STM32F40x UFBGA176 ballout Figure 17. STM32F40x WLCSP90 ballout Table 6. Legend/abbreviations used in the pinout table Table 7. STM32F40x pin and ball definitions Table 8. FSMC pin definition Table 9. Alternate function mapping 4 Memory mapping Figure 18. STM32F40x memory map Table 10. STM32F40x register boundary addresses 5 Electrical characteristics 5.1 Parameter conditions 5.1.1 Minimum and maximum values 5.1.2 Typical values 5.1.3 Typical curves 5.1.4 Loading capacitor 5.1.5 Pin input voltage Figure 19. Pin loading conditions Figure 20. Pin input voltage 5.1.6 Power supply scheme Figure 21. Power supply scheme 5.1.7 Current consumption measurement Figure 22. Current consumption measurement scheme 5.2 Absolute maximum ratings Table 11. Voltage characteristics Table 12. Current characteristics Table 13. Thermal characteristics 5.3 Operating conditions 5.3.1 General operating conditions Table 14. General operating conditions Table 15. Limitations depending on the operating power supply range 5.3.2 VCAP_1/VCAP_2 external capacitor Figure 23. External capacitor CEXT Table 16. VCAP_1/VCAP_2 operating conditions 5.3.3 Operating conditions at power-up / power-down (regulator ON) Table 17. Operating conditions at power-up / power-down (regulator ON) 5.3.4 Operating conditions at power-up / power-down (regulator OFF) Table 18. Operating conditions at power-up / power-down (regulator OFF) 5.3.5 Embedded reset and power control block characteristics Table 19. Embedded reset and power control block characteristics 5.3.6 Supply current characteristics Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled) Figure 24. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator ON) or RAM, and peripherals OFF Figure 25. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator ON) or RAM, and peripherals ON Figure 26. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals OFF Figure 27. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals ON Table 22. Typical and maximum current consumption in Sleep mode Table 23. Typical and maximum current consumptions in Stop mode Table 24. Typical and maximum current consumptions in Standby mode Table 25. Typical and maximum current consumptions in VBAT mode Figure 28. Typical VBAT current consumption (LSE and RTC ON/backup RAM OFF) Figure 29. Typical VBAT current consumption (LSE and RTC ON/backup RAM ON) Table 26. Switching output I/O current consumption Table 27. Peripheral current consumption 5.3.7 Wakeup time from low-power mode Table 28. Low-power mode wakeup timings 5.3.8 External clock source characteristics Table 29. High-speed external user clock characteristics Table 30. Low-speed external user clock characteristics Figure 30. High-speed external clock source AC timing diagram Figure 31. Low-speed external clock source AC timing diagram Table 31. HSE 4-26 MHz oscillator characteristics Figure 32. Typical application with an 8 MHz crystal Table 32. LSE oscillator characteristics (fLSE = 32.768 kHz) Figure 33. Typical application with a 32.768 kHz crystal 5.3.9 Internal clock source characteristics Table 33. HSI oscillator characteristics Table 34. LSI oscillator characteristics Figure 34. ACCLSI versus temperature 5.3.10 PLL characteristics Table 35. Main PLL characteristics Table 36. PLLI2S (audio PLL) characteristics 5.3.11 PLL spread spectrum clock generation (SSCG) characteristics Table 37. SSCG parameters constraint Figure 35. PLL output clock waveforms in center spread mode Figure 36. PLL output clock waveforms in down spread mode 5.3.12 Memory characteristics Table 38. Flash memory characteristics Table 39. Flash memory programming Table 40. Flash memory programming with VPP Table 41. Flash memory endurance and data retention 5.3.13 EMC characteristics Table 42. EMS characteristics Table 43. EMI characteristics 5.3.14 Absolute maximum ratings (electrical sensitivity) Table 44. ESD absolute maximum ratings Table 45. Electrical sensitivities 5.3.15 I/O current injection characteristics Table 46. I/O current injection susceptibility 5.3.16 I/O port characteristics Table 47. I/O static characteristics Table 48. Output voltage characteristics Table 49. I/O AC characteristics Figure 37. I/O AC characteristics definition 5.3.17 NRST pin characteristics Table 50. NRST pin characteristics Figure 38. Recommended NRST pin protection 5.3.18 TIM timer characteristics Table 51. Characteristics of TIMx connected to the APB1 domain Table 52. Characteristics of TIMx connected to the APB2 domain 5.3.19 Communications interfaces Table 53. I2C characteristics Figure 39. I2C bus AC waveforms and measurement circuit Table 54. SCL frequency (fPCLK1= 42 MHz.,VDD = 3.3 V) Table 55. SPI dynamic characteristics Figure 40. SPI timing diagram - slave mode and CPHA = 0 Figure 41. SPI timing diagram - slave mode and CPHA = 1 Figure 42. SPI timing diagram - master mode Table 56. I2S dynamic characteristics Figure 43. I2S slave timing diagram (Philips protocol) Figure 44. I2S master timing diagram (Philips protocol)(1) Table 57. USB OTG FS startup time Table 58. USB OTG FS DC electrical characteristics Figure 45. USB OTG FS timings: definition of data signal rise and fall time Table 59. USB OTG FS electrical characteristics Table 60. USB HS DC electrical characteristics Table 61. USB HS clock timing parameters Table 62. ULPI timing Figure 46. ULPI timing diagram Table 63. Ethernet DC electrical characteristics Figure 47. Ethernet SMI timing diagram Table 64. Dynamic characteristics: Ehternet MAC signals for SMI Figure 48. Ethernet RMII timing diagram Table 65. Dynamic characteristics: Ethernet MAC signals for RMII Figure 49. Ethernet MII timing diagram Table 66. Dynamic characteristics: Ethernet MAC signals for MII 5.3.20 12-bit ADC characteristics Table 67. ADC characteristics Table 68. ADC accuracy at fADC = 30 MHz Figure 50. ADC accuracy characteristics Figure 51. Typical connection diagram using the ADC Figure 52. Power supply and reference decoupling (VREF+ not connected to VDDA) Figure 53. Power supply and reference decoupling (VREF+ connected to VDDA) 5.3.21 Temperature sensor characteristics Table 69. Temperature sensor characteristics Table 70. Temperature sensor calibration values 5.3.22 VBAT monitoring characteristics Table 71. VBAT monitoring characteristics 5.3.23 Embedded reference voltage Table 72. Embedded internal reference voltage Table 73. Internal reference voltage calibration values 5.3.24 DAC electrical characteristics Table 74. DAC characteristics Figure 54. 12-bit buffered /non-buffered DAC 5.3.25 FSMC characteristics Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms Table 75. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings Figure 56. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms Table 76. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings Figure 57. Asynchronous multiplexed PSRAM/NOR read waveforms Table 77. Asynchronous multiplexed PSRAM/NOR read timings Figure 58. Asynchronous multiplexed PSRAM/NOR write waveforms Table 78. Asynchronous multiplexed PSRAM/NOR write timings Figure 59. Synchronous multiplexed NOR/PSRAM read timings Table 79. Synchronous multiplexed NOR/PSRAM read timings Figure 60. Synchronous multiplexed PSRAM write timings Table 80. Synchronous multiplexed PSRAM write timings Figure 61. Synchronous non-multiplexed NOR/PSRAM read timings Table 81. Synchronous non-multiplexed NOR/PSRAM read timings Figure 62. Synchronous non-multiplexed PSRAM write timings Table 82. Synchronous non-multiplexed PSRAM write timings Figure 63. PC Card/CompactFlash controller waveforms for common memory read access Figure 64. PC Card/CompactFlash controller waveforms for common memory write access Figure 65. PC Card/CompactFlash controller waveforms for attribute memory read access Figure 66. PC Card/CompactFlash controller waveforms for attribute memory write access Figure 67. PC Card/CompactFlash controller waveforms for I/O space read access Figure 68. PC Card/CompactFlash controller waveforms for I/O space write access Table 83. Switching characteristics for PC Card/CF read and write cycles in attribute/common space Table 84. Switching characteristics for PC Card/CF read and write cycles in I/O space Figure 69. NAND controller waveforms for read access Figure 70. NAND controller waveforms for write access Figure 71. NAND controller waveforms for common memory read access Figure 72. NAND controller waveforms for common memory write access Table 85. Switching characteristics for NAND Flash read cycles Table 86. Switching characteristics for NAND Flash write cycles 5.3.26 Camera interface (DCMI) timing specifications Figure 73. DCMI timing diagram Table 87. DCMI characteristics 5.3.27 SD/SDIO MMC card host interface (SDIO) characteristics Figure 74. SDIO high-speed mode Figure 75. SD default mode Table 88. Dynamic characteristics: SD / MMC characteristics 5.3.28 RTC characteristics Table 89. RTC characteristics 6 Package characteristics 6.1 Package mechanical data Figure 76. WLCSP90 - 0.400 mm pitch wafer level chip size package outline Table 90. WLCSP90 - 0.400 mm pitch wafer level chip size package mechanical data Figure 77. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline Table 91. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data Figure 78. LQFP64 recommended footprint Figure 79. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline Table 92. LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package mechanical data Figure 80. LQFP100 recommended footprint Figure 81. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline Table 93. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data Figure 82. LQFP144 recommended footprint Figure 83. UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline Table 94. UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data Figure 84. LQFP176 24 x 24 mm, 176-pin low-profile quad flat package outline Table 95. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package mechanical data Figure 85. LQFP176 recommended footprint 6.2 Thermal characteristics Table 96. Package thermal characteristics 7 Part numbering Table 97. Ordering information scheme Appendix A Application block diagrams A.1 USB OTG full speed (FS) interface solutions Figure 86. USB controller configured as peripheral-only and used in Full speed mode Figure 87. USB controller configured as host-only and used in full speed mode Figure 88. USB controller configured in dual mode and used in full speed mode A.2 USB OTG high speed (HS) interface solutions Figure 89. USB controller configured as peripheral, host, or dual-mode and used in high speed mode A.3 Ethernet interface solutions Figure 90. MII mode using a 25 MHz crystal Figure 91. RMII with a 50 MHz oscillator Figure 92. RMII with a 25 MHz crystal and PHY with PLL 8 Revision history Table 98. Document revision history (continued)