DatasheetsDatasheet AVR64DD28, AVR64DD32 (Microchip)

Datasheet AVR64DD28, AVR64DD32 (Microchip)

| Производитель | Microchip |

| Описание | AVR DD Family |

| Страниц / Страница | 614 / 1 — AVR64DD32/28. AVR® DD Family. Introduction. AVR® DD Family Overview. … |

| Формат / Размер файла | PDF / 7.8 Мб |

| Язык документа | английский |

AVR64DD32/28. AVR® DD Family. Introduction. AVR® DD Family Overview. Figure 1. AVR® DD Family Overview. Preliminary Datasheet

21 предложений от 9 поставщиков 8-bit Microcontrollers - MCU 64KB, 8KB RAM, 32p, 24MHz, MVIO, 12b ADC, ZCD, DAC, 2xUART, SPI, TWI |

| AVR64DD32-I/RXB

Microchip | 143 ₽ | |

| AVR64DD32-I/PT

Microchip | 144 ₽ | |

| AVR64DD32-I/PT

Microchip | 190 ₽ | |

| AVR64DD32-I

Microchip | от 313 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

AVR64DD32/28 AVR® DD Family Introduction

The AVR64DD32/28 microcontrollers of the AVR® DD Family of microcontrollers are using the AVR® CPU with hardware multiplier running at clock speeds up to 24 MHz, with 64 KB of Flash, 8 KB of SRAM, and 256 bytes of EEPROM. The microcontrollers are available in 28- or 32-pin packages. The AVR DD Family uses the latest technologies from Microchip Technology, with a flexible and low-power architecture, including the Event System, intelligent analog features, and advanced digital peripherals.

AVR® DD Family Overview

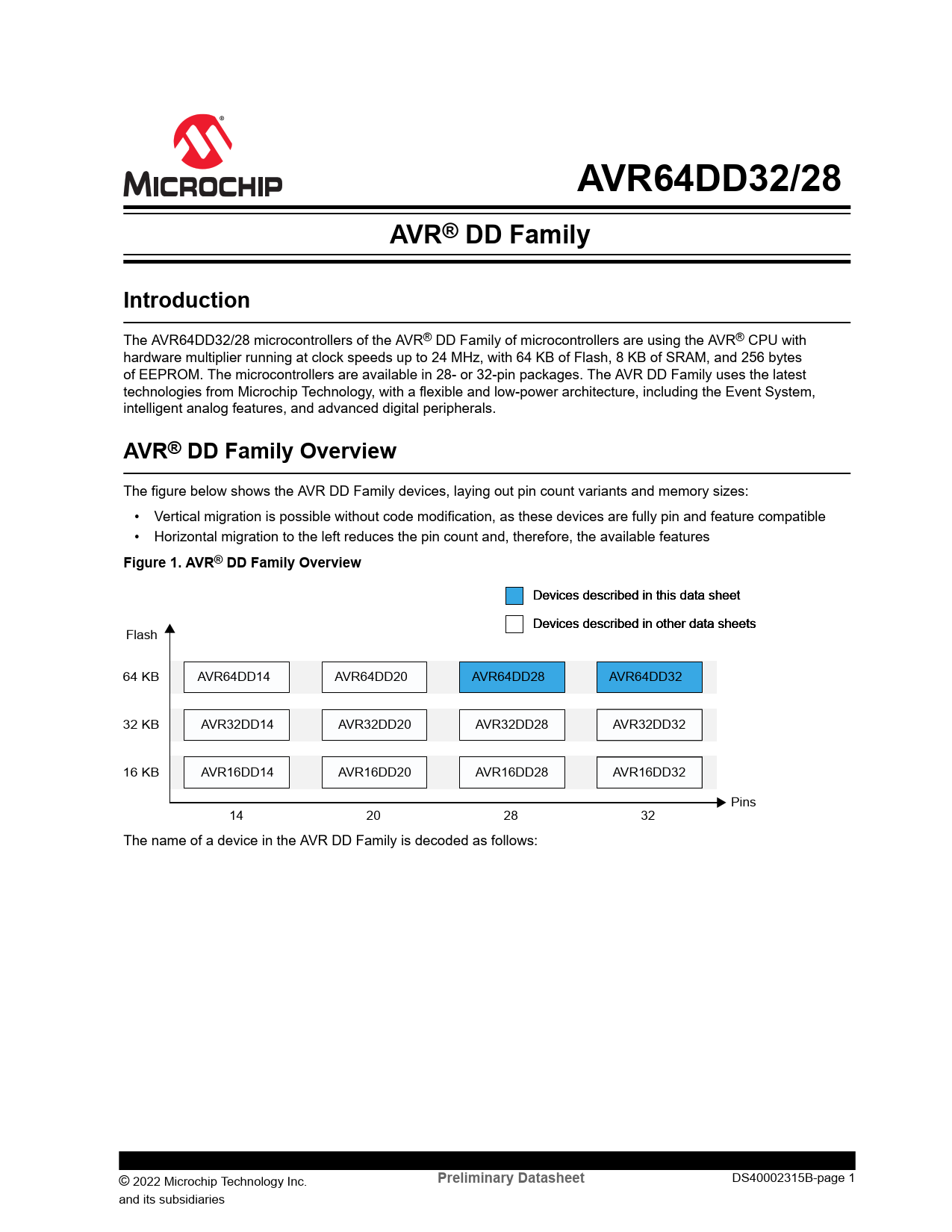

The figure below shows the AVR DD Family devices, laying out pin count variants and memory sizes: • Vertical migration is possible without code modification, as these devices are fully pin and feature compatible • Horizontal migration to the left reduces the pin count and, therefore, the available features

Figure 1. AVR® DD Family Overview

Devices described in this data sheet Devices described in other data sheets Flash 64 KB AVR64DD14 AVR64DD20 AVR64DD28 AVR64DD32 32 KB AVR32DD14 AVR32DD20 AVR32DD28 AVR32DD32 16 KB AVR16DD14 AVR16DD20 AVR16DD28 AVR16DD32 Pins 14 20 28 32 The name of a device in the AVR DD Family is decoded as follows: © 2022 Microchip Technology Inc.

Preliminary Datasheet

DS40002315B-page 1 and its subsidiaries Document Outline Introduction AVR® DD Family Overview Memory Overview Peripheral Overview Features Table of Contents 1. Block Diagram 2. Pinout 2.1. 28-Pin SPDIP, SSOP and SOIC 2.2. 28-Pin VQFN 2.3. 32-Pin VQFN and TQFP 3. I/O Multiplexing and Considerations 3.1. I/O Multiplexing 4. Hardware Guidelines 4.1. General Guidelines 4.1.1. Special Consideration for Packages with Center Pad 4.2. Connection for Power Supply 4.2.1. Digital Power Supply 4.2.2. Analog Power Supply 4.2.3. Multi-Voltage I/O 4.3. Connection for RESET 4.4. Connection for UPDI Programming 4.4.1. UPDI Connection v1 4.4.2. UPDI Connection v2 4.5. Connecting External Crystal Oscillators 4.5.1. Connection for XTAL32K (External 32.768 kHz Crystal Oscillator) 4.5.2. Connection for XTALHF (External HF Crystal Oscillator) 4.6. Connection for External Voltage Reference 5. Power Supply 5.1. Power Domains 5.2. Voltage Regulator 5.3. Power-Up 6. Conventions 6.1. Numerical Notation 6.2. Memory Size and Type 6.3. Frequency and Time 6.4. Registers and Bits 6.4.1. Addressing Registers from Header Files 6.5. ADC Parameter Definitions 7. AVR® CPU 7.1. Features 7.2. Overview 7.3. Architecture 7.3.1. Arithmetic Logic Unit (ALU) 7.3.1.1. Hardware Multiplier 7.4. Functional Description 7.4.1. Program Flow 7.4.2. Instruction Execution Timing 7.4.3. Status Register 7.4.4. Stack and Stack Pointer 7.4.5. Register File 7.4.5.1. The X-, Y-, and Z-Registers 7.4.5.2. Extended Pointers 7.4.6. Configuration Change Protection (CCP) 7.4.6.1. Sequence for Write Operation to Configuration Change Protected I/O Registers 7.4.6.2. Sequence for Execution of Self-Programming 7.4.7. On-Chip Debug Capabilities 7.5. Register Summary 7.6. Register Description 7.6.1. Configuration Change Protection 7.6.2. Stack Pointer 7.6.3. Status Register 7.6.4. Extended Z-Pointer Register 8. Memories 8.1. Overview 8.2. Memory Map 8.3. In-System Reprogrammable Flash Program Memory 8.4. SRAM Data Memory 8.5. EEPROM Data Memory 8.6. SIGROW - Signature Row 8.6.1. Signature Row Summary 8.6.2. Signature Row Description 8.6.2.1. Device ID 8.6.2.2. Temperature Sensor Calibration n 8.6.2.3. Serial Number Byte n 8.7. USERROW - User Row 8.8. FUSE - Configuration and User Fuses 8.8.1. Fuse Summary 8.8.2. Fuse Description 8.8.2.1. Watchdog Configuration 8.8.2.2. Brown-out Detector Configuration 8.8.2.3. Oscillator Configuration 8.8.2.4. System Configuration 0 8.8.2.5. System Configuration 1 8.8.2.6. Code Size 8.8.2.7. Boot Size 8.9. LOCK - Memory Sections Access Protection 8.9.1. Lock Summary 8.9.2. Lock Description 8.9.2.1. Lock Key 8.10. I/O Memory 8.10.1. Single-Cycle I/O Registers 8.10.2. Extended I/O Registers 8.10.3. Accessing 16-Bit Registers 8.10.4. Accessing 24- Bit Registers 9. Peripherals and Architecture 9.1. Peripheral Address Map 9.2. Interrupt Vector Mapping 9.3. SYSCFG - System Configuration 9.3.1. Register Summary 9.3.2. Register Description 9.3.2.1. Device Revision ID Register 10. GPR - General Purpose Registers 10.1. Register Summary 10.2. Register Description 10.2.1. General Purpose Register n 11. NVMCTRL - Nonvolatile Memory Controller 11.1. Features 11.2. Overview 11.2.1. Block Diagram 11.3. Functional Description 11.3.1. Memory Organization 11.3.1.1. Flash 11.3.1.2. EEPROM 11.3.1.3. Signature Row 11.3.1.4. User Row 11.3.1.5. Fuses 11.3.2. Memory Access 11.3.2.1. Read 11.3.2.2. Programming 11.3.2.3. Command Modes 11.3.2.3.1. Flash Write Mode 11.3.2.3.2. Flash Page Erase Mode 11.3.2.3.3. Flash Multi-Page Erase Mode 11.3.2.3.4. EEPROM Write Mode 11.3.2.3.5. EEPROM Erase/Write Mode 11.3.2.3.6. EEPROM Byte Erase Mode 11.3.2.3.7. EEPROM Multi-Byte Erase Mode 11.3.2.3.8. Chip Erase Command 11.3.2.3.9. EEPROM Erase Command 11.3.3. Preventing Flash/EEPROM Corruption 11.3.4. Interrupts 11.3.5. Sleep Mode Operation 11.3.6. Configuration Change Protection 11.4. Register Summary 11.5. Register Description 11.5.1. Control A 11.5.2. Control B 11.5.3. Status 11.5.4. Interrupt Control 11.5.5. Interrupt Flags 11.5.6. Data 11.5.7. Address 12. CLKCTRL - Clock Controller 12.1. Features 12.2. Overview 12.2.1. Block Diagram 12.2.2. Signal Description 12.3. Functional Description 12.3.1. Initialization 12.3.2. Main Clock Selection and Prescaler 12.3.3. Main Clock After Reset 12.3.4. Clock Sources 12.3.4.1. Internal Oscillators 12.3.4.1.1. Internal High-Frequency Oscillator (OSCHF) 12.3.4.1.2. 32.768 kHz Oscillator (OSC32K) 12.3.4.2. External Clock Sources 12.3.4.2.1. High-Frequency Crystal Oscillator (XOSCHF) 12.3.4.2.2. 32.768 kHz Crystal Oscillator (XOSC32K) 12.3.5. Phase-Locked Loop (PLL) 12.3.6. Manual Tuning and Auto-Tune 12.3.7. Clock Failure Detection (CFD) 12.3.7.1. Clock Failure Detection (CFD) Operation 12.3.7.2. Condition Clearing 12.3.7.3. CFD Test 12.3.7.3.1. Testing the CFD Without Influencing the Main Clock 12.3.7.3.2. Testing the CFD and Changing the Main Clock to the Start-Up Clock Source 12.3.8. Sleep Mode Operation 12.3.9. Configuration Change Protection (CCP) 12.4. Register Summary 12.5. Register Description 12.5.1. Main Clock Control A 12.5.2. Main Clock Control B 12.5.3. Main Clock Control C 12.5.4. Main Clock Interrupt Control 12.5.5. Main Clock Interrupt Flags 12.5.6. Main Clock Status 12.5.7. Internal High-Frequency Oscillator Control A 12.5.8. Internal High-Frequency Oscillator Frequency Tune 12.5.9. PLL Control A 12.5.10. 32.768 kHz Oscillator Control A 12.5.11. 32.768 kHz Crystal Oscillator Control A 12.5.12. External High-Frequency Oscillator Control A 13. SLPCTRL - Sleep Controller 13.1. Features 13.2. Overview 13.2.1. Block Diagram 13.3. Functional Description 13.3.1. Initialization 13.3.2. Voltage Regulator Configuration 13.3.3. Operation 13.3.3.1. Sleep Modes 13.3.3.2. Wake-Up Time 13.3.4. Debug Operation 13.3.5. Configuration Change Protection 13.4. Register Summary 13.5. Register Description 13.5.1. Control A 13.5.2. Voltage Regulator Control Register 14. RSTCTRL - Reset Controller 14.1. Features 14.2. Overview 14.2.1. Block Diagram 14.2.2. Signal Description 14.3. Functional Description 14.3.1. Initialization 14.3.2. Operation 14.3.2.1. Reset Sources 14.3.2.1.1. Power-on Reset (POR) 14.3.2.1.2. Brown-out Detector (BOD) Reset 14.3.2.1.3. External Reset (RESET) 14.3.2.1.4. Watchdog Timer (WDT) Reset 14.3.2.1.5. Software Reset (SWRST) 14.3.2.1.6. Unified Program and Debug Interface (UPDI) Reset 14.3.2.1.7. High Voltage (HV) Pulse 14.3.2.1.8. Domains Affected By Reset 14.3.2.2. Reset Time 14.3.3. Sleep Mode Operation 14.3.4. Configuration Change Protection 14.4. Register Summary 14.5. Register Description 14.5.1. Reset Flag Register 14.5.2. Software Reset Register 15. CPUINT - CPU Interrupt Controller 15.1. Features 15.2. Overview 15.2.1. Block Diagram 15.3. Functional Description 15.3.1. Initialization 15.3.2. Operation 15.3.2.1. Enabling, Disabling and Resetting 15.3.2.2. Interrupt Vector Locations 15.3.2.3. Interrupt Response Time 15.3.2.4. Interrupt Priority 15.3.2.4.1. Non-Maskable Interrupts 15.3.2.4.2. High-Priority Interrupt 15.3.2.4.3. Normal-Priority Interrupts 15.3.2.4.3.1. Static Scheduling 15.3.2.4.3.2. Modified Static Scheduling 15.3.2.4.3.3. Round Robin Scheduling 15.3.2.5. Compact Vector Table 15.3.3. Debug Operation 15.3.4. Configuration Change Protection 15.4. Register Summary 15.5. Register Description 15.5.1. Control A 15.5.2. Status 15.5.3. Interrupt Priority Level 0 15.5.4. Interrupt Vector with Priority Level 1 16. EVSYS - Event System 16.1. Features 16.2. Overview 16.2.1. Block Diagram 16.2.2. Signal Description 16.3. Functional Description 16.3.1. Initialization 16.3.2. Operation 16.3.2.1. Event User Multiplexer Setup 16.3.2.2. Event System Channel 16.3.2.3. Event Generators 16.3.2.4. Event Users 16.3.2.5. Synchronization 16.3.2.6. Software Event 16.3.3. Sleep Mode Operation 16.3.4. Debug Operation 16.4. Register Summary 16.5. Register Description 16.5.1. Software Events 16.5.2. Channel n Generator Selection 16.5.3. User Channel MUX 17. PORTMUX - Port Multiplexer 17.1. Overview 17.2. Register Summary 17.3. Register Description 17.3.1. EVSYS Pin Position 17.3.2. CCL LUTn Pin Position 17.3.3. USARTn Pin Position 17.3.4. SPIn Pin Position 17.3.5. TWIn Pin Position 17.3.6. TCAn Pin Position 17.3.7. TCBn Pin Position 17.3.8. TCDn Pin Position 18. PORT - I/O Pin Configuration 18.1. Features 18.2. Overview 18.2.1. Block Diagram 18.2.2. Signal Description 18.3. Functional Description 18.3.1. Initialization 18.3.2. Operation 18.3.2.1. Basic Functions 18.3.2.2. Port Configuration 18.3.2.3. Pin Configuration 18.3.2.4. Multi-Pin Configuration 18.3.2.5. Virtual Ports 18.3.2.6. Peripheral Override 18.3.2.7. Multi-Voltage I/O 18.3.3. Interrupts 18.3.3.1. Asynchronous Sensing Pin Properties 18.3.4. Events 18.3.5. Sleep Mode Operation 18.3.6. Debug Operation 18.4. Register Summary - PORTx 18.5. Register Description - PORTx 18.5.1. Data Direction 18.5.2. Data Direction Set 18.5.3. Data Direction Clear 18.5.4. Data Direction Toggle 18.5.5. Output Value 18.5.6. Output Value Set 18.5.7. Output Value Clear 18.5.8. Output Value Toggle 18.5.9. Input Value 18.5.10. Interrupt Flags 18.5.11. Port Control 18.5.12. Multi-Pin Configuration 18.5.13. Multi-Pin Control Update Mask 18.5.14. Multi-Pin Control Set Mask 18.5.15. Multi-Pin Control Clear Mask 18.5.16. Pin n Control 18.6. Register Summary - VPORTx 18.7. Register Description - VPORTx 18.7.1. Data Direction 18.7.2. Output Value 18.7.3. Input Value 18.7.4. Interrupt Flags 19. MVIO - Multi-Voltage I/O 19.1. Features 19.2. Overview 19.2.1. Block Diagram 19.2.2. Signal Description 19.3. Functional Description 19.3.1. Initialization 19.3.2. Operation 19.3.2.1. Power Sequencing 19.3.2.2. Voltage Measurement 19.3.3. Events 19.3.4. Interrupts 19.3.5. Sleep Mode Operation 19.3.6. Debug Operation 19.4. Register Summary 19.5. Register Description 19.5.1. Interrupt Control 19.5.2. Interrupt Flags 19.5.3. Status 20. BOD - Brown-out Detector 20.1. Features 20.2. Overview 20.2.1. Block Diagram 20.3. Functional Description 20.3.1. Initialization 20.3.2. Interrupts 20.3.3. Sleep Mode Operation 20.3.4. Configuration Change Protection 20.4. Register Summary 20.5. Register Description 20.5.1. Control A 20.5.2. Control B 20.5.3. VLM Control 20.5.4. Interrupt Control 20.5.5. VLM Interrupt Flags 20.5.6. VLM Status 21. VREF - Voltage Reference 21.1. Features 21.2. Overview 21.2.1. Block Diagram 21.3. Functional Description 21.3.1. Initialization 21.4. Register Summary 21.5. Register Description 21.5.1. ADC0 Reference 21.5.2. DAC0 Reference 21.5.3. Analog Comparator Reference 22. WDT - Watchdog Timer 22.1. Features 22.2. Overview 22.2.1. Block Diagram 22.3. Functional Description 22.3.1. Initialization 22.3.2. Clocks 22.3.3. Operation 22.3.3.1. Normal Mode 22.3.3.2. Window Mode 22.3.3.3. Preventing Unintentional Changes 22.3.4. Sleep Mode Operation 22.3.5. Debug Operation 22.3.6. Synchronization 22.3.7. Configuration Change Protection 22.4. Register Summary 22.5. Register Description 22.5.1. Control A 22.5.2. Status 23. TCA - 16-bit Timer/Counter Type A 23.1. Features 23.2. Overview 23.2.1. Block Diagram 23.2.2. Signal Description 23.3. Functional Description 23.3.1. Definitions 23.3.2. Initialization 23.3.3. Operation 23.3.3.1. Normal Operation 23.3.3.2. Double Buffering 23.3.3.3. Changing the Period 23.3.3.4. Compare Channel 23.3.3.4.1. Waveform Generation 23.3.3.4.2. Frequency (FRQ) Waveform Generation 23.3.3.4.3. Single-Slope PWM Generation 23.3.3.4.4. Dual-Slope PWM Generation 23.3.3.4.5. Port Override for Waveform Generation 23.3.3.5. Timer/Counter Commands 23.3.3.6. Split Mode - Two 8-Bit Timer/Counters 23.3.4. Events 23.3.5. Interrupts 23.3.6. Sleep Mode Operation 23.4. Register Summary - Normal Mode 23.5. Register Description - Normal Mode 23.5.1. Control A - Normal Mode 23.5.2. Control B - Normal Mode 23.5.3. Control C - Normal Mode 23.5.4. Control D - Normal Mode 23.5.5. Control Register E Clear - Normal Mode 23.5.6. Control Register E Set - Normal Mode 23.5.7. Control Register F Clear 23.5.8. Control Register F Set 23.5.9. Event Control 23.5.10. Interrupt Control Register - Normal Mode 23.5.11. Interrupt Flag Register - Normal Mode 23.5.12. Debug Control Register - Normal Mode 23.5.13. Temporary Bits for 16-Bit Access 23.5.14. Counter Register - Normal Mode 23.5.15. Period Register - Normal Mode 23.5.16. Compare n Register - Normal Mode 23.5.17. Period Buffer Register 23.5.18. Compare n Buffer Register 23.6. Register Summary - Split Mode 23.7. Register Description - Split Mode 23.7.1. Control A - Split Mode 23.7.2. Control B - Split Mode 23.7.3. Control C - Split Mode 23.7.4. Control D - Split Mode 23.7.5. Control Register E Clear - Split Mode 23.7.6. Control Register E Set - Split Mode 23.7.7. Interrupt Control Register - Split Mode 23.7.8. Interrupt Flag Register - Split Mode 23.7.9. Debug Control Register - Split Mode 23.7.10. Low Byte Timer Counter Register - Split Mode 23.7.11. High Byte Timer Counter Register - Split Mode 23.7.12. Low Byte Timer Period Register - Split Mode 23.7.13. High Byte Period Register - Split Mode 23.7.14. Compare Register n For Low Byte Timer - Split Mode 23.7.15. High Byte Compare Register n - Split Mode 24. TCB - 16-Bit Timer/Counter Type B 24.1. Features 24.2. Overview 24.2.1. Block Diagram 24.2.2. Signal Description 24.3. Functional Description 24.3.1. Definitions 24.3.2. Initialization 24.3.3. Operation 24.3.3.1. Modes 24.3.3.1.1. Periodic Interrupt Mode 24.3.3.1.2. Time-Out Check Mode 24.3.3.1.3. Input Capture on Event Mode 24.3.3.1.4. Input Capture Frequency Measurement Mode 24.3.3.1.5. Input Capture Pulse-Width Measurement Mode 24.3.3.1.6. Input Capture Frequency and Pulse-Width Measurement Mode 24.3.3.1.7. Single-Shot Mode 24.3.3.1.8. 8-Bit PWM Mode 24.3.3.2. Output 24.3.3.3. 32-Bit Input Capture 24.3.3.4. Noise Canceler 24.3.3.5. Synchronized with Timer/Counter Type A 24.3.4. Events 24.3.5. Interrupts 24.3.6. Sleep Mode Operation 24.4. Register Summary 24.5. Register Description 24.5.1. Control A 24.5.2. Control B 24.5.3. Event Control 24.5.4. Interrupt Control 24.5.5. Interrupt Flags 24.5.6. Status 24.5.7. Debug Control 24.5.8. Temporary Value 24.5.9. Count 24.5.10. Capture/Compare 25. TCD - 12-Bit Timer/Counter Type D 25.1. Features 25.2. Overview 25.2.1. Block Diagram 25.2.2. Signal Description 25.3. Functional Description 25.3.1. Definitions 25.3.2. Initialization 25.3.3. Operation 25.3.3.1. Register Synchronization Categories 25.3.3.2. Waveform Generation Modes 25.3.3.2.1. One Ramp Mode 25.3.3.2.2. Two Ramp Mode 25.3.3.2.3. Four Ramp Mode 25.3.3.2.4. Dual Slope Mode 25.3.3.3. Disabling TCD 25.3.3.4. TCD Inputs 25.3.3.4.1. Input Blanking 25.3.3.4.2. Digital Filter 25.3.3.4.3. Asynchronous Event Detection 25.3.3.4.4. Software Commands 25.3.3.4.5. Input Modes 25.3.3.4.5.1. Input Modes Validity 25.3.3.4.5.2. Input Mode 0: Input Has No Action 25.3.3.4.5.3. Input Mode 1: Stop Output, Jump to the Opposite Compare Cycle, and Wait 25.3.3.4.5.4. Input Mode 2: Stop Output, Execute Opposite Compare Cycle, and Wait 25.3.3.4.5.5. Input Mode 3: Stop Output, Execute Opposite Compare Cycle while Fault Active 25.3.3.4.5.6. Input Mode 4: Stop all Outputs, Maintain Frequency 25.3.3.4.5.7. Input Mode 5: Stop all Outputs, Execute Dead-Time while Fault Active 25.3.3.4.5.8. Input Mode 6: Stop All Outputs, Jump to Next Compare Cycle, and Wait 25.3.3.4.5.9. Input Mode 7: Stop all Outputs, Wait for Software Action 25.3.3.4.5.10. Input Mode 8: Stop Output on Edge, Jump to Next Compare Cycle 25.3.3.4.5.11. Input Mode 9: Stop Output on Edge, Maintain Frequency 25.3.3.4.5.12. Input Mode 10: Stop Output at Level, Maintain Frequency 25.3.3.4.5.13. Input Mode Summary 25.3.3.5. Dithering 25.3.3.6. TCD Counter Capture 25.3.3.7. Output Control 25.3.4. Events 25.3.4.1. Programmable Output Events 25.3.5. Interrupts 25.3.6. Sleep Mode Operation 25.3.7. Debug Operation 25.3.8. Configuration Change Protection 25.4. Register Summary 25.5. Register Description 25.5.1. Control A 25.5.2. Control B 25.5.3. Control C 25.5.4. Control D 25.5.5. Control E 25.5.6. Event Control A 25.5.7. Event Control B 25.5.8. Interrupt Control 25.5.9. Interrupt Flags 25.5.10. Status 25.5.11. Input Control A 25.5.12. Input Control B 25.5.13. Fault Control 25.5.14. Delay Control 25.5.15. Delay Value 25.5.16. Dither Control 25.5.17. Dither Value 25.5.18. Debug Control 25.5.19. Capture A 25.5.20. Capture B 25.5.21. Compare Set A 25.5.22. Compare Set B 25.5.23. Compare Clear A 25.5.24. Compare Clear B 26. RTC - Real-Time Counter 26.1. Features 26.2. Overview 26.2.1. RTC Block Diagram 26.3. Clocks 26.4. RTC Functional Description 26.4.1. Initialization 26.4.1.1. Configure the Clock CLK_RTC 26.4.1.2. Configure RTC 26.4.2. Operation - RTC 26.4.2.1. Enabling and Disabling 26.5. PIT Functional Description 26.5.1. Initialization 26.5.2. Operation - PIT 26.5.2.1. Enabling and Disabling 26.5.2.2. PIT Interrupt Timing 26.6. Crystal Error Correction 26.7. Events 26.8. Interrupts 26.9. Sleep Mode Operation 26.10. Synchronization 26.11. Debug Operation 26.12. Register Summary 26.13. Register Description 26.13.1. Control A 26.13.2. Status 26.13.3. Interrupt Control 26.13.4. Interrupt Flag 26.13.5. Temporary 26.13.6. Debug Control 26.13.7. Crystal Frequency Calibration 26.13.8. Clock Selection 26.13.9. Count 26.13.10. Period 26.13.11. Compare 26.13.12. Periodic Interrupt Timer Control A 26.13.13. Periodic Interrupt Timer Status 26.13.14. PIT Interrupt Control 26.13.15. PIT Interrupt Flag 26.13.16. Periodic Interrupt Timer Debug Control 27. USART - Universal Synchronous and Asynchronous Receiver and Transmitter 27.1. Features 27.2. Overview 27.2.1. Block Diagram 27.2.2. Signal Description 27.3. Functional Description 27.3.1. Initialization 27.3.2. Operation 27.3.2.1. Frame Formats 27.3.2.2. Clock Generation 27.3.2.2.1. The Fractional Baud Rate Generator 27.3.2.3. Data Transmission 27.3.2.3.1. Disabling the Transmitter 27.3.2.4. Data Reception 27.3.2.4.1. Receiver Error Flags 27.3.2.4.2. Disabling the Receiver 27.3.2.4.3. Flushing the Receive Buffer 27.3.3. Communication Modes 27.3.3.1. Synchronous Operation 27.3.3.1.1. Clock Operation 27.3.3.1.2. External Clock Limitations 27.3.3.1.3. USART in Host SPI Mode 27.3.3.1.3.1. Frame Formats 27.3.3.1.3.2. Clock Generation 27.3.3.1.3.3. Data Transmission 27.3.3.1.3.4. Data Reception 27.3.3.1.3.5. USART in Host SPI Mode vs. SPI 27.3.3.2. Asynchronous Operation 27.3.3.2.1. Clock Recovery 27.3.3.2.2. Data Recovery 27.3.3.2.3. Error Tolerance 27.3.3.2.4. Double-Speed Operation 27.3.3.2.5. Auto-Baud 27.3.3.2.6. Half-Duplex Operation 27.3.3.2.6.1. One-Wire Mode 27.3.3.2.6.2. RS-485 Mode 27.3.3.2.7. IRCOM Mode of Operation 27.3.4. Additional Features 27.3.4.1. Parity 27.3.4.2. Start-of-Frame Detection 27.3.4.3. Multiprocessor Communication 27.3.4.3.1. Using Multiprocessor Communication 27.3.5. Events 27.3.6. Interrupts 27.4. Register Summary 27.5. Register Description 27.5.1. Receiver Data Register Low Byte 27.5.2. Receiver Data Register High Byte 27.5.3. Transmit Data Register Low Byte 27.5.4. Transmit Data Register High Byte 27.5.5. USART Status Register 27.5.6. Control A 27.5.7. Control B 27.5.8. Control C - Normal Mode 27.5.9. Control C - Host SPI Mode 27.5.10. Baud Register 27.5.11. Control D 27.5.12. Debug Control Register 27.5.13. IrDA Control Register 27.5.14. IRCOM Transmitter Pulse Length Control Register 27.5.15. IRCOM Receiver Pulse Length Control Register 28. SPI - Serial Peripheral Interface 28.1. Features 28.2. Overview 28.2.1. Block Diagram 28.2.2. Signal Description 28.3. Functional Description 28.3.1. Initialization 28.3.2. Operation 28.3.2.1. Host Mode Operation 28.3.2.1.1. Normal Mode 28.3.2.1.2. Buffer Mode 28.3.2.1.3. SS Pin Functionality in Host Mode - Multi-Host Support 28.3.2.2. Client Mode 28.3.2.2.1. Normal Mode 28.3.2.2.2. Buffer Mode 28.3.2.2.3. SS Pin Functionality in Client Mode 28.3.2.3. Data Modes 28.3.2.4. Events 28.3.2.5. Interrupts 28.4. Register Summary 28.5. Register Description 28.5.1. Control A 28.5.2. Control B 28.5.3. Interrupt Control 28.5.4. Interrupt Flags - Normal Mode 28.5.5. Interrupt Flags - Buffer Mode 28.5.6. Data 29. TWI - Two-Wire Interface 29.1. Features 29.2. Overview 29.2.1. Block Diagram 29.2.2. Signal Description 29.3. Functional Description 29.3.1. General TWI Bus Concepts 29.3.2. TWI Basic Operation 29.3.2.1. Initialization 29.3.2.1.1. Host Initialization 29.3.2.1.2. Client Initialization 29.3.2.2. TWI Host Operation 29.3.2.2.1. Clock Generation 29.3.2.2.2. TWI Bus State Logic 29.3.2.2.3. Transmitting Address Packets 29.3.2.2.3.1. Case M1: Address Packet Transmit Complete - Direction Bit Set to ‘0’ 29.3.2.2.3.2. Case M2: Address Packet Transmit Complete - Direction Bit Set to ‘1’ 29.3.2.2.3.3. Case M3: Address Packet Transmit Complete - Address not Acknowledged by Client 29.3.2.2.3.4. Case M4: Arbitration Lost or Bus Error 29.3.2.2.4. Transmitting Data Packets 29.3.2.2.5. Receiving Data Packets 29.3.2.3. TWI Client Operation 29.3.2.3.1. Receiving Address Packets 29.3.2.3.1.1. Case S1: Address Packet Accepted - Direction Bit Set to ‘0’ 29.3.2.3.1.2. Case S2: Address Packet Accepted - Direction Bit Set to ‘1’ 29.3.2.3.1.3. Case S3: Stop Condition Received 29.3.2.3.1.4. Case S4: Collision 29.3.2.3.2. Receiving Data Packets 29.3.2.3.3. Transmitting Data Packets 29.3.3. Additional Features 29.3.3.1. SMBus 29.3.3.1.1. Compliance to SMBus Specifications 29.3.3.2. Multi-Host 29.3.3.3. Smart Mode 29.3.3.4. Dual Mode 29.3.3.5. Quick Command Mode 29.3.3.6. 10-Bit Address 29.3.4. Interrupts 29.3.5. Sleep Mode Operation 29.3.6. Debug Operation 29.4. Register Summary 29.5. Register Description 29.5.1. Control A 29.5.2. Dual Mode Control Configuration 29.5.3. Debug Control 29.5.4. Host Control A 29.5.5. Host Control B 29.5.6. Host Status 29.5.7. Host Baud Rate 29.5.8. Host Address 29.5.9. Host Data 29.5.10. Client Control A 29.5.11. Client Control B 29.5.12. Client Status 29.5.13. Client Address 29.5.14. Client Data 29.5.15. Client Address Mask 30. CRCSCAN - Cyclic Redundancy Check Memory Scan 30.1. Features 30.2. Overview 30.2.1. Block Diagram 30.3. Functional Description 30.3.1. Initialization 30.3.2. Operation 30.3.2.1. Checksum 30.3.3. Interrupts 30.3.4. Sleep Mode Operation 30.3.5. Debug Operation 30.4. Register Summary 30.5. Register Description 30.5.1. Control A 30.5.2. Control B 30.5.3. Status 31. CCL - Configurable Custom Logic 31.1. Features 31.2. Overview 31.2.1. Block Diagram 31.2.2. Signal Description 31.2.2.1. CCL Input Selection MUX 31.3. Functional Description 31.3.1. Operation 31.3.1.1. Enable-Protected Configuration 31.3.1.2. Enabling, Disabling, and Resetting 31.3.1.3. Truth Table Logic 31.3.1.4. Truth Table Inputs Selection 31.3.1.5. Filter 31.3.1.6. Edge Detector 31.3.1.7. Sequencer Logic 31.3.1.8. Clock Source Settings 31.3.2. Interrupts 31.3.3. Events 31.3.4. Sleep Mode Operation 31.4. Register Summary 31.5. Register Description 31.5.1. Control A 31.5.2. Sequencer Control 0 31.5.3. Sequencer Control 1 31.5.4. Interrupt Control 0 31.5.5. Interrupt Flag 31.5.6. LUT n Control A 31.5.7. LUT n Control B 31.5.8. LUT n Control C 31.5.9. TRUTHn 32. AC - Analog Comparator 32.1. Features 32.2. Overview 32.2.1. Block Diagram 32.2.2. Signal Description 32.3. Functional Description 32.3.1. Initialization 32.3.2. Operation 32.3.2.1. Input Hysteresis 32.3.2.2. Input and Reference Selection 32.3.2.3. Normal Mode 32.3.2.4. Power Modes 32.3.3. Events 32.3.4. Interrupts 32.3.5. Sleep Mode Operation 32.4. Register Summary 32.5. Register Description 32.5.1. Control A 32.5.2. MUX Control 32.5.3. DAC Voltage Reference 32.5.4. Interrupt Control 32.5.5. Status 33. ADC - Analog-to-Digital Converter 33.1. Features 33.2. Overview 33.2.1. Block Diagram 33.2.2. Signal Description 33.3. Functional Description 33.3.1. Definitions 33.3.2. Initialization 33.3.3. Operation 33.3.3.1. Operation Modes 33.3.3.2. Starting a Conversion 33.3.3.3. Clock Generation 33.3.3.4. Conversion Timing 33.3.3.4.1. Single Conversion 33.3.3.4.2. Accumulated Conversion 33.3.3.4.3. Free-Running Conversion 33.3.3.4.4. Adjusting Conversion Time 33.3.3.5. Conversion Result (Output Formats) 33.3.3.6. Accumulation 33.3.3.7. Channel Selection 33.3.3.8. Temperature Measurement 33.3.3.9. Window Comparator 33.3.4. I/O Lines and Connections 33.3.5. Events 33.3.6. Interrupts 33.3.7. Debug Operation 33.3.8. Sleep Mode Operation 33.3.9. Synchronization 33.3.10. Configuration Change Protection 33.4. Register Summary 33.5. Register Description 33.5.1. Control A 33.5.2. Control B 33.5.3. Control C 33.5.4. Control D 33.5.5. Control E 33.5.6. Sample Control 33.5.7. MUX Selection for Positive ADC Input 33.5.8. MUX Selection for Negative ADC Input 33.5.9. Command 33.5.10. Event Control 33.5.11. Interrupt Control 33.5.12. Interrupt Flags 33.5.13. Debug Control 33.5.14. Temporary 33.5.15. Result 33.5.16. Window Comparator Low Threshold 33.5.17. Window Comparator High Threshold 34. DAC - Digital-to-Analog Converter 34.1. Features 34.2. Overview 34.2.1. Block Diagram 34.2.2. Signal Description 34.3. Functional Description 34.3.1. Initialization 34.3.2. Operation 34.3.2.1. Enabling, Disabling and Resetting 34.3.2.2. Starting a Conversion 34.3.2.3. DAC Output 34.3.2.3.1. Unbuffered Output as Source For Internal Peripherals 34.3.2.3.2. Buffered Output 34.3.3. Sleep Mode Operation 34.4. Register Summary 34.5. Register Description 34.5.1. Control A 34.5.2. DATA 35. ZCD - Zero-Cross Detector 35.1. Features 35.2. Overview 35.2.1. Block Diagram 35.2.2. Signal Description 35.3. Functional Description 35.3.1. Initialization 35.3.2. Operation 35.3.2.1. External Resistor Selection 35.3.2.2. ZCD Logic Output 35.3.2.3. Correction for ZCPINV Offset 35.3.2.3.1. Correction By Offset Current 35.3.2.3.2. Correction by AC Coupling 35.3.2.4. Handling VPEAK Variations 35.3.3. Events 35.3.4. Interrupts 35.3.5. Sleep Mode Operation 35.4. Register Summary 35.5. Register Description 35.5.1. Control A 35.5.2. Interrupt Control 35.5.3. Status 36. UPDI - Unified Program and Debug Interface 36.1. Features 36.2. Overview 36.2.1. Block Diagram 36.2.2. Addressing the Program Memory Space 36.2.3. Clocks 36.2.4. Physical Layer 36.2.5. I/O Lines and Connections 36.3. Functional Description 36.3.1. Principle of Operation 36.3.1.1. UPDI UART 36.3.1.2. BREAK Character 36.3.1.2.1. BREAK in One-Wire Mode 36.3.1.3. SYNCH Character 36.3.1.3.1. SYNCH in One-Wire Mode 36.3.2. Operation 36.3.2.1. UPDI Enabling 36.3.2.1.1. One-Wire Enable 36.3.2.1.2. UPDI Enable with High-Voltage Override of UPDI Pin 36.3.2.2. UPDI Disabling 36.3.2.2.1. Disable During Start-Up 36.3.2.2.1.1. Time-Out Disable 36.3.2.2.1.2. Incorrect SYNCH Pattern 36.3.2.2.2. UPDI Regular Disable 36.3.2.3. UPDI Communication Error Handling 36.3.2.4. Direction Change 36.3.3. UPDI Instruction Set 36.3.3.1. LDS - Load Data from Data Space Using Direct Addressing 36.3.3.2. STS - Store Data to Data Space Using Direct Addressing 36.3.3.3. LD - Load Data from Data Space Using Indirect Addressing 36.3.3.4. ST - Store Data from UPDI to Data Space Using Indirect Addressing 36.3.3.5. LDCS - Load Data from Control and Status Register Space 36.3.3.6. STCS - Store Data to Control and Status Register Space 36.3.3.7. REPEAT - Set Instruction Repeat Counter 36.3.3.8. KEY - Set Activation Key or Send System Information Block 36.3.4. CRC Checking of Flash During Boot 36.3.5. System Clock Measurement with UPDI 36.3.6. Inter-Byte Delay 36.3.7. System Information Block 36.3.8. Enabling of Key Protected Interfaces 36.3.8.1. Chip Erase 36.3.8.2. NVM Programming 36.3.8.3. User Row Programming 36.3.9. Events 36.3.10. Sleep Mode Operation 36.4. Register Summary 36.5. Register Description 36.5.1. Status A 36.5.2. Status B 36.5.3. Control A 36.5.4. Control B 36.5.5. ASI Key Status 36.5.6. ASI Reset Request 36.5.7. ASI Control A 36.5.8. ASI System Control A 36.5.9. ASI System Status 36.5.10. ASI CRC Status 37. Instruction Set Summary 38. Electrical Characteristics 38.1. Disclaimer 38.2. Absolute Maximum Ratings 38.3. Standard Operating Conditions 38.4. Supply Voltage 38.5. Power Consumption 38.6. Peripherals Power Consumption 38.7. I/O Pins 38.8. Memory Programming Specifications 38.9. Thermal Characteristics 38.10. CLKCTRL 38.10.1. Internal Oscillators 38.10.2. XOSC32K 38.10.3. XOSCHF 38.10.4. External Clock 38.10.5. PLL 38.10.6. System Clock 38.11. RSTCTRL and BOD 38.12. VREF 38.13. USART 38.14. SPI 38.15. TWI 38.16. DAC 38.17. ADC 38.18. AC 38.19. ZCD 38.20. UPDI 39. Characteristics Graphs 40. Ordering Information 41. Package Drawings 41.1. Online Package Drawings 41.2. Package Marking Information 41.2.1. 28-Pin SPDIP 41.2.2. 28-Pin SOIC 41.2.3. 28-Pin SSOP 41.2.4. 28-Pin VQFN 41.2.5. 32-Pin VQFN 41.2.6. 32-Pin TQFP 41.3. 28-Pin SPDIP 41.4. 28-Pin SOIC 41.5. 28-Pin SSOP 41.6. 28-Pin VQFN 41.7. 32-Pin VQFN 41.8. 32-Pin TQFP 42. Data Sheet Revision History 42.1. Rev. B - 04/2022 42.2. Rev. A - 11/2021 The Microchip Website Product Change Notification Service Customer Support Product Identification System Microchip Devices Code Protection Feature Legal Notice Trademarks Quality Management System Worldwide Sales and Service

Купить AVR64DD32 на РадиоЛоцман.Цены — от 143 до 387 ₽

Купить AVR64DD32 на РадиоЛоцман.Цены — от 143 до 387 ₽