Datasheet AM2431, AM2432, AM2434 (Texas Instruments)

| Производитель | Texas Instruments |

| Описание | Arm Cortex-R5F based MCU with industrial communications and security up to 800MHz |

| Страниц / Страница | 316 / 1 — AM2434,. AM2432. , AM2431. AM243x Sitara™ Microcontrollers. 1 Features. … |

| Формат / Размер файла | PDF / 6.4 Мб |

| Язык документа | английский |

AM2434,. AM2432. , AM2431. AM243x Sitara™ Microcontrollers. 1 Features. Processor cores:. TION. Memory subsystem:. NCE INFO

, Arm® Cortex-R5F based MCU with industrial communications and security up to 800MHz |

| XAM2431ASFGGAALV

Texas Instruments | 2 686 ₽ | |

| XAM2431ASFGGAALV

Texas Instruments | 6 828 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

AM2434, AM2432 , AM2431

SPRSP65B – APRIL 2021 – REVISED JULY 2021

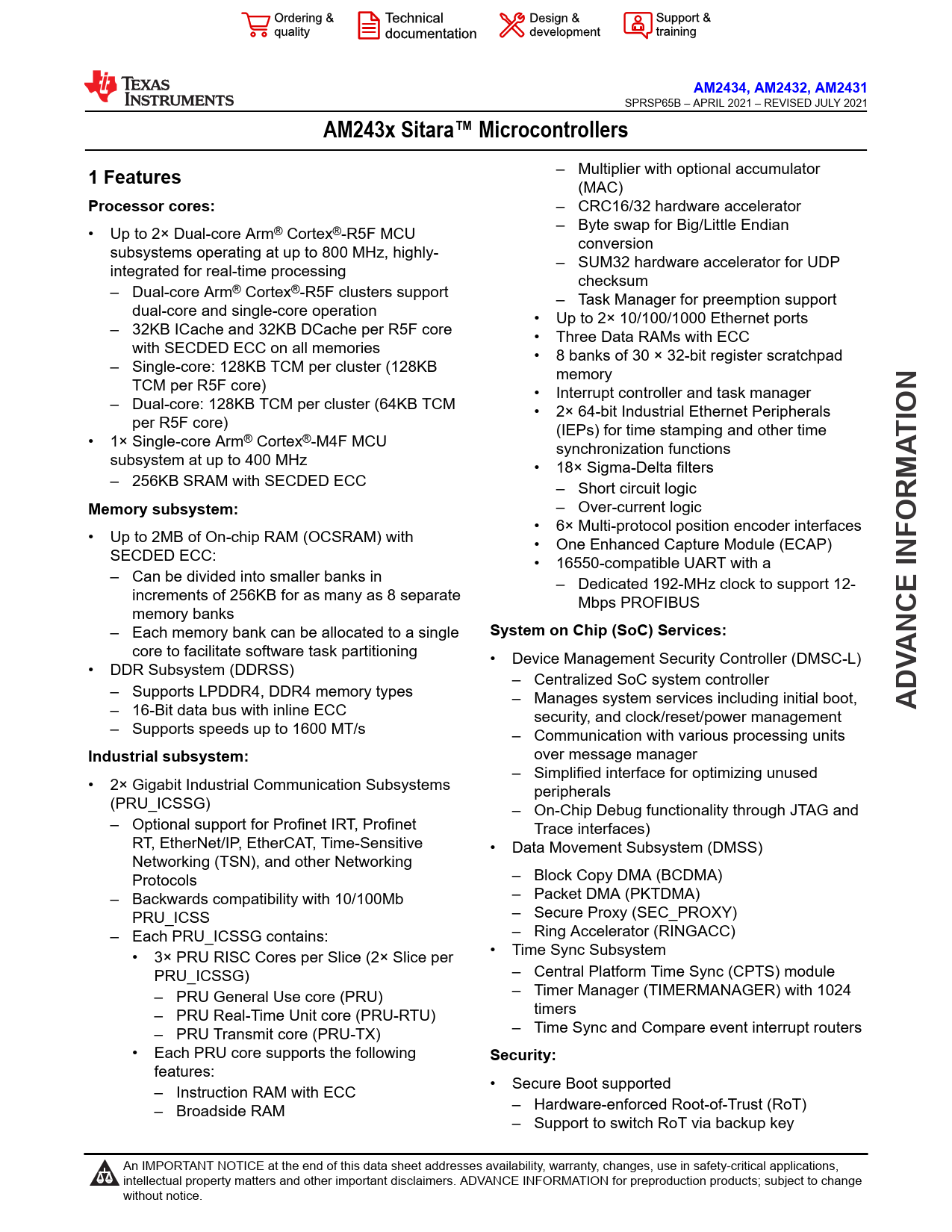

AM243x Sitara™ Microcontrollers 1 Features

– Multiplier with optional accumulator (MAC)

Processor cores:

– CRC16/32 hardware accelerator – Byte swap for Big/Little Endian • Up to 2× Dual-core Arm® Cortex®-R5F MCU conversion subsystems operating at up to 800 MHz, highly- – SUM32 hardware accelerator for UDP integrated for real-time processing checksum – Dual-core Arm® Cortex®-R5F clusters support – Task Manager for preemption support dual-core and single-core operation • Up to 2× 10/100/1000 Ethernet ports – 32KB ICache and 32KB DCache per R5F core • Three Data RAMs with ECC with SECDED ECC on all memories • 8 banks of 30 × 32-bit register scratchpad – Single-core: 128KB TCM per cluster (128KB memory TCM per R5F core) • Interrupt controller and task manager – Dual-core: 128KB TCM per cluster (64KB TCM • 2× 64-bit Industrial Ethernet Peripherals per R5F core) (IEPs) for time stamping and other time

TION

• 1× Single-core Arm® Cortex®-M4F MCU synchronization functions subsystem at up to 400 MHz • 18× Sigma-Delta filters

MA

– 256KB SRAM with SECDED ECC – Short circuit logic

R Memory subsystem:

– Over-current logic • 6× Multi-protocol position encoder interfaces • Up to 2MB of On-chip RAM (OCSRAM) with • One Enhanced Capture Module (ECAP) SECDED ECC: • 16550-compatible UART with a – Can be divided into smaller banks in – Dedicated 192-MHz clock to support 12- increments of 256KB for as many as 8 separate Mbps PROFIBUS memory banks

NCE INFO

– Each memory bank can be allocated to a single

System on Chip (SoC) Services:

core to facilitate software task partitioning

A

• Device Management Security Controller (DMSC-L)

V

• DDR Subsystem (DDRSS) – Centralized SoC system controller – Supports LPDDR4, DDR4 memory types – Manages system services including initial boot,

AD

– 16-Bit data bus with inline ECC security, and clock/reset/power management – Supports speeds up to 1600 MT/s – Communication with various processing units

Industrial subsystem:

over message manager – Simplified interface for optimizing unused • 2× Gigabit Industrial Communication Subsystems peripherals (PRU_ICSSG) – On-Chip Debug functionality through JTAG and – Optional support for Profinet IRT, Profinet Trace interfaces) RT, EtherNet/IP, EtherCAT, Time-Sensitive • Data Movement Subsystem (DMSS) Networking (TSN), and other Networking Protocols – Block Copy DMA (BCDMA) – Backwards compatibility with 10/100Mb – Packet DMA (PKTDMA) PRU_ICSS – Secure Proxy (SEC_PROXY) – Each PRU_ICSSG contains: – Ring Accelerator (RINGACC) • 3× PRU RISC Cores per Slice (2× Slice per • Time Sync Subsystem PRU_ICSSG) – Central Platform Time Sync (CPTS) module – PRU General Use core (PRU) – Timer Manager (TIMERMANAGER) with 1024 – PRU Real-Time Unit core (PRU-RTU) timers – PRU Transmit core (PRU-TX) – Time Sync and Compare event interrupt routers • Each PRU core supports the following

Security:

features: • Secure Boot supported – Instruction RAM with ECC – Broadside RAM – Hardware-enforced Root-of-Trust (RoT) – Support to switch RoT via backup key An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. ADVANCE INFORMATION for preproduction products; subject to change without notice. Document Outline 1 Features 2 Applications 3 Description 3.1 Functional Block Diagram Table of Contents 4 Revision History 5 Device Comparison 5.1 Related Products 6 Terminal Configuration and Functions 6.1 Pin Diagram 6.1.1 AM243x ALV Pin Diagram 6.1.2 AM243x ALX Pin Diagram 6.2 Pin Attributes (ALV Package) 6.3 Pin Attributes (ALX Package) 6.4 Signal Descriptions 6.4.1 ADC MAIN Domain Instances 6.4.1.1 ADC0 Signal Descriptions 6.4.2 DDRSS MAIN Domain Instances 6.4.2.1 DDRSS0 Signal Descriptions 6.4.3 GPIO MAIN Domain Instances 6.4.3.1 GPIO0 Signal Descriptions 6.4.3.2 GPIO1 Signal Descriptions MCU Domain Instances 6.4.3.3 MCU_GPIO0 Signal Descriptions 6.4.4 I2C MAIN Domain Instances 6.4.4.1 I2C0 Signal Descriptions 6.4.4.2 I2C1 Signal Descriptions 6.4.4.3 I2C2 Signal Descriptions 6.4.4.4 I2C3 Signal Descriptions MCU Domain Instances 6.4.4.5 MCU_I2C0 Signal Descriptions 6.4.4.6 MCU_I2C1 Signal Descriptions 6.4.5 MCAN MAIN Domain Instances 6.4.5.1 MCAN0 Signal Descriptions 6.4.5.2 MCAN1 Signal Descriptions 6.4.6 SPI (MCSPI) MAIN Domain Instances 6.4.6.1 MCSPI0 Signal Descriptions 6.4.6.2 MCSPI1 Signal Descriptions 6.4.6.3 MCSPI2 Signal Descriptions 6.4.6.4 MCSPI3 Signal Descriptions 6.4.6.5 MCSPI4 Signal Descriptions MCU Domain Instances 6.4.6.6 MCU_MCSPI0 Signal Descriptions 6.4.6.7 MCU_MCSPI1 Signal Descriptions 6.4.7 UART MAIN Domain Instances 6.4.7.1 UART0 Signal Descriptions 6.4.7.2 UART1 Signal Descriptions 6.4.7.3 UART2 Signal Descriptions 6.4.7.4 UART3 Signal Descriptions 6.4.7.5 UART4 Signal Descriptions 6.4.7.6 UART5 Signal Descriptions 6.4.7.7 UART6 Signal Descriptions MCU Domain Instances 6.4.7.8 MCU_UART0 Signal Descriptions 6.4.7.9 MCU_UART1 Signal Descriptions 6.4.8 MDIO MAIN Domain Instances 6.4.8.1 MDIO0 Signal Descriptions 6.4.9 CPSW MAIN Domain Instances 6.4.9.1 CPSW3G0 Signal Descriptions 6.4.10 ECAP MAIN Domain Instances 6.4.10.1 ECAP0 Signal Descriptions 6.4.10.2 ECAP1 Signal Descriptions 6.4.10.3 ECAP2 Signal Descriptions EQEP MAIN Domain Instances 6.4.11.1 EQEP0 Signal Descriptions 6.4.11.2 EQEP1 Signal Descriptions 6.4.11.3 EQEP2 Signal Descriptions 6.4.11 EPWM MAIN Domain Instances 6.4.11.1 EPWM Signal Descriptions 6.4.11.2 EPWM0 Signal Descriptions 6.4.11.3 EPWM1 Signal Descriptions 6.4.11.4 EPWM2 Signal Descriptions 6.4.11.5 EPWM3 Signal Descriptions 6.4.11.6 EPWM4 Signal Descriptions 6.4.11.7 EPWM5 Signal Descriptions 6.4.11.8 EPWM6 Signal Descriptions 6.4.11.9 EPWM7 Signal Descriptions 6.4.11.10 EPWM8 Signal Descriptions 6.4.12 SERDES MAIN Domain Instances 6.4.12.1 SERDES0 Signal Descriptions 6.4.13 USB MAIN Domain Instances 6.4.13.1 USB0 Signal Descriptions 6.4.14 OSPI MAIN Domain Instances 6.4.14.1 OSPI0 Signal Descriptions 6.4.15 GPMC MAIN Domain Instances 6.4.15.1 GPMC0 Signal Descriptions 6.4.16 MMC MAIN Domain Instances 6.4.16.1 MMC0 Signal Descriptions 6.4.16.2 MMC1 Signal Descriptions 6.4.17 FSITX MAIN Domain Instances 6.4.17.1 FSI0 TX Signal Descriptions 6.4.17.2 FSI1 TX Signal Descriptions 6.4.18 FSIRX MAIN Domain Instances 6.4.18.1 FSI0 RX Signal Descriptions 6.4.18.2 FSI1 RX Signal Descriptions 6.4.18.3 FSI2 RX Signal Descriptions 6.4.18.4 FSI3 RX Signal Descriptions 6.4.18.5 FSI4 RX Signal Descriptions 6.4.18.6 FSI5 RX Signal Descriptions 6.4.19 CPTS MAIN Domain Instances 6.4.19.1 CPTS0 Signal Descriptions 6.4.19.2 CP GEMAC CPTS0 Signal Descriptions 6.4.20 ICSSG MAIN Domain Instances 6.4.20.1 PRU_ICSSG0 Signal Descriptions 6.4.20.2 PRU_ICSSG1 Signal Descriptions 6.4.21 DMTIMER MAIN Domain Instances 6.4.21.1 DMTIMER Signal Descriptions MCU Domain Instances 6.4.21.2 MCU_DMTIMER Signal Descriptions 6.4.22 TRACE MAIN Domain Instances 6.4.22.1 Trace Signal Descriptions 6.4.23 JTAG MAIN Domain Instances 6.4.23.1 JTAG Signal Descriptions 6.4.24 SYSBOOT MAIN Domain Instances 6.4.24.1 Sysboot Signal Descriptions 6.4.25 SYSTEM MAIN Domain Instances 6.4.25.1 System Signal Descriptions MCU Domain Instances 6.4.25.2 MCU System Signal Descriptions 6.4.26 CLOCK MCU Domain Instances 6.4.26.1 MCU Clock Signal Descriptions 6.4.27 VMON 6.4.27.1 VMON Signal Description 6.4.28 Power Supply 6.4.28.1 Power Supply Signal Description 6.5 Pin Multiplexing 6.6 Connections for Unused Pins 7 Specifications 7.1 Absolute Maximum Ratings 7.2 ESD Ratings 7.3 Power-On Hours (POH) 7.4 Recommended Operating Conditions 7.5 Operating Performance Points 7.6 Power Consumption Summary 7.7 Electrical Characteristics 7.7.1 Fail-Safe Reset (FS RESET) Electrical Characteristics 7.7.2 I2C Open-Drain, and Fail-Safe (I2C OD FS) Electrical Characteristics 7.7.3 High-Frequency Oscillator (HFOSC) Electrical Characteristics 7.7.4 eMMCPHY Electrical Characteristics 7.7.5 SDIO Electrical Characteristics 7.7.6 ADC12B Electrical Characteristics 7.7.7 LVCMOS Electrical Characteristics 7.7.8 USB2PHY Electrical Characteristics 7.7.9 DDR Electrical Characteristics 7.8 VPP Specifications for One-Time Programmable (OTP) eFuses 7.8.1 Recommended Operating Conditions for OTP eFuse Programming 7.8.2 Hardware Requirements 7.8.3 Programming Sequence 7.8.4 Impact to Your Hardware Warranty 7.9 Thermal Resistance Characteristics 7.9.1 Thermal Resistance Characteristics 7.10 Timing and Switching Characteristics 7.10.1 Timing Parameters and Information 7.10.2 Power Supply Sequencing 7.10.2.1 Power Supply Slew Rate Requirement 7.10.2.2 Power-Up Sequencing 7.10.2.3 Power-Down Sequencing 7.10.3 System Timing 7.10.3.1 Reset Timing 7.10.3.2 Safety Signal Timing 7.10.3.3 Clock Timing 7.10.4 Clock Specifications 7.10.4.1 Input Clocks / Oscillators 7.10.4.1.1 MCU_OSC0 Internal Oscillator Clock Source 7.10.4.1.1.1 Load Capacitance 7.10.4.1.1.2 Shunt Capacitance 7.10.4.1.2 MCU_OSC0 LVCMOS Digital Clock Source 7.10.4.2 Output Clocks 7.10.4.3 PLLs 7.10.5 Peripherals 7.10.5.1 CPSW3G 7.10.5.1.1 CPSW3G MDIO Timing 7.10.5.1.2 CPSW3G RMII Timing 7.10.5.1.3 CPSW3G RGMII Timing 7.10.5.2 DDRSS 7.10.5.3 ECAP 7.10.5.4 EPWM 7.10.5.5 EQEP 7.10.5.6 FSI 7.10.5.7 GPIO 7.10.5.8 GPMC 7.10.5.8.1 GPMC and NOR Flash — Synchronous Mode 7.10.5.8.2 GPMC and NOR Flash — Asynchronous Mode 7.10.5.8.3 GPMC and NAND Flash — Asynchronous Mode 7.10.5.9 I2C 7.10.5.9.1 Timing Requirements for I2C Input Timings 7.10.5.10 MCAN 7.10.5.11 MCSPI 7.10.5.11.1 MCSPI — Master Mode 7.10.5.11.2 MCSPI — Slave Mode 7.10.5.12 MMCSD 7.10.5.12.1 MMC0 - eMMC Interface 7.10.5.12.1.1 Legacy SDR Mode 7.10.5.12.1.2 High Speed SDR Mode 7.10.5.12.1.3 High Speed DDR Mode 7.10.5.12.1.4 HS200 Mode 7.10.5.12.2 MMC1 - SD/SDIO Interface 7.10.5.12.2.1 Default Speed Mode 7.10.5.12.2.2 High Speed Mode 7.10.5.12.2.3 UHS–I SDR12 Mode 7.10.5.12.2.4 UHS–I SDR25 Mode 7.10.5.12.2.5 UHS–I SDR50 Mode 7.10.5.12.2.6 UHS–I DDR50 Mode 7.10.5.12.2.7 UHS–I SDR104 Mode 7.10.5.13 CPTS 7.10.5.14 OSPI 7.10.5.14.1 OSPI With Data Training 7.10.5.14.1.1 OSPI Switching Characteristics – Data Training 7.10.5.14.2 OSPI Without Data Training 7.10.5.14.2.1 OSPI SDR Timing 7.10.5.14.2.2 OSPI DDR Timing 7.10.5.15 PCIe 7.10.5.16 PRU_ICSSG 7.10.5.16.1 PRU_ICSSG Programmable Real-Time Unit (PRU) 7.10.5.16.1.1 PRU_ICSSG PRU Direct Output Mode Timing 7.10.5.16.1.2 PRU_ICSSG PRU Parallel Capture Mode Timing 7.10.5.16.1.3 PRU_ICSSG PRU Shift Mode Timing 7.10.5.16.1.4 PRU_ICSSG PRU Sigma Delta and Peripheral Interface 7.10.5.16.1.4.1 PRU_ICSSG PRU Sigma Delta and Peripheral Interface Timing 7.10.5.16.2 PRU_ICSSG Pulse Width Modulation (PWM) 7.10.5.16.2.1 PRU_ICSSG PWM Timing 7.10.5.16.3 PRU_ICSSG Industrial Ethernet Peripheral (IEP) 7.10.5.16.3.1 PRU_ICSSG IEP Timing 7.10.5.16.4 PRU_ICSSG Universal Asynchronous Receiver Transmitter (UART) 7.10.5.16.4.1 PRU_ICSSG UART Timing 7.10.5.16.5 PRU_ICSSG Enhanced Capture Peripheral (ECAP) 7.10.5.16.5.1 PRU_ICSSG ECAP Timing 7.10.5.16.6 PRU_ICSSG RGMII, MII_RT, and Switch 7.10.5.16.6.1 PRU_ICSSG MDIO Timing 7.10.5.16.6.2 PRU_ICSSG MII Timing 7.10.5.16.6.3 PRU_ICSSG RGMII Timing 7.10.5.17 Timers 7.10.5.18 UART 7.10.5.19 USB 7.10.6 Emulation and Debug 7.10.6.1 Trace 7.10.6.2 JTAG 8 Detailed Description 8.1 Overview 8.2 Processor Subsystems 8.2.1 Arm Cortex-R5F Subsystem (R5FSS) 8.2.2 Arm Cortex-M4F (M4FSS) 8.3 Accelerators and Coprocessors 8.3.1 Programmable Real-Time Unit Subsystem and Industrial Communication Subsystem (PRU_ICSSG) 8.4 Other Subsystems 8.4.1 PDMA Controller 8.4.2 Peripherals 8.4.2.1 ADC 8.4.2.2 DCC 8.4.2.3 Dual Date Rate (DDR) External Memory Interface (DDRSS) 8.4.2.4 ECAP 8.4.2.5 EPWM 8.4.2.6 ELM 8.4.2.7 ESM 8.4.2.8 GPIO 8.4.2.9 EQEP 8.4.2.10 GPMC 8.4.2.11 I2C 8.4.2.12 MCAN 8.4.2.13 MCRC Controller 8.4.2.14 MCSPI 8.4.2.15 MMCSD 8.4.2.16 OSPI 8.4.2.17 Peripheral Component Interconnect Express (PCIe) 8.4.2.18 Serializer/Deserializer (SerDes) 8.4.2.19 RTI 8.4.2.20 DMTIMER 8.4.2.21 UART 8.4.2.22 Universal Serial Bus Subsystem(USBSS) 9 Applications, Implementation, and Layout 9.1 Power Supply Mapping 9.2 Device Connection and Layout Fundamentals 9.2.1 Power Supply Decoupling and Bulk Capacitors 9.2.1.1 Power Distribution Network Implementation Guidance 9.2.2 External Oscillator 9.2.3 JTAG and EMU 9.2.4 Unused Pins 9.3 Peripheral- and Interface-Specific Design Information 9.3.1 General Routing Guidelines 9.3.2 DDR Board Design and Layout Guidelines 9.3.3 OSPI and QSPI Board Design and Layout Guidelines 9.3.3.1 No Loopback and Internal Pad Loopback 9.3.3.2 External Board Loopback 9.3.3.3 DQS (only available in Octal Flash devices) 9.3.4 USB VBUS Design Guidelines 9.3.5 System Power Supply Monitor Design Guidelines 9.3.6 High Speed Differential Signal Routing Guidance 9.3.7 Thermal Solution Guidance 10 Device and Documentation Support 10.1 Device Nomenclature 10.1.1 Standard Package Symbolization 10.1.2 Device Naming Convention 10.2 Tools and Software 10.3 Documentation Support 10.4 Support Resources 10.5 Trademarks 10.6 Electrostatic Discharge Caution 10.7 Glossary 11 Mechanical, Packaging, and Orderable Information 11.1 Packaging Information