Datasheet ADIN1100 (Analog Devices) - 3

| Производитель | Analog Devices |

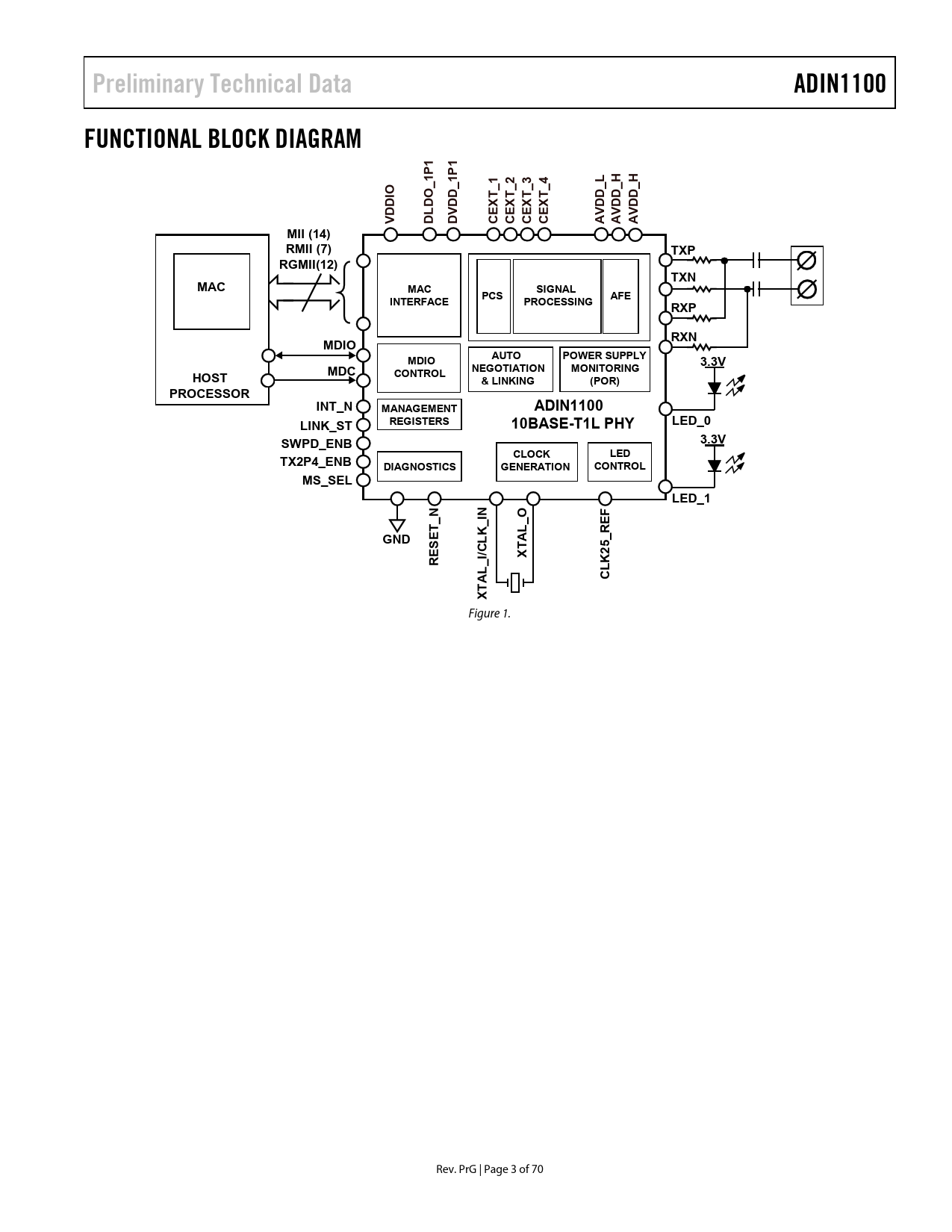

| Описание | Robust, Industrial, Low Power 10BASE-T1L Ethernet PHY |

| Страниц / Страница | 70 / 3 — Preliminary Technical Data. ADIN1100. FUNCTIONAL BLOCK DIAGRAM. _1P DO. … |

| Версия | PrG |

| Формат / Размер файла | PDF / 1.1 Мб |

| Язык документа | английский |

Preliminary Technical Data. ADIN1100. FUNCTIONAL BLOCK DIAGRAM. _1P DO. DD_1P. XT_1 XT_2 XT_3 XT_4. DD_L DD_H DD_H. VDDI. CE CE CE CE

Модельный ряд для этого даташита

Текстовая версия документа

Preliminary Technical Data ADIN1100 FUNCTIONAL BLOCK DIAGRAM 1 1 O _1P DO DD_1P XT_1 XT_2 XT_3 XT_4 DD_L DD_H DD_H VDDI DL DV CE CE CE CE AV AV AV MII (14) RMII (7) TXP RGMII(12) TXN MAC MAC INTERFACE PCS SIGNAL PROCESSING AFE RXP MDIO RXN MDIO AUTO POWER SUPPLY NEGOTIATION MONITORING 3.3V HOST MDC CONTROL & LINKING (POR) PROCESSOR INT_N MANAGEMENT ADIN1100 REGISTERS LINK_ST 10BASE-T1L PHY LED_0 SWPD_ENB 3.3V CLOCK LED TX2P4_ENB DIAGNOSTICS GENERATION CONTROL MS_SEL LED_1 _N F _IN _O GND LK RESET I/C XTAL K25_RE L_ CL XTA

Figure 1. Rev. PrG | Page 3 of 70 Document Outline Features Applications General Description Functional Block Diagram Specifications Timing Characteristics Power-Up Timing Management Interface Timing Absolute Maximum Ratings Thermal Resistance ESD Caution Pin Configuration and Function Descriptions Theory of Operation Power Supply Domains MAC Interface MII Interface Mode RMII Interface Mode RGMII Interface Mode Auto-Negotiation Transmit Amplitude Resolution Master/Slave Resolution Management Interface Interrupt (INT_N) MDI Interface Reset Operation Power-On Reset Hardware Reset Software Reset PHY Subsystem Reset MAC Interface Reset Status LEDs LED Function Link Status Pin Powerdown Modes Hardware Powerdown Mode Software Powerdown Mode Hardware Configuration Pins Hardware Configuration Pin Functions PHY Address Configuration Software Powerdown after Reset Master/Slave Preference Transmit Amplitude MAC Interface Selection Media Convertor Bringing Up 10BASE-T1L Links Unmanaged PHY Operation Managed PHY Operation Power-up and Reset Complete Configuring the Part for Linking Advertisement of Transmit Level Operating Mode Advertisement of Master/Slave Successful Completion of Auto-Negotiation Link Status On-Chip Diagnostics Loopback Modes PMA Loopback PCS Loopback MAC Interface Loopback MAC Interface Remote Loopback External MII/RMII Loopback Frame Generator and Checker Frame Generator and Checker used with Remote Loopback with Two PHYs Test Modes Accessing the test modes Applications Information System Level Power Management Transmit Level = 1.0 V pk-pk Transmit Level = 2.4 V pk-pk Component Recommendations Crystal External Clock Input Register Summary Clause 22 Clause 45 Recommended Register Operation Latch Low Registers IEEE Duplicated Registers Read Modify Write Operation Clause 22 Register Details MII Control Register MII Status Register PHY Identifier 1 Register PHY Identifier 2 Register MMD Access Control Register MMD Access Register Clause 45 Register Details PMA/PMD Control 1 Register PMA/PMD Status 1 Register PMA/PMD MMD Devices in Package 1 Register PMA/PMD MMD Devices in Package 2 Register PMA/PMD Control 2 Register PMA/PMD Status 2 Register PMA/PMD Transmit Disable Register PMA/PMD Extended Abilities Register BASE-T1 PMA/PMD Extended Ability Register BASE-T1 PMA/PMD Control Register 10BASE-T1L PMA Control Register 10BASE-T1L PMA Status Register 10BASE-T1L Test Mode Control Register Frequency Offset Saturation Threshold for CR Stability Check Register Slave IIR Filter Change Echo Acquisition Clock Recovery Proportional Gain Register 10BASE-T1L PMA Link Status Register MSE Value Register PCS Control 1 Register PCS Status 1 Register PCS MMD Devices in Package 1 Register PCS MMD Devices in Package 2 Register PCS Status 2 Register 10BASE-T1L PCS Control Register 10BASE-T1L PCS Status Register AUTO-_NEGOTIATION MMD Devices in Package 1 Register AUTO-_NEGOTIATION MMD Devices in Package 2 Register BASE-T1 Autonegotiation Control Register BASE-T1 Autonegotiation Status Register BASE-T1 Autonegotiation Advertisement [15:0] Register BASE-T1 Autonegotiation Advertisement [31:16] Register BASE-T1 Autonegotiation Advertisement [47:32] Register BASE-T1 Autonegotiation Link Partner Base Page Ability [15:0] Register BASE-T1 Autonegotiation Link Partner Base Page Ability [31:16] Register BASE-T1 Autonegotiation Link Partner Base Page Ability [47:32] Register BASE-T1 Autonegotiation Next Page Transmit [15:0] Register BASE-T1 Autonegotiation Next Page Transmit [31:16] Register BASE-T1 Autonegotiation Next Page Transmit [47:32] Register BASE-T1 Autonegotiation Link Partner Next Page Ability [15:0] Register BASE-T1 Autonegotiation Link Partner Next Page Ability [31:16] Register BASE-T1 Autonegotiation Link Partner Next Page Ability [47:32] Register 10BASE-T1 Autonegotiation Control Register 10BASE-T1 Autonegotiation Status Register Extra Autonegotiation Status Register PHY Instantaneous Status Register Vendor Specific MMD 1 Device Identifier High Register Vendor Specific MMD 1 Device Identifier Low Register Vendor Specific 1 MMD Devices in Package Register Vendor Specific 1 MMD Devices in Package Register Vendor Specific MMD 1 Status Register System Interrupt Status Register System Interrupt Mask Register Software Reset Register Software Power-down Control Register PHY Subsystem Reset Register PHY MAC Interface Reset Register System Status Register CRSM Power Management Control Register MAC Interface Configuration Register CRSM Diagnostics Clock Control Register Package Configuration Values Register MDIO Control Register Pinmux Configuration 1 Register Pinmux Configuration 2 Register LED 0 ON/_OFF Blink Time Register LED 1 ON/_OFF Blink Time Register LED Control Register LED Polarity Register Vendor Specific MMD 2 Device Identifier High Register Vendor Specific MMD 2 Device Identifier Low Register Vendor Specific 2 MMD Devices in Package Register Vendor Specific 2 MMD Devices in Package Register Vendor Specific MMD 2 Status Register PHY Subsystem Interrupt Status Register PHY Subsystem Interrupt Mask Register Frame Checker Enable Register Frame Checker Interrupt Enable Register Frame Checker Transmit Select Register Receive Error Count Register Frame Checker Count High Register Frame Checker Count Low Register Frame Checker Length Error Count Register Frame Checker Alignment Error Count Register Frame Checker Symbol Error Count Register Frame Checker Oversized Frame Count Register Frame Checker Undersized Frame Count Register Frame Checker Odd Nibble Frame Count Register Frame Checker Odd Preamble Packet Count Register Frame Checker False Carrier Count Register Frame Generator Enable Register Frame Generator CONTROL/_RESTART Register Frame Generator Continuous Mode Enable Register Frame Generator Interrupt Enable Register Frame Generator Frame Length Register Frame Generator Number of Frames High Register Frame Generator Number of Frames Low Register Frame Generator Done Register RMII Configuration Register MAC Interface Loopbacks Configuration Register MAC Start Of Packet (SOP) Generation Control Register PCB Layout Recommendations PHY Package Layout Component Placement Crystal Placement and Routing Outline Dimensions

Купить ADIN1100CCPZ-R7 на РадиоЛоцман.Цены — от 817 до 9 938 ₽

Купить ADIN1100CCPZ-R7 на РадиоЛоцман.Цены — от 817 до 9 938 ₽