Datasheet PIC18(L)F25/26K83 (Microchip) - 861

| Производитель | Microchip |

| Описание | 28-Pin, Low-Power, High-Performance Microcontrollers with CAN Technology |

| Страниц / Страница | 870 / 861 — PIC18(L)F25/26K83 |

| Формат / Размер файла | PDF / 8.5 Мб |

| Язык документа | английский |

PIC18(L)F25/26K83

Модельный ряд для этого даташита

Текстовая версия документа

PIC18(L)F25/26K83

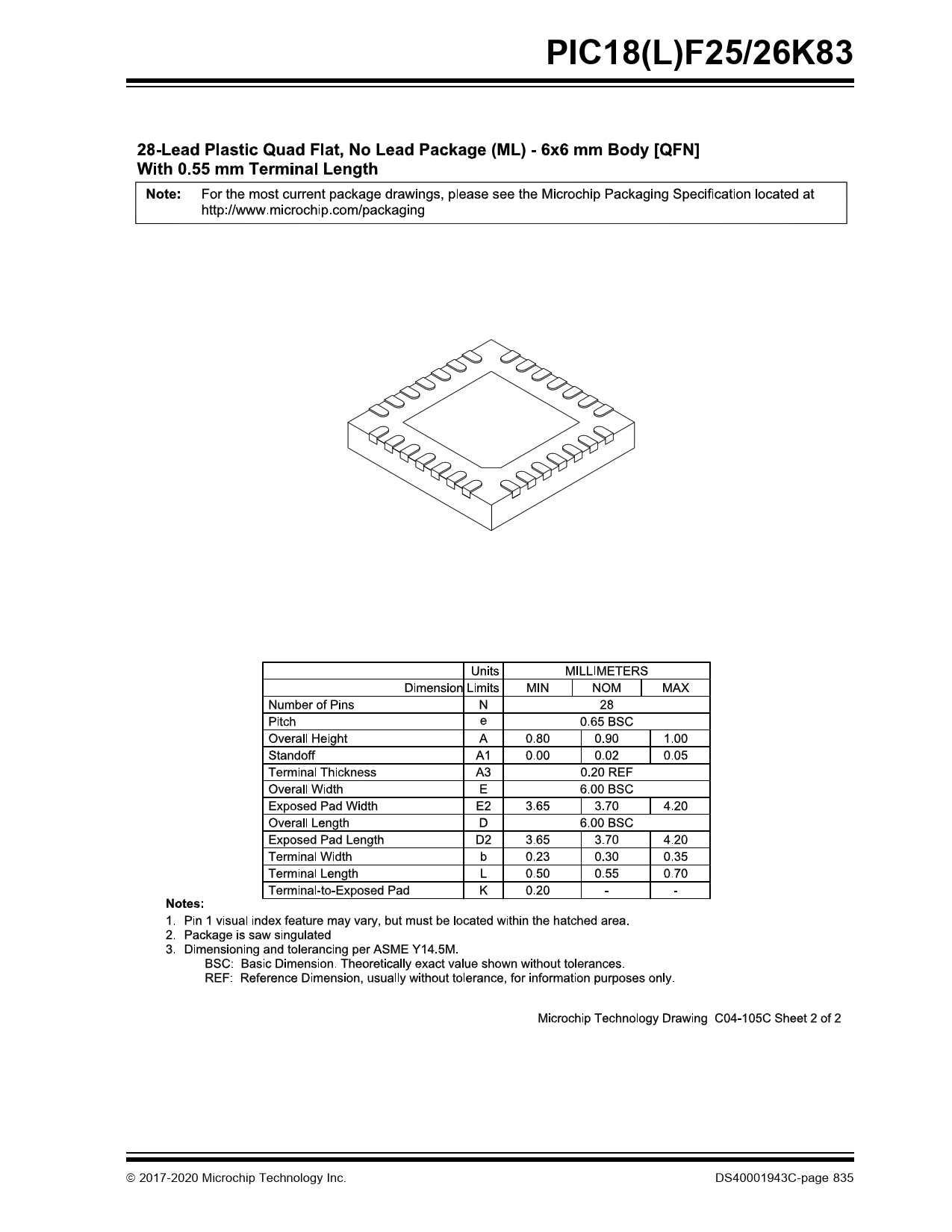

2017-2020 Microchip Technology Inc. DS40001943C-page 835 Document Outline Description Core Features Memory Operating Characteristics Power-Saving Functionality eXtreme Low-Power (XLP) Features Digital Peripherals Analog Peripherals Flexible Oscillator Structure Pin Diagrams Pin Allocation Tables Table of Contents Most Current Data Sheet Errata Customer Notification System 1.0 Device Overview 1.1 New Features 1.2 Details on Individual Family Members TABLE 1-1: Device Features 1.3 Register and Bit naming conventions 1.3.1 Register Names 1.3.2 Bit Names 1.3.2.1 Short Bit Names 1.3.2.2 Long Bit Names 1.3.2.3 Bit Fields 1.3.3 Register and Bit Naming Exceptions 1.3.3.1 Status, Interrupt, and Mirror Bits 2.0 Guidelines for Getting Started with PIC18(L)F25/ 26K83 Microcontrollers 2.1 Basic Connection Requirements FIGURE 2-1: Recommended Minimum Connections 2.2 Power Supply Pins 2.2.1 Decoupling Capacitors 2.2.2 Tank Capacitors 2.3 Master Clear (MCLR) Pin FIGURE 2-2: Example of MCLR Pin Connections 2.4 ICSP™ Pins 2.5 External Oscillator Pins 2.6 Unused I/Os FIGURE 2-3: Suggested Placement of the Oscillator Circuit 3.0 PIC18 CPU FIGURE 3-1: PIC18(L)F25/26K83 Family Block Diagram 3.1 System Arbitration TABLE 3-1: Default Priorities 3.1.1 Priority Lock EXAMPLE 3-1: Priority Lock Sequence EXAMPLE 3-2: Priority Unlock Sequence 3.2 Memory Access Scheme 3.2.1 ISR Priority > MAIN Priority > Peripheral Priority 3.2.2 Peripheral Priority > ISR Priority > MAIN Priority 3.2.3 ISR Priority > Peripheral Priority > MAIN Priority 3.2.4 Peripheral 1 Priority > ISR Priority > MAIN Priority > Peripheral 2 Priority Register 3-1: ISRPR: Interrupt Service Routine Priority Register Register 3-2: MAINPR: Main Routine Priority Register Register 3-3: DMA1PR: DMA1 Priority Register Register 3-4: DMA2PR: DMA2 Priority Register Register 3-5: SCANPR: Scanner Priority Register Register 3-6: PRLOCK: Priority Lock Register TABLE 3-2: Summary of Registers Associated with CPU 4.0 Memory Organization 4.1 Program Flash Memory Organization 4.2 Memory Access Partition (MAP) 4.2.1 Application Block 4.2.2 Boot Block 4.2.3 Storage Area Flash TABLE 4-1: Program and Data EEPROM Memory Map TABLE 4-2: Program Flash Memory Partition 4.2.4 Program Counter 4.2.5 Return Address Stack 4.2.5.1 Top-of-Stack Access FIGURE 4-1: Return Address Stack and Associated Registers 4.2.5.2 Return Stack Pointer (STKPTR) 4.2.5.3 PUSH and POP Instructions 4.3 Register Definitions: Stack Pointer Register 4-1: TOSU: Top-of-Stack Upper Byte Register 4-2: TOSH: Top-of-Stack High Byte Register 4-3: TOSL: Top-of-Stack Low Byte Register 4-4: STKPTR: Stack Pointer Register 4.3.1 Fast Register Stack EXAMPLE 4-1: Fast Register Stack Code Example 4.3.2 Look-up Tables in Program Memory 4.3.2.1 Computed GOTO EXAMPLE 4-2: Computed GOTO Using an Offset Value 4.3.2.2 Table Reads and Table Writes 4.4 PIC18 Instruction Cycle 4.4.1 Clocking Scheme 4.4.2 Instruction Flow/Pipelining FIGURE 4-2: Clock/ Instruction Cycle EXAMPLE 4-3: Instruction Pipeline Flow 4.4.3 Instructions in Program Memory 4.4.4 Multi-Word Instructions FIGURE 4-3: Instructions in Program Memory EXAMPLE 4-4: Two-Word Instructions EXAMPLE 4-5: Three-Word Instructions 4.5 Data Memory Organization 4.5.1 Bank Select Register (BSR) FIGURE 4-5: Use of the Bank Select Register (Direct Addressing) 4.5.2 General Purpose Register File 4.5.3 Special Function Registers 4.5.4 Access Bank TABLE 4-3: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 63 TABLE 4-4: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 62 TABLE 4-5: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 61 TABLE 4-6: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 60 TABLE 4-7: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 59 TABLE 4-8: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 58 TABLE 4-9: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 57 TABLE 4-10: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 56 TABLE 4-11: Special Function Register Map for PIC18(L)F25/26K83 Devices Bank 55 4.5.5 Status Register 4.5.6 Call Shadow Register 4.6 Register Definitions: Status Registers Register 4-2: STATUS: Status Register 4.7 Data Addressing Modes 4.7.1 Inherent and Literal Addressing 4.7.2 Direct Addressing 4.7.3 Indirect Addressing EXAMPLE 4-6: How to Clear RAM (Bank 1) Using Indirect Addressing 4.7.3.1 FSR Registers and the INDF Operand 4.7.3.2 FSR Registers, POSTINC, POSTDEC, PREINC and PLUSW FIGURE 4-6: Indirect Addressing 4.7.3.3 Operations by FSRs on FSRs 4.8 Data Memory and the Extended Instruction Set 4.8.1 Indexed Addressing with Literal Offset 4.8.2 Instructions Affected by Indexed Literal Offset Mode FIGURE 4-7: Comparing Addressing Options for Bit-Oriented and Byte-Oriented Instructions (Extended Instruction Set Enabled) 4.8.3 Mapping the Access Bank in Indexed Literal Offset Mode 4.9 PIC18 Instruction Execution and the Extended Instruction Set FIGURE 4-8: Remapping the Access Bank with Indexed Literal Offset Addressing 5.0 Device Configuration 5.1 Configuration Words 5.2 Register Definitions: Configuration Words Register 5-1: Configuration Word 1L (30 0000h) Register 5-2: Configuration Word 1H (30 0001h) Register 5-3: Configuration Word 2L (30 0002h) Register 5-4: Configuration Word 2H (30 0003h) Register 5-5: Configuration Word 3L (30 0004h) Register 5-6: Configuration Word 3H (30 0005h) Register 5-7: Configuration Word 4L (30 0006h) TABLE 5-1: Boot Block Size Bits Register 5-8: Configuration Word 4H (30 0007h) Register 5-9: Configuration Word 5L (30 0008h) Register 5-10: Configuration Word 5H (30 0009h) TABLE 5-2: Summary of Configuration Words 5.3 Code Protection 5.4 User ID 5.5 Device ID and Revision ID 5.6 Register Definitions: Device ID and Revision ID Register 5-11: DEVICE ID: Device ID Register Register 5-12: REVISION ID: Revision ID Register 5.7 Device Information Area TABLE 5-3: Device Information Area 5.7.1 Microchip Unique identifier (MUI) 5.7.2 External Unique Identifier (EUI) 5.7.3 Analog-to-Digital Conversion Data of the Temperature Sensor 5.7.4 Fixed Voltage Reference Data 5.8 Device Configuration Information TABLE 5-4: Device Configuration Information for PIC18(L)F25/26K83 6.0 Resets FIGURE 6-1: Simplified Block Diagram of On-Chip Reset Circuit FIGURE 6-2: LPBOR, BOR, POR Relationship 6.1 Power-on Reset (POR) 6.2 Brown-out Reset (BOR) 6.2.1 BOR is Always On 6.2.2 BOR is Off in Sleep 6.2.3 BOR Controlled by Software 6.2.4 BOR and Bulk Erase TABLE 6-1: BOR Operating Modes FIGURE 6-3: Brown-out Situations 6.3 Register Definitions: BOR Control Register 6-1: BORCON: Brown-out Reset Control Register 6.4 Low-Power Brown-out Reset (LPBOR) 6.4.1 Enabling LPBOR 6.4.1.1 LPBOR Module Output 6.5 MCLR TABLE 6-2: MCLR Configuration 6.5.1 MCLR Enabled 6.5.2 MCLR Disabled 6.6 Windowed Watchdog Timer (WWDT) Reset 6.7 RESET Instruction 6.8 Stack Overflow/Underflow Reset 6.9 Programming Mode Exit 6.10 Power-up Timer (PWRT) 6.11 Start-up Sequence FIGURE 6-4: Reset Start-up Sequence 6.11.1 Memory Execution Violation 6.12 Determining the Cause of a Reset TABLE 6-3: Reset Condition for Special Registers 6.13 Power Control (PCON0/PCON1) Register 6.14 Register Definitions: Power Control Register 6-2: PCON0: Power Control Register 0 Register 6-3: PCON1: Power Control Register 1 TABLE 6-4: Summary of Registers Associated with Resets 7.0 Oscillator Module (with Fail-Safe Clock Monitor) 7.1 Overview FIGURE 7-1: Simplified PIC® MCU Clock Source Block Diagram 7.2 Clock Source Types 7.2.1 External Clock Sources 7.2.1.1 EC Mode FIGURE 7-2: External Clock (EC) Mode Operation 7.2.1.2 LP, XT, HS Modes FIGURE 7-3: Quartz Crystal Operation (LP, XT or HS Mode) FIGURE 7-4: Ceramic Resonator Operation (XT or HS Mode) 7.2.1.3 Oscillator Start-up Timer (OST) 7.2.1.4 4x PLL 7.2.1.5 Secondary Oscillator FIGURE 7-5: Quartz Crystal Operation (Secondary Oscillator) 7.2.2 Internal Clock Sources 7.2.2.1 HFINTOSC 7.2.2.2 MFINTOSC 7.2.2.3 Internal Oscillator Frequency Adjustment 7.2.2.4 LFINTOSC 7.2.2.5 ADCRC 7.2.2.6 Oscillator Status and Manual Enable 7.2.2.7 HFOR and MFOR Bits 7.3 Clock Switching 7.3.1 New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) Bits 7.3.2 Clock Switch and Sleep FIGURE 7-6: Clock Switch (CSWHOLD = 0) FIGURE 7-7: Clock Switch (CSWHOLD = 1) FIGURE 7-8: Clock Switch Abandoned 7.4 Fail-Safe Clock Monitor FIGURE 7-9: FSCM Block Diagram 7.4.1 Fail-Safe Detection 7.4.2 Fail-Safe Operation 7.4.3 Fail-Safe Condition Clearing 7.4.4 Reset or Wake-up from Sleep FIGURE 7-10: FSCM Timing Diagram TABLE 7-1: NOSC/COSC and NDIV/CDIV Bit Settings 7.5 Register Definitions: Oscillator Control Register 7-1: OSCCON1: Oscillator Control Register 1 TABLE 7-2: Default Oscillator Settings Register 7-2: OSCCON2: Oscillator Control Register 2 Register 7-3: OSCCON3: Oscillator Control Register 3 Register 7-4: OSCSTAT: Oscillator Status Register 1 Register 7-5: OSCFRQ: HFINTOSC Frequency Selection Register Register 7-6: OSCTUNE: HFINTOSC Tuning Register Register 7-7: OSCEN: Oscillator Manual Enable Register TABLE 7-3: Summary of Registers Associated with Clock Sources 8.0 Reference Clock Output Module FIGURE 8-1: Clock Reference Block Diagram FIGURE 8-2: Clock Reference Timing 8.1 Clock Source 8.1.1 Clock Synchronization 8.2 Programmable Clock Divider 8.3 Selectable Duty Cycle 8.4 Operation in Sleep Mode 8.5 Register Definitions: Reference Clock Register 8-1: CLKRCON: Reference Clock Control Register Register 8-2: CLKRCLK: Clock Reference Clock Selection MUX TABLE 8-1: Summary of Registers Associated with Clock Reference Output 9.0 Interrupt Controller 9.1 Interrupt Control and Status Registers 9.2 Interrupt Vector Table (IVT) 9.2.1 Interrupt Vector Table base address (IVTBASE) 9.2.2 Interrupt Vector Table Contents 9.2.3 Interrupt Vector Table (IVT) address calculation TABLE 9-1: IVT Address Calculation Summary 9.2.4 Access control for IVTBASE registers EXAMPLE 9-1: IVT Unlock Sequence EXAMPLE 9-2: IVT lock Sequence 9.3 Interrupt Priority 9.3.1 User (Software) priority 9.3.2 Natural Order (Hardware) Priority TABLE 9-2: Interrupt Vector Priority Table 9.4 Interrupt Operation FIGURE 9-1: Vectored Interrupts State Transition Diagram 9.4.1 Serving a high or low priority interrupt when main routine code is executing FIGURE 9-2: Interrupt Execution: High/Low Priority Interrupt When Executing Main Routine 9.4.2 Serving a high priority interrupt While a low priority interrupt pending FIGURE 9-3: Interrupt Execution: High Priority Interrupt with a Low Priority Interrupt Pending 9.4.3 Preempting Low Priority Interrupts FIGURE 9-4: Interrupt Execution: High Priority Interrupt Preempting Low Priority Interrupts 9.4.4 Simultaneous Low and High Priority Interrupts FIGURE 9-5: Interrupt Execution: Simultaneous Low and High Priority Interrupts 9.5 Context Saving 9.5.1 Accessing Shadow Registers FIGURE 9-6: Context Save State Machine Diagram 9.6 Returning from Interrupt Service Routine (ISR) 9.7 Interrupt Latency FIGURE 9-7: Interrupt Timing Diagram – One Cycle Instruction FIGURE 9-8: Interrupt Timing Diagram – Two Word Instruction FIGURE 9-9: Interrupt Timing Diagram – Three Cycle Instruction 9.7.1 Aborting Interrupts FIGURE 9-10: Interrupt Timing Diagram - Aborting Interrupts 9.8 Interrupt Setup Procedure 9.9 External Interrupt Pins 9.10 Wake-up from Sleep 9.11 Interrupt Compatibility EXAMPLE 9-3: Setting Up Vectored Interrupts Using MPASM EXAMPLE 9-4: Setting Up Vectored Interrupts Using XC8 9.12 Register Definitions: Interrupt Control Register 9-1: INTCON0: Interrupt Control Register 0 Register 9-2: INTCON1: Interrupt Control Register 1 Register 9-3: PIR0: Peripheral Interrupt Request Register 0 Register 9-4: PIR1: Peripheral Interrupt Request Register 1 Register 9-5: PIR2: Peripheral Interrupt Register 2(1) Register 9-6: PIR3: Peripheral Interrupt Register 3(1) Register 9-7: PIR4: Peripheral Interrupt Register 4(1) Register 9-8: PIR5: Peripheral Interrupt Register 5(1) Register 9-9: PIR6: Peripheral Interrupt Register 6(1) Register 9-10: PIR7: Peripheral Interrupt Register 7(1) Register 9-11: PIR8: Peripheral Interrupt Register 8(1) Register 9-12: PIR9: Peripheral Interrupt Register 9(1) Register 9-13: PIE0: Peripheral Interrupt Enable Register 0 Register 9-14: PIE1: Peripheral Interrupt Enable Register 1 Register 9-15: PIE2: Peripheral Interrupt Enable Register 2 Register 9-16: PIE3: Peripheral Interrupt Enable Register 3 Register 9-17: PIE4: Peripheral Interrupt Enable Register 4 Register 9-18: PIE5: Peripheral Interrupt Enable Register 5 Register 9-19: PIE6: Peripheral Interrupt Enable Register 6 Register 9-20: PIE7: Peripheral Interrupt Enable Register 7 Register 9-21: PIE8: Peripheral Interrupt Enable Register 8 Register 9-22: PIE9: Peripheral Interrupt Enable Register 9 Register 9-23: IPR0: Peripheral Interrupt Priority Register 0 Register 9-24: IPR1: Peripheral Interrupt Priority Register 1 Register 9-25: IPR2: Peripheral Interrupt Priority Register 2 Register 9-26: IPR3: Peripheral Interrupt Priority Register 3 Register 9-27: IPR4: Peripheral Interrupt Priority Register 4 Register 9-28: IPR5: Peripheral Interrupt Priority Register 5 Register 9-29: IPR6: Peripheral Interrupt Priority Register 6 Register 9-30: IPR7: Peripheral Interrupt Priority Register 7 Register 9-31: IPR8: Peripheral Interrupt Priority Register 8 Register 9-32: IPR9: Peripheral Interrupt Priority Register 9 Register 9-33: IVTBASEU: Interrupt Vector Table Base Address Upper Register Register 9-34: IVTBASEH: Interrupt Vector Table Base Address High Register Register 9-35: IVTBASEL: Interrupt Vector Table Base Address Low Register Register 9-36: IVTADU: Interrupt Vector Table Address Upper Register Register 9-37: IVTADH: Interrupt Vector Table Address High Register Register 9-38: IVTADL: Interrupt Vector Table Address Low Register Register 9-39: IVTLOCK: Interrupt Vector Table Lock Register Register 9-40: SHADCON: Shadow Control Register TABLE 9-3: Summary of Registers Associated with Interrupts 10.0 Power-Saving Operation Modes 10.1 Doze Mode 10.1.1 Doze Operation FIGURE 10-1: Doze Mode Operation Example (DOZE<2:0> = 001, 1:4) 10.1.2 Interrupts During Doze EXAMPLE 10-1: Doze Software Example 10.2 Sleep Mode 10.2.1 Wake-up from Sleep 10.2.2 Wake-up Using Interrupts FIGURE 10-2: Wake-Up from Sleep through Interrupt 10.2.3 Low-Power Sleep Mode 10.2.3.1 Sleep Current vs. Wake-up Time 10.2.3.2 Peripheral Usage in Sleep 10.2.4 Idle Mode 10.2.4.1 Idle and Interrupts 10.2.4.2 Idle and WWDT 10.3 Peripheral Operation in Power Saving Modes 10.4 Register Definitions: Voltage Regulator Control Register 10-1: VREGCON: Voltage Regulator Control Register(1) Register 10-2: CPUDOZE: Doze and Idle Register TABLE 10-1: Summary of Registers Associated with Power-down Mode 11.0 Windowed Watchdog Timer (WWDT) FIGURE 11-1: Windowed Watchdog Timer Block Diagram 11.1 Independent Clock Source 11.2 WWDT Operating Modes 11.2.1 WWDT Is Always On 11.2.2 WWDT Is Off in Sleep 11.2.3 WWDT Controlled by Software TABLE 11-1: WWDT Operating Modes 11.3 Time-out Period 11.4 Watchdog Window 11.5 Clearing the WWDT 11.5.1 CLRWDT Considerations (Windowed Mode) 11.6 Operation During Sleep TABLE 11-2: WWDT Clearing Conditions FIGURE 11-2: Window Period and Delay 11.7 Register Definitions: Windowed Watchdog Timer Control Register 11-1: WDTCON0: Watchdog Timer Control Register 0 Register 11-2: WDTCON1: Watchdog Timer Control Register 1 Register 11-3: WDTPSL: WWDT Prescale Select Low Byte Register (Read-Only) Register 11-4: WDTPSH: WWDT Prescale Select High Byte Register (Read-Only) Register 11-5: WDTTMR: WDT Timer Register (Read-Only) TABLE 11-3: Summary of Registers Associated with Windowed Watchdog Timer 12.0 8x8 Hardware Multiplier 12.1 Introduction 12.2 Operation EXAMPLE 12-1: 8x8 Unsigned Multiply Routine EXAMPLE 12-2: 8x8 Signed Multiply Routine TABLE 12-1: Performance Comparison for Various Multiply Operations EQUATION 12-1: 16 x 16 Unsigned Multiplication Algorithm EXAMPLE 12-3: 16 x 16 Unsigned Multiply Routine EQUATION 12-2: 16 x 16 Signed Multiplication Algorithm EXAMPLE 12-4: 16 x 16 Signed Multiply Routine 13.0 Nonvolatile Memory (NVM) Control TABLE 13-1: NVM Organization and Access Information 13.1 Program Flash Memory TABLE 13-2: Flash Memory Organization by Device 13.1.1 Table Reads and Table Writes FIGURE 13-1: Table Read Operation FIGURE 13-2: Table Write Operation 13.1.2 Control Registers 13.1.2.1 NVMCON1 and NVMCON2 Registers 13.1.2.2 TABLAT – Table Latch Register 13.1.2.3 TBLPTR – Table Pointer Register 13.1.2.4 Table Pointer Boundaries TABLE 13-3: Table Pointer Operations with TBLRD and TBLWT Instructions FIGURE 13-3: Table Pointer Boundaries Based on Operation 13.1.3 Reading the Program Flash Memory FIGURE 13-4: Reads from Program Flash Memory EXAMPLE 13-1: Reading a Program Flash Memory Word FIGURE 13-5: Program Flash Memory Read Flowchart 13.1.4 NVM Unlock Sequence FIGURE 13-6: NVM Unlock Sequence Flowchart EXAMPLE 13-2: NVM Unlock Sequence 13.1.5 Erasing Program Flash Memory 13.1.5.1 Program Flash Memory Erase Sequence EXAMPLE 13-3: Erasing a Program Flash Memory block FIGURE 13-7: PFM Row Erase Flowchart 13.1.6 Writing to Program Flash Memory FIGURE 13-8: Table Writes to Program Flash Memory 13.1.6.1 Program Flash Memory Write Sequence EXAMPLE 13-4: Writing to Program Flash Memory EXAMPLE 13-4: Writing to Program Flash Memory (Continued) FIGURE 13-9: Program Flash Memory (PFM) Write Flowchart 13.1.6.2 Write Verify FIGURE 13-10: Program Flash Memory Verify Flowchart 13.1.6.3 Unexpected Termination of Write Operation 13.1.6.4 Protection Against Spurious Writes 13.2 Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Word Access 13.2.1 Reading Access 13.2.2 Writing Access TABLE 13-4: DIA, DCI, User ID, Dev/REV ID and Configuration Word Access (REG<1:0> = x1) 13.3 Data EEPROM Memory 13.3.1 NVMADRL and NVMADRH Registers 13.3.2 NVMCON1 and NVMCON2 Registers 13.3.3 Reading the Data EEPROM Memory FIGURE 13-11: Data EEPROM Read Flowchart 13.3.4 Writing to the Data EEPROM Memory 13.3.5 Write Verify EXAMPLE 13-5: Data EEPROM Read EXAMPLE 13-6: Data EEPROM Write 13.3.6 Operation During Code- Protect 13.3.7 Protection Against Spurious Write 13.3.8 Erasing the Data EEPROM Memory EXAMPLE 13-7: Data EEPROM Refresh Routine 13.4 Register Definitions: Nonvolatile Memory Register 13-1: NVMCON1: Nonvolatile Memory Control 1 Register Register 13-2: NVMCON2: Nonvolatile Memory Control 2 Register Register 13-3: NVMADRL: Data EEPROM Memory Address Low Register 13-4: NVMADRH: Data EEPROM Memory Address High Register 13-5: NVMDAT: Data EEPROM Memory Data TABLE 13-5: Summary OF Registers Associated with Nonvolatile Memory Control 14.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner 14.1 CRC Module Overview 14.2 CRC Functional Overview EXAMPLE 14-1: CRC Example 14.3 CRC Polynomial Implementation EXAMPLE 14-2: CRC LFSR Example 14.4 CRC Data Sources 14.4.1 CRC from User Data 14.4.2 CRC from Flash 14.5 CRC Check Value 14.6 CRC Interrupt 14.7 Configuring the CRC 14.8 Scanner Module Overview 14.9 Configuring the Scanner 14.10 Scanner Interrupt 14.11 Scanning Modes 14.11.1 TRIGEN = 0, BURSTMD = 0 14.11.2 TRIGEN = 1, BURSTMD = 0 14.11.3 TRIGEN = x, BURSTMD = 1 14.12 Register Definitions: CRC and Scanner Control Register 14-1: CRCCON0: CRC Control Register 0 Register 14-2: CRCCON1: CRC Control Register 1 Register 14-3: CRCDATH: CRC Data High Byte Register Register 14-4: CRCDATL: CRC Data Low Byte Register Register 14-5: CRCACCH: CRC Accumulator High Byte Register Register 14-6: CRCACCL: CRC Accumulator Low Byte Register Register 14-7: CRCSHIFTH: CRC Shift High Byte Register Register 14-8: CRCSHIFTL: CRC Shift Low Byte Register Register 14-9: CRCXORH: CRC XOR High Byte Register Register 14-10: CRCXORL: CRC XOR Low Byte Register Register 14-11: SCANCON0: Scanner Access Control Register 0 TABLE 14-1: Scanner Operating Modes(1) Register 14-12: SCANLADRU: Scan Low Address Upper Byte Register Register 14-13: SCANLADRH: SCAN Low Address High Byte Register Register 14-14: SCANLADRL: SCAN Low Address Low Byte Register Register 14-15: SCANHADRU: Scan High Address Upper Byte Register Register 14-16: SCANHADRH: SCAN High Address High Byte Register Register 14-17: SCANHADRL: SCAN High Address Low Byte Register Register 14-18: SCANTRIG: SCAN Trigger Selection Register TABLE 14-2: Summary of Registers Associated with CRC 15.0 Direct Memory Access (DMA) 15.1 Introduction 15.2 DMA Registers 15.3 DMA Organization FIGURE 15-1: DMA Functional Block Diagram 15.4 DMA Interface TABLE 15-1: DMA Memory Access 15.4.1 DMA Addressing FIGURE 15-2: DMA Pointers Block Diagram 15.4.2 DMA Message Size/Counters FIGURE 15-3: DMA Counters Block Diagram TABLE 15-2: Example Message Size Table 15.5 DMA Message Transfers TABLE 15-3: DMA Initial Conditions TABLE 15-4: DMA Source Pointer/Counter during Operation TABLE 15-5: DMA Destination Pointer/Counter during Operation 15.5.1 Starting DMA Message transfers 15.5.1.1 User Software Control 15.5.1.2 Hardware Trigger, SIRQ 15.5.2 Stopping DMA Message transfers 15.5.2.1 User Software Control 15.5.2.2 Hardware Trigger, AIRQ 15.5.2.3 Source Count Reload 15.5.2.4 Destination Count Reload 15.5.2.5 Clearing the Enable bit 15.5.3 Disable DMA Messages transfers upon completion 15.5.3.1 Clearing the SIRQEN bit 15.5.3.2 Source/Destination Stop 15.6 Types of Hardware Triggers 15.6.1 Edge TRIGGER Requests 15.6.2 Level TRIGGER Requests 15.7 Types of Data Transfers 15.8 DMA Interrupts 15.8.1 DMA Source Count Interrupt 15.8.2 DMA Destination Count Interrupt 15.8.3 Abort Interrupt 15.8.4 Overrun Interrupt 15.9 DMA Setup and Operation FIGURE 15-4: DMA Operation with hardware trigger 15.9.1 Source Stop FIGURE 15-5: GPR-GPR Transactions with Hardware Triggers, SSTP = 1 15.9.2 Destination Stop FIGURE 15-6: GPR-GPR Transactions with Hardware Triggers, DSTP = 1 15.9.3 Continuous Transfer FIGURE 15-7: GPR-GPR Transactions with Hardware Triggers, SSTP, DSTP = 0 15.9.4 Transfer from SFR to GPR FIGURE 15-8: SFR Space to GPR Space Transfer 15.9.5 Overrun Interrupt FIGURE 15-9: Overrun Interrupt 15.9.6 Abort trigger, Message Complete FIGURE 15-10: Abort at the End of Message 15.9.7 Abort trigger, Message In progress FIGURE 15-11: Abort during Message Transfer TABLE 15-6: Example DMA Use Case Table 15.10 Reset 15.11 Power Saving Mode Operation 15.11.1 Sleep Mode 15.11.2 Idle Mode 15.11.3 Doze Mode 15.11.4 Peripheral Module Disable 15.12 DMA Register Interfaces EXAMPLE 15-1: Setup DMA1 to move data from Program Flash Memory to UART1 Transmit Buffer using hardware triggers 15.13 Register definitions: DMA TABLE 15-7: Register and Bit Naming Register 15-1: DMAXCON0: DMAx Control Register 0 Register 15-2: DMAxCON1: DMAx Control Register1 Register 15-3: DMAxBUF: DMAx Data Buffer Register Register 15-4: DMAxSSAL: DMAx Source Start Address Low Register Register 15-5: DMAxSSAH: DMAx Source Start Address High Register Register 15-6: DMAxSSAU: DMAx source Start address Upper Register Register 15-7: DMAxSPTRL: DMAx Source Pointer Low Register Register 15-8: DMAxSPTRH: DMAx Source Pointer High Register Register 15-9: DMAxSPTRU: DMAx Source Pointer Upper Register Register 15-10: DMAxSSZL: DMAx Source Size Low Register Register 15-11: DMAxSSZH: DMAx Source Size High Register Register 15-12: DMAxSCNTL: DMAx Source Count Low Register Register 15-13: DMAxSCNTH: DMAx Source Count High Register Register 15-14: DMAxDSAL: DMAx Destination Start Address Low Register Register 15-15: DMAxDSAH: DMAx Destination Start Address High Register Register 15-16: DMAxDPTRL: DMAx Destination Pointer Low Register Register 15-17: DMAxDPTRH: DMAx Destination Pointer High Register Register 15-18: DMAxDSZL: DMAx Destination Size Low Register Register 15-19: DMAxDSZH: DMAx Destination Size High Register Register 15-20: DMAxDCNTL: DMAx Destination Count Low Register Register 15-21: DMAxDCNTH: DMAx Destination Count High Register Register 15-22: DMAxSIRQ: DMAx Start Interrupt Request Source Selection Register Register 15-23: DMAxAIRQ: DMAx Abort Interrupt Request Source Selection Register TABLE 15-8: DMAxSIRQ AND DMAxAIRQ Trigger Sources TABLE 15-9: Summary of Registers Associated with DMA 16.0 I/O Ports TABLE 16-1: Port Allocation Table for PIC18(L)F25/26K83 Devices 16.1 Generic I/O Port Operation 16.2 I/O Priorities 16.3 PORTx Registers 16.3.1 Data Register EXAMPLE 16-1: Initializing PORTA 16.3.2 Direction Control 16.3.3 Analog Control 16.3.4 Open-Drain Control 16.3.5 Slew Rate Control 16.3.6 Input Threshold Control 16.3.7 Weak Pull-up Control 16.3.8 Edge Selectable Interrupt-on-Change 16.3.9 I2C Pad Control 16.4 PORTE Registers 16.4.1 Master Clear Input (MCLR) 16.4.2 RE3 Weak Pull-up 16.4.3 Interrupt-on-Change 16.5 Register Definitions: Port Control Register 16-1: PORTx: PORTx Register(1) TABLE 16-2: PORT Registers Register 16-2: TRISx: Tri-State Control Register TABLE 16-3: TRIS Registers Register 16-3: LATx: LATx Register(1) TABLE 16-4: LAT Registers Register 16-4: ANSELx: Analog Select Register TABLE 16-5: Analog Select PORT Registers Register 16-5: WPUx: Weak Pull-up Register TABLE 16-6: Weak Pull-Up Port Registers Register 16-6: ODCONx: Open-Drain Control Register TABLE 16-7: Open-Drain Control Registers Register 16-7: SLRCONx: Slew Rate Control Register TABLE 16-8: Slew Rate Control Registers Register 16-8: INLVLx: Input Level Control Register TABLE 16-9: Input Level Port Registers Register 16-9: RxyI2C: I2C PAD Rxy Control Register TABLE 16-10: I2C Pad Control Registers TABLE 16-11: Summary of Registers Associated with I/O 17.0 Peripheral Pin Select (PPS) Module 17.1 PPS Inputs 17.2 PPS Outputs FIGURE 17-1: Simplified PPS Block Diagram 17.3 Bidirectional Pins 17.4 PPS Lock EXAMPLE 17-1: PPS Lock sequence EXAMPLE 17-2: PPS Unlock sequence 17.5 PPS One-way Lock 17.6 Operation During Sleep 17.7 Effects of a Reset 17.8 Register Definitions: PPS Input Selection Register 17-1: xxxPPS: Peripheral xxx Input Selection TABLE 17-1: PPS Input Register Details Register 17-2: RxyPPS: Pin Rxy Output Source Selection Register TABLE 17-2: PPS Output Register Details Register 17-3: PPSLOCK: PPS Lock Register TABLE 17-3: Summary of Registers Associated with the PPS Module 18.0 Interrupt-on-Change 18.1 Enabling the Module 18.2 Individual Pin Configuration 18.3 Interrupt Flags 18.4 Clearing Interrupt Flags EXAMPLE 18-1: Clearing Interrupt Flags (PORTA Example) 18.5 Operation in Sleep FIGURE 18-1: Interrupt-on-Change Block Diagram (PORTA Example) 18.6 Register Definitions: Interrupt-on-Change Control Register 18-1: IOCxP: Interrupt-on-Change Positive Edge Register Example Register 18-2: IOCxN: Interrupt-on-Change Negative Edge Register Example Register 18-3: IOCxF: Interrupt-on-Change Flag Register Example TABLE 18-1: IOC Registers TABLE 18-2: Summary of Registers Associated with Interrupt-on-Change 19.0 Peripheral Module Disable (PMD) 19.1 Disabling a Module 19.2 Enabling a Module 19.3 Effects of a Reset 19.4 System Clock Disable 19.5 Register Definitions: Peripheral Module Disable Register 19-1: PMD0: PMD Control Register 0 Register 19-2: PMD1: PMD Control Register 1 Register 19-3: PMD2: PMD Control Register 2 Register 19-4: PMD3: PMD Control Register 3 Register 19-5: PMD4: PMD Control Register 4 Register 19-6: PMD5: PMD Control Register 5 Register 19-7: PMD6: PMD Control Register 6 Register 19-8: PMD7: PMD Control Register 7 TABLE 19-1: Summary of Registers Associated with Peripheral Module Disable 20.0 Timer0 Module FIGURE 20-1: Block Diagram of Timer0 20.1 Timer0 Operation 20.1.1 16-Bit Mode 20.1.1.1 Timer0 Reads and Writes in 16-Bit Mode 20.1.2 8-BIT Mode 20.1.3 Counter Mode 20.1.4 Timer Mode 20.1.5 Asynchronous Mode 20.1.6 Synchronous Mode 20.2 Clock Source Selection 20.2.1 Internal Clock Source 20.2.2 External Clock Source 20.3 Programmable Prescaler 20.4 Programmable Postscaler 20.5 Operation During Sleep 20.6 Timer0 Interrupts 20.7 Timer0 Output 20.8 Register Definitions: Timer0 Control Register 20-1: T0CON0: TIMER0 Control Register 0 Register 20-2: T0CON1: TIMER0 Control Register 1 Register 20-3: TMR0L: TIMER0 Count Register Register 20-4: TMR0H: TIMER0 Period Register TABLE 20-1: Summary of Registers Associated with TIMER0 21.0 Timer1/3/5 Module with Gate Control FIGURE 21-1: Timer1/3/5 Block Diagram 21.1 Timer1/3/5 Operation TABLE 21-1: Timer1/3/5 Enable Selections 21.2 Clock Source Selection 21.2.1 Internal Clock Source 21.2.2 External Clock Source 21.3 Timer1/3/5 Prescaler 21.4 Timer1/3/5 Operation in Asynchronous Counter Mode 21.4.1 Reading and Writing Timer1/3/ 5 in Asynchronous Counter Mode 21.5 Timer1/3/5 16-Bit Read/Write Mode FIGURE 21-2: Timer1/3/5 16-Bit Read/ Write Mode Block Diagram 21.6 Timer1/3/5 Gate 21.6.1 Timer1/3/5 Gate Enable TABLE 21-2: Timer1/3/5 Gate Enable Selections 21.6.2 Timer1/3/5 Gate Source Selection 21.6.3 Timer1/3/5 Gate Toggle Mode 21.6.4 Timer1/3/5 Gate Single-Pulse Mode 21.6.5 Timer1/3/5 Gate Value Status 21.6.6 Timer1/3/5 Gate Event Interrupt 21.7 Timer1/3/5 Interrupt 21.8 Timer1/3/5 Operation During Sleep 21.9 CCP Capture/Compare Time Base 21.10 CCP Special Event Trigger FIGURE 21-3: Timer1/3/5 Incrementing Edge FIGURE 21-4: Timer1/3/5 Gate Enable Mode FIGURE 21-5: Timer1/3/5 Gate Toggle Mode FIGURE 21-6: Timer1/3/5 Gate Single-Pulse Mode FIGURE 21-7: Timer1/3/5 Gate Single-Pulse and Toggle Combined Mode 21.11 Peripheral Module Disable 21.12 Register Definitions: Timer1/3/5 Register 21-1: TxCON: Timerx Control Register Register 21-2: TxGCON: Timerx Gate Control Register Register 21-3: TxCLK: Timerx Clock Register Register 21-4: TxGATE: Timerx Gate ISM Register Register 21-5: TMRxL: Timerx Low Byte Register Register 21-6: TMRxH: Timerx High Byte Register TABLE 21-3: Summary of Registers Associated with Timer1/3/5 as a Timer/Counter 22.0 Timer2/4/6 Module FIGURE 22-1: Timer2 Block Diagram FIGURE 22-2: Timer2 Clock Source Block Diagram 22.1 Timer2 Operation 22.1.1 Free Running Period Mode 22.1.2 One-Shot Mode 22.1.3 Monostable Mode 22.2 Timer2 Output 22.3 External Reset Sources TABLE 22-1: Timer2 Operating Modes 22.4 Timer2 Interrupt FIGURE 22-3: Timer2 Prescaler, Postscaler, and Interrupt Timing Diagram 22.5 Operation Examples 22.5.1 Software Gate Mode FIGURE 22-4: Software Gate Mode Timing Diagram 22.5.2 Hardware Gate Mode FIGURE 22-5: Hardware Gate Mode Timing Diagram (MODE = 00001) 22.5.3 Edge-Triggered Hardware Limit Mode FIGURE 22-6: Edge Triggered Hardware Limit Mode Timing Diagram (MODE=00100) 22.5.4 Level-Triggered Hardware Limit Mode FIGURE 22-7: Level Triggered Hardware Limit Mode Timing Diagram (MODE = 00111) 22.5.5 Software Start One-Shot Mode FIGURE 22-8: Software Start One-shot Mode Timing Diagram (MODE = 01000) 22.5.6 Edge-Triggered One-Shot Mode FIGURE 22-9: Edge Triggered One-Shot Mode Timing Diagram (MODE = 01001) 22.5.7 Edge-Triggered Hardware Limit One-Shot Mode FIGURE 22-10: Edge Triggered Hardware Limit One-Shot Mode Timing Diagram (MODE = 01100)) 22.5.8 Level Reset, Edge-Triggered Hardware Limit One-Shot Modes FIGURE 22-11: Low Level Reset, Edge-Triggered hardware Limit one-Shot Mode Timing Diagram (MODE = 01110) 22.5.9 Edge-Triggered Monostable Modes FIGURE 22-12: Rising Edge-Triggered Monostable Mode Timing Diagram (MODE = 10001) 22.5.10 Level-Triggered Hardware Limit One-Shot Modes FIGURE 22-13: Level-Triggered hardware Limit one-Shot Mode Timing Diagram (MODE = 10110) 22.6 Timer2 Operation During Sleep 22.7 Register Definitions: Timer2/4/6 Control TABLE 22-2: Operating Modes Register 22-1: TxCLK: Timerx Clock Selection Register Register 22-2: TxRST: Timer2 External Reset Signal Selection Register Register 22-3: TxTMR: Timerx Counter Register Register 22-4: TxPR: Timerx Period Register Register 22-5: TxCON: Timerx Control Register Register 22-6: TxHLT: Timerx Hardware Limit Control Register TABLE 22-3: Summary of Registers Associated with Timer2 23.0 Capture/Compare/PWM Module 23.1 CCP Module Configuration 23.1.1 CCP Modules and Timer Resources TABLE 23-1: CCP Mode – Timer Resource 23.1.2 Open-Drain Output Option 23.2 Capture Mode 23.2.1 Capture Sources 23.2.2 Timer1 Mode Resource FIGURE 23-1: Capture Mode Operation Block Diagram 23.2.3 Software Interrupt Mode 23.2.4 Capture During Sleep 23.3 Compare Mode FIGURE 23-2: Compare Mode Operation Block Diagram 23.3.1 CCPx Pin Configuration 23.3.2 Timer1 Mode Resource 23.3.3 Auto-Conversion Trigger 23.3.4 Compare During Sleep 23.4 PWM Overview 23.4.1 Standard PWM Operation FIGURE 23-3: CCP PWM Output Signal FIGURE 23-4: Simplified PWM Block Diagram 23.4.2 Setup for PWM Operation 23.4.3 Timer2 Timer Resource 23.4.4 PWM Period EQUATION 23-1: PWM Period 23.4.5 PWM Duty Cycle FIGURE 23-5: PWM 10-Bit Alignment EQUATION 23-2: Pulse Width EQUATION 23-3: Duty Cycle Ratio 23.4.6 PWM Resolution EQUATION 23-4: PWM Resolution TABLE 23-2: Example PWM Frequencies and Resolutions (Fosc = 20 MHz) TABLE 23-3: Example PWM Frequencies and Resolutions (Fosc = 8 MHz) 23.4.7 Operation in Sleep Mode 23.4.8 Changes in System Clock Frequency 23.4.9 Effects of Reset 23.5 Register Definitions: CCP Control Register 23-1: CCPxCON: CCPx Control Register Register 23-2: CCPTMRS0: CCP Timers Control Register 0 Register 23-3: CCPTMRS1: CCP Timers Control Register 1 Register 23-4: CCPxCAP: Capture Input Selection Multiplexer Register Register 23-5: CCPRxL: CCPx Register Low Byte Register 23-6: CCPRxH: CCPx Register High Byte TABLE 23-4: Summary of Registers Associated with CCPx 24.0 Pulse-Width Modulation (PWM) FIGURE 24-1: Simplified PWM Block Diagram FIGURE 24-2: PWM Output 24.1 PWMx Pin Configuration 24.1.1 Fundamental Operation 24.1.2 PWM Output Polarity 24.1.3 PWM Period EQUATION 24-1: PWM Period 24.1.4 PWM Duty Cycle EQUATION 24-2: Pulse Width EQUATION 24-3: Duty Cycle Ratio 24.1.5 PWM Resolution EQUATION 24-4: PWM Resolution TABLE 24-1: Example PWM Frequencies and Resolutions (Fosc = 20 MHz) TABLE 24-2: Example PWM Frequencies and Resolutions (Fosc = 8 MHz) 24.1.6 Operation in Sleep Mode 24.1.7 Changes in System Clock Frequency 24.1.8 Effects of Reset 24.1.9 Setup for PWM Operation using PWMx Pins 24.1.10 Setup for PWM Operation to Other Device Peripherals 24.2 Register Definitions: PWM Control Register 24-1: PWMxCON: PWM Control Register Register 24-2: CCPTMRS1: CCP Timers Control Register 1 Register 24-3: PWMXDCH: PWM Duty Cycle High Bits Register 24-4: PWMxDCL: PWM Duty Cycle Low Bits TABLE 24-3: Summary of Registers Associated with PWM 25.0 Signal Measurement Timer (SMTX) FIGURE 25-1: SMT Block Diagram FIGURE 25-2: SMT Signal and Window Block Diagram 25.1 SMT Operation 25.1.1 Clock Sources 25.1.2 Period Match interrupt 25.2 Basic Timer Function Registers 25.2.1 Time Base 25.2.2 Pulse-Width Latch registers 25.2.3 Period Latch registers 25.3 Halt Operation 25.4 Polarity Control 25.5 Status Information 25.5.1 Window Status 25.5.2 Signal Status 25.5.3 GO Status 25.6 Modes of Operation 25.6.1 Timer Mode TABLE 25-1: Modes of Operation FIGURE 25-3: Timer Mode Timing Diagram 25.6.2 Gated Timer Mode FIGURE 25-4: Gated Timer Mode Repeat Acquisition Timing Diagram FIGURE 25-5: Gated Timer Mode Single Acquisition Timing Diagram 25.6.3 Period and Duty Cycle Mode FIGURE 25-6: Period And Duty-Cycle Repeat Acquisition Mode Timing Diagram FIGURE 25-7: Period And Duty-Cycle Single Acquisition Timing Diagram 25.6.4 High and Low Measure Mode FIGURE 25-8: High and Low Measure Mode Repeat Acquisition Timing Diagram FIGURE 25-9: High and Low Measure Mode Single Acquisition Timing Diagram 25.6.5 Windowed Measure Mode FIGURE 25-10: Windowed Measure Mode Repeat Acquisition Timing Diagram FIGURE 25-11: Windowed Measure Mode Single Acquisition Timing Diagram 25.6.6 Gated Windowed Measure Mode FIGURE 25-12: Gated Windowed Measure Mode Repeat Acquisition Timing Diagram FIGURE 25-13: Gated Windowed Measure Mode Single Acquisition Timing Diagrams 25.6.7 Time of Flight Measure Mode FIGURE 25-14: Time Of Flight Mode Repeat Acquisition Timing Diagram FIGURE 25-15: Time Of Flight Mode Single Acquisition Timing Diagram 25.6.8 Capture Mode FIGURE 25-16: Capture Mode Repeat Acquisition Timing Diagram FIGURE 25-17: Capture Mode Single Acquisition Timing Diagram 25.6.9 Counter Mode FIGURE 25-18: Counter Mode Timing Diagram 25.6.10 Gated Counter Mode FIGURE 25-19: Gated Counter Mode Repeat Acquisition Timing Diagram FIGURE 25-20: Gated Counter Mode Single Acquisition Timing Diagram 25.6.11 Windowed Counter Mode FIGURE 25-21: Windowed Counter Mode Repeat Acquisition Timing Diagram FIGURE 25-22: Windowed Counter Mode Single Acquisition Timing Diagram 25.7 Interrupts 25.7.1 PW and PR Acquisition interrupts 25.7.2 Counter Period Match interrupt 25.8 Register Definitions: SMT Control TABLE 25-2: Long Bit Names Prefixes for SMT Peripherals Register 25-1: SMTXCON0: SMT Control Register 0 Register 25-2: SMTXCON1: SMT Control Register 1 Register 25-3: SMTXSTAT: SMT Status Register Register 25-4: SMTXCLK: SMT Clock Selection Register Register 25-5: SMTXWIN: SMTX Window Input Select Register Register 25-6: SMTXSIG: SMTX Signal Input Select Register Register 25-7: SMTXTMRL: SMT Timer Register – Low Byte Register 25-8: SMTXTMRH: SMT Timer Register – High Byte Register 25-9: SMTXTMRU: SMT Timer Register – Upper Byte Register 25-10: SMTxCPRL: SMT Captured Period Register – Low Byte Register 25-11: SMTxCPRH: SMT Captured Period Register – High Byte Register 25-12: SMTxCPRU: SMT Captured Period Register – Upper Byte Register 25-13: SMTxCPWL: SMT Captured Pulse Width Register – Low Byte Register 25-14: SMTxCPWH: SMT Captured Pulse Width Register – High Byte Register 25-15: SMTxCPWU: SMT Captured Pulse Width Register – Upper Byte Register 25-16: SMTxPRL: SMT Period Register – Low Byte Register 25-17: SMTxPRH: SMT Period Register – High Byte Register 25-18: SMTxPRU: SMT Period Register – Upper Byte TABLE 25-3: Summary of Registers Associated with SMTx 26.0 Complementary Waveform Generator (CWG) Module 26.1 Fundamental Operation 26.2 Operating Modes 26.2.1 Half-Bridge Mode FIGURE 26-1: Simplified CWG Block Diagram (Half-Bridge Mode, MODE<2:0> = 100) FIGURE 26-2: CWGx Half-Bridge Mode Operation 26.2.2 Push-Pull Mode FIGURE 26-3: Simplified CWG Block Diagram (Push-Pull Mode, MODE<2:0> = 101) FIGURE 26-4: CWGx Push-Pull Mode Operation 26.2.3 Full-Bridge Modes FIGURE 26-5: Example of Full-Bridge Application FIGURE 26-6: Simplified CWG Block Diagram (Forward and Reverse Full-Bridge Modes) FIGURE 26-7: Example of Full-Bridge Output 26.2.3.1 Direction Change in Full-Bridge Mode 26.2.3.2 Dead-Band Delay in Full-Bridge Mode FIGURE 26-8: Example of PWM Direction Change at Near 100% Duty Cycle 26.2.4 Steering Modes 26.2.4.1 Synchronous Steering Mode FIGURE 26-9: Example of Synchronous Steering (MODE<2:0> = 001) 26.2.4.2 Asynchronous Steering Mode FIGURE 26-10: Example of Asynchronous Steering (MODE<2:0>= 000) 26.2.4.3 Start-up Considerations FIGURE 26-11: Simplified CWG Block Diagram (Output Steering Modes) 26.3 Clock Source 26.4 Selectable Input Sources TABLE 26-1: Selectable Input Sources 26.5 Output Control 26.5.1 CWG Outputs 26.5.2 Polarity Control 26.6 Dead-Band Control 26.6.1 Dead-Band Functionality in Half-Bridge mode 26.6.2 Dead-Band Functionality in Full-Bridge mode 26.7 Rising Edge and Reverse Dead Band 26.8 Falling Edge and Forward Dead Band FIGURE 26-12: Dead-Band Operation, CWGxDBR = 0x01, CWGxDBF = 0x02 FIGURE 26-13: Dead-Band Operation, CWGxDBR = 0x03, CWGxDBF = 0x06, Source Shorter Than Dead Band 26.9 Dead-Band Jitter EQUATION 26-1: Dead-Band Delay Time Calculation 26.10 Auto-Shutdown 26.10.1 Shutdown 26.10.1.1 Software Generated Shutdown 26.10.1.2 External Input Source 26.10.1.3 Pin Override Levels 26.10.1.4 Auto-Shutdown Interrupts 26.11 Auto-Shutdown Restart 26.11.1 Software-Controlled Restart 26.11.2 Auto-Restart 26.12 Operation During Sleep 26.13 Configuring the CWG FIGURE 26-14: CWG Shutdown Block Diagram FIGURE 26-15: Shutdown Functionality, Auto-Restart Disabled (REN = 0, LSAC = 01, LSBD = 01) FIGURE 26-16: Shutdown Functionality, Auto-Restart Enabled (REN = 1, LSAC = 01, LSBD = 01) 26.14 Register Definitions: CWG Control Register 26-1: CWGxCON0: CWG Control Register 0 Register 26-2: CWGxCON1: CWG Control Register 1 Register 26-3: CWGxCLK: CWGx Clock Input Selection Register Register 26-4: CWGxISM: CWGx Input Selection Register Register 26-5: CWGxSTR(1): CWG Steering Control Register Register 26-6: CWGxAS0: CWG Auto-Shutdown Control Register 0 Register 26-7: CWGxAS1: CWG Auto-Shutdown Control Register 1 Register 26-8: CWGxDBR: CWG Rising Dead-Band Count Register Register 26-9: CWGxDBF: CWG Falling Dead-Band Count Register TABLE 26-2: Summary of Registers Associated with CWG 27.0 Configurable Logic Cell (CLC) FIGURE 27-1: CLCx Simplified Block Diagram 27.1 CLCx Setup 27.1.1 Data Selection TABLE 27-1: CLCx Data Input Selection (Continued) 27.1.2 Data Gating TABLE 27-2: Data Gating Logic 27.1.3 Logic Function 27.1.4 Output Polarity 27.2 CLCx Interrupts 27.3 Output Mirror Copies 27.4 Effects of a Reset 27.5 Operation During Sleep 27.6 CLCx Setup Steps FIGURE 27-2: Input Data Selection and Gating FIGURE 27-3: Programmable Logic Functions 27.7 Register Definitions: CLC Control Register 27-1: CLCxCON: Configurable Logic Cell Control Register Register 27-2: CLCxPOL: Signal Polarity Control Register Register 27-3: CLCxSEL0: Generic CLCx Data 0 Select Register Register 27-4: CLCxSEL1: Generic CLCx Data 1 Select Register Register 27-5: CLCxSEL2: Generic CLCx Data 2 Select Register Register 27-6: CLCxSEL3: Generic CLCx Data 3 Select Register Register 27-7: CLCxGLS0: Gate 0 Logic Select Register Register 27-8: CLCxGLS1: Gate 1 Logic Select Register Register 27-9: CLCxGLS2: Gate 2 Logic Select Register Register 27-10: CLCxGLS3: Gate 3 Logic Select Register Register 27-11: CLCDATA: CLC Data Output TABLE 27-3: Summary of Registers Associated with CLCx 28.0 Numerically Controlled Oscillator (NCO) Module FIGURE 28-1: Direct Digital Synthesis Module Simplified Block Diagram 28.1 NCO Operation EQUATION 28-1: NCO Overflow Frequency 28.1.1 NCO CLOCK SOURCES 28.1.2 ACCUMULATOR 28.1.3 ADDER 28.1.4 INCREMENT REGISTERS 28.2 FIXED DUTY CYCLE MODE 28.3 PULSE FREQUENCY MODE 28.3.1 OUTPUT PULSE-WIDTH CONTROL 28.4 OUTPUT POLARITY CONTROL 28.5 Interrupts 28.6 Effects of a Reset 28.7 Operation in Sleep FIGURE 28-2: FDC Output Mode Operation Diagram 28.8 NCO Control Registers Register 28-1: NCO1CON: NCO Control Register Register 28-2: NCO1CLK: NCO1 Input Clock Control Register Register 28-3: NCO1ACCL: NCO1 Accumulator Register – Low Byte Register 28-4: NCO1ACCH: NCO1 Accumulator Register – High Byte Register 28-5: NCO1ACCU: NCO1 Accumulator Register – Upper Byte(1) Register 28-6: NCO1INCL: NCO1 Increment Register – Low Byte(1,2) Register 28-7: NCO1INCH: NCO1 Increment Register – High Byte(1) Register 28-8: NCO1INCU: NCO1 Increment Register – Upper Byte(1) TABLE 28-1: Summary of Registers Associated with NCO 29.0 Zero-Cross Detection (ZCD) Module 29.1 External Resistor Selection EQUATION 29-1: External Resistor FIGURE 29-1: External Voltage FIGURE 29-2: Simplified ZCD Block Diagram 29.2 ZCD Logic Output 29.3 ZCD Logic Polarity 29.4 ZCD Interrupts 29.5 Correcting for Vcpinv offset EQUATION 29-2: ZCD Event Offset EQUATION 29-3: ZCD Pull-up/down EQUATION 29-4: Pull-up/down Resistor Values 29.6 Handling Vpeak Variations EQUATION 29-5: Series R for V range 29.7 Operation During Sleep 29.8 Effects of a Reset 29.9 Disabling the ZCD Module 29.10 Register Definitions: ZCD Control Register 29-1: ZCDCON: Zero-Cross Detect Control Register TABLE 29-1: Summary of Registers Associated with the ZCD Module 30.0 Data Signal Modulator (DSM) Module FIGURE 30-1: Simplified Block Diagram of the Data Signal Modulator 30.1 DSM Operation 30.2 Modulator Signal Sources 30.3 Carrier Signal Sources 30.4 Carrier Synchronization FIGURE 30-2: On Off Keying (OOK) Synchronization FIGURE 30-3: No Synchronization (CHSYNC = 0, CLSYNC = 0) FIGURE 30-4: Carrier High Synchronization (CHSYNC = 1, CLSYNC = 0) FIGURE 30-5: Carrier Low Synchronization (CHSYNC = 0, CLSYNC = 1) FIGURE 30-6: Full Synchronization (CHSYNC = 1, CLSYNC = 1) 30.5 Carrier Source Polarity Select 30.6 Programmable Modulator Data 30.7 Modulated Output Polarity 30.8 Operation in Sleep Mode 30.9 Effects of a Reset 30.10 Peripheral Module Disable 30.11 Register Definitions: Modulation Control Register 30-1: MD1CON0: Modulation Control Register 0 Register 30-2: MD1CON1: Modulation Control Register 1 Register 30-3: MD1CARH: Modulation High Carrier Control Register Register 30-4: MD1CARL: Modulation Low Carrier Control Register TABLE 30-1: MD1CARH/MD1CARL Selection MUX Connections Register 30-5: MD1SRC: Modulation Source Control Register TABLE 30-2: MD1SRC Selection MUX Connections TABLE 30-3: Summary of Registers Associated with Data Signal Modulator Mode 31.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support FIGURE 31-1: UART Transmit Block Diagram FIGURE 31-2: UART Receive Block Diagram 31.1 UART I/O Pin Configuration 31.2 UART Asynchronous Modes 31.2.1 UART Asynchronous Transmitter 31.2.1.1 Enabling the Transmitter 31.2.1.2 Transmitting Data 31.2.1.3 Transmit Data Polarity 31.2.1.4 Transmit Interrupt Flag 31.2.1.5 TSR Status 31.2.1.6 Transmitter 7-bit Mode 31.2.1.7 Transmitter Parity Modes 31.2.1.8 Asynchronous Transmission Setup FIGURE 31-3: Asynchronous Transmission FIGURE 31-4: Asynchronous Transmission (Back-to-Back) 31.2.2 UART Asynchronous Receiver 31.2.2.1 Enabling the Receiver 31.2.2.2 Receiving Data 31.2.2.3 Receive Interrupts 31.2.2.4 Receive Framing Error 31.2.2.5 Receiver Parity Modes 31.2.2.6 Receive FIFO Overflow 31.2.2.7 Asynchronous Reception Setup FIGURE 31-5: Asynchronous Reception 31.3 Asynchronous Address Mode 31.3.1 Address Mode Transmit 31.3.2 Address Mode Receive 31.4 DMX Mode 31.4.1 DMX Controller 31.4.2 DMX Receiver FIGURE 31-6: DMX Transmit Sequence 31.5 LIN Modes 31.5.1 LIN Master/Slave Mode 31.5.2 LIN Slave Mode 31.5.2.1 LIN Slave Receiver 31.5.2.2 LIN Slave Transmitter 31.6 DALI Mode 31.6.1 Control Device 31.6.2 Control Gear FIGURE 31-7: Manchester Timing FIGURE 31-8: DALI Frame Timing FIGURE 31-9: DALI Forward/Back Frame Timing 31.7 General Purpose Manchester 31.8 Polarity 31.9 Stop Bits 31.9.1 Delayed UxRXIF 31.10 Operation after FIFO overflow 31.11 Receive and Transmit Buffers 31.11.1 FIFO status 31.11.2 FIFO Reset 31.12 Flow Control 31.12.1 Hardware Flow Control FIGURE 31-10: Flow Control 31.12.2 RS-485 Transceiver control FIGURE 31-11: RS-485 Configuration 31.12.3 XON/XOFF Flow Control 31.13 Checksum 31.13.1 Transmit Checksum Method 31.13.2 Receive Checksum Method 31.14 Collision Detection 31.15 RX/TX Activity Timeout 31.16 Clock Accuracy with Asynchronous Operation 31.17 UART Baud Rate Generator (BRG) EXAMPLE 31-1: Calculating Baud Rate Error TABLE 31-1: Baud Rate Formulas 31.17.1 Auto-Baud Detect TABLE 31-2: BRG Counter Clock Rates FIGURE 31-12: Automatic Baud Rate Calibration 31.17.2 Auto-Baud Overflow 31.17.3 Auto-Wake-up on Break 31.17.3.1 Special Considerations FIGURE 31-13: Auto-Wake-up Bit (WUE) Timing During Normal Operation FIGURE 31-14: Auto-Wake-up Bit (WUE) Timings During Sleep 31.18 Transmitting a Break 31.19 Receiving a Break 31.20 UART Operation During Sleep FIGURE 31-15: Send Break Character Sequence 31.21 Register Definitions: UART Control Register 31-1: UxCON0: UART Control Register 0 Register 31-2: UxCON1: UART Control Register 1 Register 31-3: UxCON2: UART Control Register 2 Register 31-4: UxERRIR: UART Error Interrupt Flag Register Register 31-5: UxERRIE: UART Error Interrupt Enable Register Register 31-6: UxUIR: UART General Interrupt Register Register 31-7: UxFIFO: UART FIFO Status Register Register 31-8: UxBRGL: UART Baud Rate Generator Low Register Register 31-9: UxBRGH: UART Baud Rate Generator High Register Register 31-10: UxRXB: UART Receive Register Register 31-11: UxTXB: UART Transmit Register Register 31-12: UxP1H: UART Parameter 1 High Register Register 31-13: UxP1L: UART Parameter 1 Low Register Register 31-14: UxP2H: UART Parameter 2 High Register Register 31-15: UxP2L: UART Parameter 2 Low Register Register 31-16: UxP3H: UART Parameter 3 High Register Register 31-17: UxP3L: UART Parameter 3 Low Register Register 31-18: UxTXCHK: UART Transmit Checksum Result Register Register 31-19: UxRXCHK: UART Receive Checksum Result Register TABLE 31-3: Summary of Registers Associated with the UART 32.0 Serial Peripheral Interface (SPI) Module 32.1 SPI Module Overview FIGURE 32-1: SPI Module Simplified Block Diagram FIGURE 32-2: SPI Master/Slave Connection With FIFOs 32.2 SPI REGISTERS 32.3 SPI MODE OPERATION 32.3.1 Enabling and Disabling the SPI module 32.3.2 BUSY bit 32.3.3 Transmit and Receive FIFOs 32.3.4 LSb vs. MSb-first operation 32.3.5 Input and Output Polarity Bits 32.4 Transfer Counter 32.4.1 Total Bit Count Mode (BMODE = 0) 32.4.2 Variable Transfer Size Mode (BMODE = 1) 32.4.3 Transfer Counter in Slave mode 32.5 Master mode TABLE 32-1: Master Mode TXR/RXR Settings 32.5.1 Full-Duplex Mode FIGURE 32-3: SPI Master Operation – Data Exchange, TXR/RXR = 1/1 32.5.2 Transmit Only Mode FIGURE 32-4: SPI Master Operation, Command+Write Data, TXR/RXR=1/0 32.5.3 Receive Only Mode FIGURE 32-5: SPI Master Operation, Command+Read Data, TXR/RXR=0/1 32.5.4 Transfer Off Mode 32.5.5 Master Mode Slave Select Control 32.5.5.1 Hardware Slave Select Control FIGURE 32-6: SPI Master SS Operation- CKE = 0, BMODE = 1, TCWIDTH = 0, SSP = 0 32.5.5.2 Software Slave Select Control 32.5.6 Master Mode SPI Clock Configuration 32.5.6.1 SPI Clock Selection EQUATION 32-1: Frequency of SCK Output Signal 32.5.6.2 CKE, CKP and SMP FIGURE 32-7: Clocking Detail – Master Mode, CKE/SMP = 0/0 FIGURE 32-8: Clocking Detail – Master Mode, CKE/SMP = 1/1 FIGURE 32-9: Clocking Detail – Master Mode, CKE = 0, SMP = 1 FIGURE 32-10: Clocking Detail – Master Mode, CKE = 1, SMP = 0 32.5.6.3 SCK Start-Up Delay 32.6 Slave Mode 32.6.1 Slave Mode Transmit options 32.6.1.1 SDO Drive/Tri-state 32.6.1.2 SDO Output Data TABLE 32-2: Slave Mode Transmit 32.6.2 Slave Mode Receive Options FIGURE 32-11: SPI Slave Mode Operation – Interrupt-Driven, Master Writes 2+3 Bytes 32.6.3 Slave Mode Slave Select 32.6.4 Slave Mode Clock Configuration 32.6.5 Daisy-Chain Configuration FIGURE 32-12: Traditional SPI Daisy – Chain Connection FIGURE 32-13: SPI Daisy-Chain Connection with Chained SCK 32.7 SPI Operation in Sleep Mode 32.8 SPI Interrupts 32.8.1 SPI Receiver data interrupt 32.8.2 SPI Transmitter Data Interrupt 32.8.3 SPI Module Status Interrupts 32.8.3.1 Shift Register Empty Interrupt 32.8.3.2 Transfer Counter is Zero Interrupt 32.8.3.3 Start of Slave Select and End of Slave Select Interrupts FIGURE 32-14: Transfer and Slave Select Interrupt timings 32.8.3.4 Receiver Overflow and Transmitter Underflow Interrupts 32.9 Register definitions: SPI Register 32-1: SPIxINTF: SPI INTERRUPT FLAG REGISTER Register 32-2: SPIxINTE: SPI INTERRUPT ENABLE REGISTER Register 32-3: SPIxTCNTL – SPI TRANSFER COUNTER LSB REGISTER Register 32-4: SPIxTCNTH: SPI TRANSFER COUNTER MSB REGISTER Register 32-5: SPIxTWIDTH: SPI TRANSFER WIDTH REGISTER Register 32-6: SPIxBAUD: SPI BAUD RATE REGISTER Register 32-7: SPIxCON0: SPI CONFIGURATION REGISTER 0 Register 32-8: SPIxCON1: SPI CONFIGURATION REGISTER 1 Register 32-9: SPIxCON2: SPI CONFIGURATION REGISTER 2 Register 32-10: SPIxSTATUS: SPI Status Register Register 32-11: SPIxRXB: SPI Read Buffer Register Register 32-12: SPIxTxB: SPI Transmit Buffer Register Register 32-13: SPIxCLK: SPI Clock Selection Register TABLE 32-3: Summary of Registers Associated with SPI 33.0 I2C Module FIGURE 33-1: I2C Module Block Diagram 33.1 I2C Features 33.2 I2C Module Overview FIGURE 33-2: I2C Master/Slave Connections 33.3 I2C Mode Operation 33.3.1 Definition of I2C Terminology TABLE 33-1: I2C BUS TERMS 33.3.2 Byte Format 33.3.3 SDA and SCL pins 33.3.4 SDA Hold Time 33.3.5 Start Condition 33.3.6 Stop Condition FIGURE 33-3: Start and Stop Conditions 33.3.7 Restart Condition FIGURE 33-4: Restart Condition 33.3.8 Acknowledge Sequence 33.3.9 Bus Time-Out 33.3.10 Address Buffers TABLE 33-2: Address Buffer Direction as per I2C Mode 33.3.10.1 Slave Mode (7-bit) 33.3.10.2 Slave Mode (10-bit) 33.3.10.3 Master Mode (7-bit) 33.3.10.4 Master Mode (10-bit) 33.3.10.5 Multi-Master Mode (7-bit only) 33.3.11 Receive and Transmit Buffer 33.3.12 Clock Stretching 33.3.12.1 Clock Stretching for Buffer Operations 33.3.12.2 Clock Stretching for Other Slave Operations 33.3.13 Data Byte Count 33.4 I2C Slave Mode 33.4.1 Slave Addressing Modes 33.4.1.1 7-bit Addresses Mode 33.4.1.2 7-bit Addresses with Masking 33.4.1.3 10-bit Addresses 33.4.1.4 10-bit Address with Masking 33.4.2 General Call Address Support FIGURE 33-5: Slave Mode General Call Address Sequence 33.4.3 Slave Operation in 7-bit Addressing Mode 33.4.3.1 Slave Reception (7-bit Addressing Mode) FIGURE 33-6: I2C Slave, 7-Bit Address, Reception (ACKTIE = 0, ADRIE = 0, WRIE = 0) FIGURE 33-7: I2C Slave, 7-Bit Address, Reception With I2CxCNT (ACKTIE = 1, ADRIE = 0, WRIE = 0) FIGURE 33-8: I2C Slave, 7-Bit Address, Reception (ACKTIE = 0, ADRIE = 1, WRIE = 1) 33.4.3.2 Slave Transmission (7-bit Addressing Mode) FIGURE 33-9: I2C Slave, 7-Bit Address, Transmission FIGURE 33-10: I2C Slave, 7-Bit Address, Transmission (No Clock Stretching) 33.4.3.3 Slave operation in 10-bit Addressing Mode 33.4.3.4 Slave Reception (10-bit Addressing Mode) FIGURE 33-11: I2C Slave, 10-Bit Address, Reception With Stop (ADB = 1) 33.4.3.5 Slave Transmission (10-bit Addressing Mode) FIGURE 33-12: I2C Slave, 10-Bit Address, Transmission 33.5 I2C Master Mode 33.5.1 I2C Master Mode Operation 33.5.1.1 Master Transmitter 33.5.1.2 Master Receiver 33.5.2 Master Clock Source and Arbitration 33.5.3 Bus Free Time 33.5.4 Master Clock Timing 33.5.4.1 Clock Timing with FME = 0 FIGURE 33-13: Clock Synthesis Timing (FME = 0) 33.5.4.2 Clock Timing with FME = 1 FIGURE 33-14: Clock Synthesis Timing (FME = 1) 33.5.5 I2C Master Mode Start Condition Timing FIGURE 33-15: Start Condition Timing 33.5.6 I2C Master Mode Repeated Start Condition Timing FIGURE 33-16: Repeated Start Condition Timing 33.5.7 Acknowledge Sequence Timing FIGURE 33-17: Acknowledge Sequence Timing 33.5.8 Stop Condition Timing FIGURE 33-18: Stop Condition during Receive or Transmit 33.5.9 Master Transmission in 7-bit Addressing Mode FIGURE 33-19: I2C Master, 7-Bit Address, Transmission With Stop 33.5.10 Master Reception in 7-bit Addressing Mode FIGURE 33-20: I2C Master, 7-Bit Address, Reception 33.5.11 Master Transmission in 10-bit Addressing Mode FIGURE 33-21: I2C Master, 10-Bit Address, Transmission With Stop 33.5.12 Master Reception in 10-bit Addressing Mode FIGURE 33-22: I2C Master, 10-Bit Address, Reception (Using RSEN Bit) 33.6 I2C Multi-Master Mode 33.6.1 Multi-Master Mode Bus Collision FIGURE 33-23: Bus Collision Timing for Transmit and Acknowledge FIGURE 33-24: I2C Multi-Master, 7-Bit Address, Write (ADRIE = 1, WRIE = 0) 33.7 Register Definitions: I2C Control Register 33-1: I2CxCon0: I2C Control register 0 Register 33-2: I2CxCon1: I2C Control register 1 Register 33-3: I2CxCon2: I2C Control register 2 Register 33-4: I2CxCLK: I2C Clock Selection Register Register 33-5: I2CxBTO: I2C Bus Timeout Selection Register Register 33-6: I2CxSTAT0: I2C STATUS REGISTER 0 Register 33-7: I2CxSTAT1: I2C STATUS REGISTER 1 Register 33-8: I2CxERR: I2C Error REGISTER Register 33-9: I2CxCNT: I2C Byte Count REGISTER Register 33-10: I2CxPIR: I2CxIF Interrupt Flag REGISTER Register 33-11: I2CxPIE: I2CxIE Interrupt and Hold Enable REGISTER Register 33-12: I2CxADR0: I2C ADDRESS 0 REGISTER Register 33-13: I2CxADR1: I2C ADDRESS 1 REGISTER Register 33-14: I2CxADR2: I2C ADDRESS 2 REGISTER Register 33-15: I2CxADR3: I2C ADDRESS 3 REGISTER Register 33-16: I2CxADB0: I2C ADDRESS Data BUFFER 0 register(1) Register 33-17: I2CxADB1: I2C ADDRESS Data BUFFER 1 register(1) 34.0 CAN Module 34.1 Module Overview 34.1.1 Module Functionality FIGURE 34-1: CAN Buffers and Protocol Engine Block Diagram 34.2 CAN Modes of Operation 34.2.1 Configuration Mode 34.2.2 Disable/Sleep Mode 34.2.3 Normal Mode 34.2.4 Listen Only Mode 34.2.5 Loopback Mode 34.2.6 Error Recognition Mode 34.3 CAN Module Functional Modes 34.3.1 Mode 0 – Legacy Mode 34.3.2 Mode 1 – Enhanced Legacy Mode 34.3.3 Mode 2 – Enhanced Fifo Mode 34.4 CAN Message Buffers 34.4.1 Dedicated Transmit Buffers 34.4.2 Dedicated Receive Buffers 34.4.3 Programmable Transmit/ Receive Buffers 34.4.4 Programmable Auto-RTR Buffers 34.5 CAN Message Transmission 34.5.1 Initiating Transmission 34.5.2 Aborting Transmission 34.5.3 Transmit Priority FIGURE 34-2: Transmit Buffers 34.6 Message Reception 34.6.1 Receiving a Message 34.6.2 Receive Priority 34.6.3 Enhanced FIFO Mode 34.6.4 Time-Stamping 34.7 Message Acceptance Filters and Masks TABLE 34-1: Filter/Mask Truth Table FIGURE 34-3: Message Acceptance Mask and Filter Operation 34.8 Baud Rate Setting EQUATION 34-1: Nominal Bit Time EQUATION 34-2: Nominal Bit Time Duration EQUATION 34-3: Time Quantum FIGURE 34-4: Bit Time Partitioning 34.8.1 External Clock, Internal Clock and Measurable Jitter in HS-PLL Based Oscillators FIGURE 34-5: Effects of Phase Jitter on the Microcontroller Clock and CAN Bit Time EQUATION 34-4: Jitter and Total Frequency Error EQUATION 34-5: 16 MHz Clock from 4x PLL Jitter: EQUATION 34-6: Resultant Frequency Error: TABLE 34-2: Frequency Error from Jitter at Various PLL Generated Clock Speeds TABLE 34-3: Total Frequency Error at Various PLL Generated Clock Speeds (100 PPM Oscillator Drift, Including Error from Jitter) 34.8.2 Time Quanta EXAMPLE 34-1: Calculating Tq, Nominal Bit Rate and Nominal Bit Time 34.8.3 Synchronization Segment 34.8.4 Propagation Segment 34.8.5 Phase Buffer Segments 34.8.6 Sample Point 34.8.7 Information Processing Time 34.8.8 Clock Selection 34.9 Synchronization 34.9.1 Hard Synchronization 34.9.2 Resynchronization 34.9.3 Synchronization Rules FIGURE 34-6: Lengthening a Bit Period (Adding SJW to Phase Segment 1) FIGURE 34-7: Shortening a Bit Period (Subtracting SJW from PHASE SEGMENT 2) 34.10 Programming Time Segments 34.11 Oscillator Tolerance 34.12 Bit Timing Configuration Registers 34.12.1 BRGCON1 34.12.2 BRGCON2 34.12.3 BRGCON3 34.13 Error Detection 34.13.1 CRC Error 34.13.2 Acknowledge Error 34.13.3 Form Error 34.13.4 Bit Error 34.13.5 Stuff Bit Error 34.13.6 Error States 34.13.7 Error Modes and Error Counters FIGURE 34-8: Error Modes State Diagram 34.14 CAN Interrupts 34.14.1 Interrupt Code Bits 34.14.2 Transmit Interrupt 34.14.3 Receive Interrupt TABLE 34-4: Values for ICODE<2:0> 34.14.4 Message Error Interrupt 34.14.5 Bus Activity Wake-up Interrupt 34.14.6 Error Interrupt 34.14.6.1 Receiver Overflow 34.14.6.2 Receiver Warning 34.14.6.3 Transmitter Warning 34.14.6.4 Receiver Bus Passive 34.14.6.5 Transmitter Bus Passive 34.14.6.6 Bus-Off 34.15 CAN Module Registers 34.15.1 CAN Control and Status Registers Register 34-1: CANCON: CAN Control Register Register 34-2: CANSTAT: CAN Status Register EXAMPLE 34-2: Changing to Configuration Mode EXAMPLE 34-3: WIN and ICODE Bits Usage in Interrupt Service Routine to Access TX/RX Buffers EXAMPLE 34-2: WIN and ICODE Bits Usage in Interrupt Service Routine to Access TX/RX Buffers (Continued) Register 34-3: ECANCON: Enhanced CAN Control Register Register 34-4: COMSTAT: Communication Status Register 34.15.2 Dedicated CAN Transmit Buffer Registers Register 34-5: TXBnCON: Transmit Buffer n Control Registers [0 £ n £ 2] Register 34-6: TXBnSIDH: Transmit Buffer ‘n’ Standard Identifier Registers, High Byte [0 £ n £ 2] Register 34-7: TXBnSIDL: Transmit Buffer ‘n’ Standard Identifier Registers, Low Byte [0 £ n £ 2] Register 34-8: TXBnEIDH: Transmit Buffer ‘n’ Extended Identifier Registers, High Byte [0 £ n £ 2] Register 34-9: TXBnEIDL: Transmit Buffer ‘n’ Extended Identifier Registers, Low Byte [0 £ n £ 2] Register 34-10: TXBnDm: Transmit Buffer ‘n’ Data Field Byte ‘m’ Registers [0 £ n £ 2, 0 £ m £ 7] Register 34-11: TXBnDLC: Transmit Buffer ‘n’ Data Length Code Registers [0 £ n £ 2] Register 34-12: TXERRCNT: Transmit Error Count Register EXAMPLE 34-3: Transmitting a CAN Message Using Banked Method EXAMPLE 34-4: Transmitting a CAN Message Using WIN Bits 34.15.3 Dedicated CAN Receive Buffer Registers Register 34-13: RXB0CON: Receive Buffer 0 Control Register (Continued) Register 34-14: RXB1CON: Receive Buffer 1 Control Register (Continued) Register 34-15: RXBnSIDH: Receive Buffer ‘n’ Standard Identifier Registers, High Byte [0 £ n £ 1] Register 34-16: RXBnSIDL: Receive Buffer ‘n’ Standard Identifier Registers, Low Byte [0 £ n £ 1] Register 34-17: RXBnEIDH: Receive Buffer ‘n’ Extended Identifier Registers, High Byte [0 £ n £ 1] Register 34-18: RXBnEIDL: Receive Buffer ‘n’ Extended Identifier Registers, Low Byte [0 £ n £ 1] Register 34-19: RXBnDLC: Receive Buffer ‘n’ Data Length Code Registers [0 £ n £ 1] Register 34-20: RXBnDm: Receive Buffer ‘n’ Data Field Byte ‘m’ Registers [0 £ n £ 1, 0 £ m £ 7] Register 34-21: RXERRCNT: Receive Error Count Register EXAMPLE 34-5: Reading a CAN Message 34.15.3.1 Programmable TX/RX and Auto-RTR Buffers Register 34-22: BnCON: TX/RX Buffer ‘n’ Control Registers in Receive Mode [0 £ n £ 5, TXnEN (bsel0<n>) = 0](1) Register 34-23: BnCON: TX/RX Buffer ‘n’ Control Registers in Transmit Mode [0 £ n £ 5, TXnEN (bsel0<n>) = 1](1) Register 34-24: BnSIDH: TX/RX Buffer ‘n’ Standard Identifier Registers, High Byte in Receive Mode [0 £ n £ 5, TXnEN (BSEL0<n>) = 0](1) Register 34-25: BnSIDH: TX/RX Buffer ‘n’ Standard Identifier Registers, High Byte in Transmit Mode [0 £ n £ 5, TXnEN (BSEL0<n>) = 1](1) Register 34-26: BnSIDL: TX/RX Buffer ‘n’ Standard Identifier Registers, Low Byte in Receive Mode [0 £ n £ 5, TXnEN (bsel0<n>) = 0](1) Register 34-27: BnSIDL: TX/RX Buffer ‘n’ Standard Identifier Registers, Low Byte in Transmit Mode [0 £ n £ 5, TXnEN (bsel0<n>) = 1](1) Register 34-28: BnEIDH: TX/RX Buffer ‘n’ Extended Identifier Registers, High Byte in Receive Mode [0 £ n £ 5, TXnEN (BSEL0<n>) = 0](1) Register 34-29: BnEIDH: TX/RX Buffer ‘n’ Extended Identifier Registers, High Byte in Transmit Mode [0 £ n £ 5, TXnEN (BSEL0<n>) = 1](1) Register 34-30: BnEIDL: TX/RX Buffer ‘n’ Extended Identifier Registers, Low Byte in Receive Mode [0 £ n £ 5, TXnEN (BSEL<n>) = 0](1) Register 34-31: BnEIDL: TX/RX Buffer ‘n’ Extended Identifier Registers, Low Byte in Receive Mode [0 £ n £ 5, TXnEN (BSEL<n>) = 1](1) Register 34-32: BnDm: TX/RX Buffer ‘n’ Data Field Byte ‘m’ Registers in Receive Mode [0 £ n £ 5, 0 £ m £ 7, TXnEN (BSEL<n>) = 0](1) Register 34-33: BnDm: TX/RX Buffer ‘n’ Data Field Byte ‘m’ Registers in Transmit Mode [0 £ n £ 5, 0 £ m £ 7, TXnEN (BSEL<n>) = 1](1) Register 34-34: BnDLC: TX/RX Buffer ‘n’ Data Length Code Registers in Receive Mode [0 £ n £ 5, TXnEN (BSEL<n>) = 0](1) Register 34-35: BnDLC: TX/RX Buffer ‘n’ Data Length Code Registers in Transmit Mode [0 £ n £ 5, TXnEN (BSEL<n>) = 1](1) Register 34-36: BSEL0: Buffer Select Register 0(1) 34.15.3.2 Message Acceptance Filters and Masks Register 34-37: RXFnSIDH: Receive Acceptance Filter ‘n’ Standard Identifier Filter Registers, High Byte [0 £ n £ 15](1) Register 34-38: RXFnSIDL: Receive Acceptance Filter ‘n’ Standard Identifier Filter Registers, Low Byte [0 £ n £ 15](1) Register 34-39: RXFnEIDH: Receive Acceptance Filter ‘n’ Extended Identifier Registers, High Byte [0 £ n £ 15](1) Register 34-40: RXFnEIDL: Receive Acceptance Filter ‘n’ Extended Identifier Registers, Low Byte [0 £ n £ 15](1) Register 34-41: RXMnSIDH: Receive Acceptance Mask ‘n’ Standard Identifier Mask Registers, High Byte [0 £ n £ 1] Register 34-42: RXMnSIDL: Receive Acceptance Mask ‘n’ Standard Identifier Mask Registers, Low Byte [0 £ n £ 1] Register 34-43: RXMnEIDH: Receive Acceptance Mask ‘n’ Extended Identifier Mask Registers, High Byte [0 £ n £ 1] Register 34-44: RXMnEIDL: Receive Acceptance Mask ‘n’ Extended Identifier Mask Registers, Low Byte [0 £ n £ 1] Register 34-45: RXFCONn: Receive Filter Control Register ‘n’ [0 £ n £ 1](1) Register 34-46: SDFLC: Standard Data Bytes Filter Length Count Register(1) Register 34-47: RXFBCONn: Receive Filter Buffer Control Register ‘n’(1) Register 34-48: MSEL0: Mask Select Register 0(1) Register 34-49: MSEL1: Mask Select Register 1(1) Register 34-50: MSEL2: Mask Select Register 2(1) Register 34-51: MSEL3: Mask Select Register 3(1) 34.15.4 CAN Baud Rate Registers Register 34-52: BRGCON1: Baud Rate Control Register 1 Register 34-53: BRGCON2: Baud Rate Control Register 2 Register 34-54: BRGCON3: Baud Rate Control Register 3 34.15.5 CAN Module I/O Control Register Register 34-55: CIOCON: CAN I/O Control Register 34.15.6 CAN Interrupt Registers Register 34-56: PIR5: Peripheral Interrupt Request (Flag) Register 5 Register 34-57: PIE5: Peripheral Interrupt Enable Register 5 Register 34-58: IPR5: Peripheral Interrupt Priority Register 5 (Continued) Register 34-59: TXBIE: Transmit Buffers Interrupt Enable Register(1) Register 34-60: BIE0: Buffer Interrupt Enable Register 0(1) 35.0 Fixed Voltage Reference (FVR) 35.1 Independent Gain Amplifiers 35.2 FVR Stabilization Period FIGURE 35-1: Voltage Reference Block Diagram 35.3 Register Definitions: FVR Control Register 35-1: FVRCON: Fixed Voltage Reference Control Register TABLE 35-1: Summary of Registers Associated with Fixed Voltage Reference 36.0 Temperature Indicator Module 36.1 Module Operation FIGURE 36-1: Temperature Indicator Module Block Diagram 36.1.1 Minimum Operating Vdd TABLE 36-1: Recommended Vdd vs. Range 36.1.2 Temperature Indicator Range 36.2 Temperature Calculation EQUATION 36-1: Sensor Temperature 36.2.1 Calibration 36.2.1.1 Higher-Order Calibration 36.2.2 Temperature Resolution 36.3 ADC Acquisition Time TABLE 36-2: Summary of Registers Associated with the Temperature Indicator 37.0 Analog-to-Digital Converter with Computation (ADC2) Module FIGURE 37-1: ADC2 Block Diagram 37.1 ADC Configuration 37.1.1 Port Configuration 37.1.2 Channel Selection 37.1.3 ADC Voltage Reference 37.1.4 Conversion Clock TABLE 37-1: ADC Clock Period (Tad) Vs. Device Operating Frequencies(1,4) FIGURE 37-2: Analog-to-Digital Conversion Tad Cycles 37.1.5 Interrupts 37.1.6 Result Formatting FIGURE 37-3: 12-Bit ADC Conversion Result Format 37.2 ADC Operation 37.2.1 Starting a Conversion 37.2.2 Completion of a Conversion 37.2.3 ADC Operation During Sleep 37.2.4 External Trigger During Sleep 37.2.5 Auto-Conversion Trigger 37.2.6 ADC Conversion Procedure (Basic Mode) EXAMPLE 37-1: ADC Conversion 37.3 ADC Acquisition Requirements EQUATION 37-1: Acquisition Time Example FIGURE 37-4: Analog Input Model FIGURE 37-5: ADC Transfer Function 37.4 ADC Charge Pump 37.5 Capacitive Voltage Divider (CVD) Features FIGURE 37-6: Hardware Capacitive Voltage Divider Block Diagram 37.5.1 CVD Operation FIGURE 37-7: Differential CVD Measurement Waveform 37.5.2 PreCharge Control 37.5.3 Acquisition Control 37.5.4 Guard Ring Outputs FIGURE 37-8: Guard Ring Circuit FIGURE 37-9: Differential CVD with Guard Ring Output Waveform 37.5.5 Additional Sample and Hold Capacitance 37.6 Computation Operation FIGURE 37-10: Computational Features Simplified Block Diagram TABLE 37-2: Computation Modes 37.6.1 Digital Filter/Average TABLE 37-3: Low-pass Filter -3 dB Cut-off Frequency 37.6.2 Basic Mode 37.6.3 Accumulate Mode 37.6.4 Average Mode 37.6.5 Burst Average Mode 37.6.6 Low-pass Filter Mode 37.6.7 Threshold Comparison 37.6.8 Continuous Sampling mode 37.6.9 Double Sample Conversion 37.7 Register Definitions: ADC Control Register 37-1: ADCON0: ADC Control Register 0 Register 37-2: ADCON1: ADC Control Register 1 Register 37-3: ADCON2: ADC Control Register 2 Register 37-4: ADCON3: ADC Control Register 3 Register 37-5: ADSTAT: ADC Status Register Register 37-6: ADCLK: ADC Clock Selection Register Register 37-7: ADREF: ADC Reference Selection Register Register 37-8: ADPCH: ADC Positive Channel Selection Register Register 37-9: ADPREL: ADC Precharge Time Control Register (Low Byte) Register 37-10: ADPREH: ADC Precharge Time Control Register (High Byte) TABLE 37-4: Precharge Time Register 37-11: ADACQL: ADC Acquisition Time Control Register (Low Byte) Register 37-12: ADACQH: ADC Acquisition Time Control Register (High Byte) TABLE 37-5: Acquisition Time Register 37-13: ADCAP: ADC Additional Sample Capacitor Selection Register Register 37-14: ADRPT: ADC Repeat Setting Register Register 37-15: ADCNT: ADC Repeat Counter Register Register 37-16: ADFLTRH: ADC Filter High Byte Register Register 37-17: ADFLTRL: ADC Filter Low Byte Register Register 37-18: ADRESH: ADC Result Register High, FM = 0 Register 37-19: ADRESL: ADC Result Register Low, FM = 0 Register 37-20: ADRESH: ADC Result Register High, FM = 1 Register 37-21: ADRESL: ADC Result Register Low, FM = 1 Register 37-22: ADPREVH: ADC Previous Result Register Register 37-23: ADPREVL: ADC Previous Result Register Register 37-24: ADACCU: ADC Accumulator Register Upper Register 37-25: ADACCH: ADC Accumulator Register High Register 37-26: ADACCL: ADC Accumulator Register Low Register 37-27: ADSTPTH: ADC Threshold Setpoint Register High Register 37-28: ADSTPTL: ADC Threshold Setpoint Register Low Register 37-29: ADERRH: ADC Setpoint Error Register High Register 37-30: ADERRL: ADC Setpoint Error Low Byte Register Register 37-31: ADLTHH: ADC Lower Threshold High Byte Register Register 37-32: ADLTHL: ADC Lower Threshold Low Byte Register Register 37-33: ADUTHH: ADC Upper Threshold High Byte Register Register 37-34: ADUTHL: ADC Upper Threshold Low Byte Register Register 37-35: ADACT: ADC AUTO-Conversion Trigger Control Register Register 37-36: ADCP: ADC Charge Pump Control Register TABLE 37-6: Summary of Registers Associated with ADC 38.0 5-Bit Digital-to-Analog Converter (DAC) Module FIGURE 38-1: Digital-to-Analog Converter Block Diagram 38.1 Output Voltage Selection 38.2 Ratiometric Output Level 38.3 DAC Voltage Reference Output 38.4 Operation During Sleep 38.5 Effects of a Reset EQUATION 38-1: DAC Output Voltage 38.6 Register Definitions: DAC Control Register 38-1: DAC1CON0: DAC Control Register Register 38-2: DAC1CON1: DAC Data Register TABLE 38-1: Summary of Registers Associated with the DAC Module 39.0 Comparator Module 39.1 Comparator Overview FIGURE 39-1: Single Comparator FIGURE 39-2: Comparator Module Simplified Block Diagram 39.2 Comparator Control 39.2.1 Comparator Enable 39.2.2 Comparator Output 39.2.3 Comparator Output Polarity TABLE 39-1: Comparator Output State vs. Input Conditions 39.3 Comparator Hysteresis 39.3.1 Comparator Output Synchronization 39.4 Comparator Interrupt 39.5 Comparator Positive Input Selection 39.6 Comparator Negative Input Selection 39.7 Comparator Response Time 39.8 Analog Input Connection Considerations FIGURE 39-3: Analog Input Model 39.9 CWG1 Auto-Shutdown Source 39.10 ADC Auto-Trigger Source 39.11 TMR2/4/6 Reset 39.12 Operation in Sleep Mode 39.13 Register Definitions: Comparator Control TABLE 39-2: Register 39-1: CMxCON0: Comparator x Control Register 0 Register 39-2: CMxCON1: Comparator x Control Register 1 Register 39-3: CMxNCH: Comparator x Inverting Channel Select Register Register 39-4: CMxPCH: Comparator x Non-Inverting Channel Select Register Register 39-5: CMOUT: Comparator Output Register TABLE 39-3: Summary of Registers Associated with Comparator Module 40.0 High/Low-Voltage Detect (HLVD) 40.1 Operation FIGURE 40-1: HLVD Module Block Diagram 40.2 HLVD Setup 40.3 Current Consumption 40.4 HLVD Start-up Time FIGURE 40-2: Low-Voltage Detect Operation (INTL = 1) FIGURE 40-3: High-Voltage Detect Operation (INTH = 1) 40.5 Applications FIGURE 40-4: Typical Low-Voltage Detect Application 40.6 Operation During Sleep 40.7 Operation During Idle and Doze Modes 40.8 Operation During Freeze 40.9 Effects of a Reset 40.10 Register Definitions: HLVD Control TABLE 40-1: Register 40-1: HLVDCON0: High/Low-Voltage Detect Control Register 0 Register 40-2: HLVDCON1: Low-voltage Detect CONTROL REGISTER 1 TABLE 40-2: Summary of Registers Associated with High/Low-Voltage Detect Module 41.0 In-Circuit Serial Programming™ (ICSP™) 41.1 High-Voltage Programming Entry Mode 41.2 Low-Voltage Programming Entry Mode 41.3 Common Programming Interfaces FIGURE 41-1: ICD RJ-11 Style Connector Interface FIGURE 41-2: PICkit™ Programmer Style Connector Interface FIGURE 41-3: Typical Connection for ICSP™ Programming 42.0 Instruction Set Summary 42.1 Standard Instruction Set TABLE 42-1: Opcode Field Descriptions (Continued) FIGURE 42-1: General Format for Instructions (1/2) FIGURE 42-2: General Format for Instructions (2/2) TABLE 42-2: Instruction Set (Continued) 42.1.1 Standard Instruction Set 42.2 Extended Instruction Set 42.2.1 Extended Instruction Syntax TABLE 42-3: Extensions to the PIC18 Instruction Set 42.2.2 Extended Instruction Set 42.2.3 Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode 42.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands 42.2.4 Considerations when Enabling the Extended Instruction Set 42.2.5 Special Considerations with Microchip MPLAB® IDE Tools 43.0 Register Summary TABLE 43-1: Register File Summary for PIC18(L)F25/26K83 Devices (Continued) 44.0 Development Support 44.1 MPLAB X Integrated Development Environment Software 44.2 MPLAB XC Compilers 44.3 MPASM Assembler 44.4 MPLINK Object Linker/ MPLIB Object Librarian 44.5 MPLAB Assembler, Linker and Librarian for Various Device Families 44.6 MPLAB X SIM Software Simulator 44.7 MPLAB REAL ICE In-Circuit Emulator System 44.8 MPLAB ICD 3 In-Circuit Debugger System 44.9 PICkit 3 In-Circuit Debugger/ Programmer 44.10 MPLAB PM3 Device Programmer 44.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits 44.12 Third-Party Development Tools 45.0 Electrical Specifications 45.1 Absolute Maximum Ratings(†) 45.2 Standard Operating Conditions FIGURE 45-1: Voltage Frequency Graph, -40°C £ Ta £ +125°C, PIC18F25/26K83 Only FIGURE 45-2: Voltage Frequency Graph, -40°C £ Ta £ +125°C, PIC18LF25/26K83 Only 45.3 DC Characteristics TABLE 45-1: Supply Voltage FIGURE 45-3: POR and POR Rearm with Slow Rising Vdd TABLE 45-2: Supply Current (Idd)(1,2,4) TABLE 45-3: Power-Down Current (Ipd)(1,2) TABLE 45-4: I/O Ports TABLE 45-5: Memory Programming Specifications TABLE 45-6: Thermal Characteristics 45.4 AC Characteristics FIGURE 45-4: Load Conditions FIGURE 45-5: Clock Timing TABLE 45-7: External Clock/Oscillator Timing Requirements (Continued) TABLE 45-8: internal Oscillator Parameters(1) FIGURE 45-6: Precision Calibrated HFINTOSC Frequency Accuracy Over Device Vdd and Temperature TABLE 45-9: PLL Specifications FIGURE 45-7: CLKOUT and I/O Timing TABLE 45-10: I/O and CLKOUT Timing Specifications FIGURE 45-8: Reset, Watchdog Timer, Oscillator Start-up Timer and Power-up Timer Timing FIGURE 45-9: Brown-Out Reset Timing and Characteristics TABLE 45-11: Reset, WDT, Oscillator Start-up Timer, Power-up Timer, Brown-Out Reset and Low-Power Brown-Out Reset Specifications TABLE 45-12: High/Low-Voltage Detect Characteristics TABLE 45-13: Analog-to-Digital Converter (ADC) Accuracy Specifications(1,2): TABLE 45-14: Analog-to-Digital Converter (ADC) Conversion Timing Specifications FIGURE 45-10: ADC Conversion Timing (ADC Clock Fosc-based) FIGURE 45-11: ADC Conversion Timing (ADC Clock from ADCRC) TABLE 45-15: Comparator Specifications TABLE 45-16: 5-Bit DAC Specifications TABLE 45-17: Fixed Voltage Reference (FVR) Specifications TABLE 45-18: Zero Cross Detect (ZCD) Specifications FIGURE 45-12: Timer0 and Timer1 External Clock Timings TABLE 45-19: Timer0 and Timer1 External Clock Requirements FIGURE 45-13: Capture/Compare/PWM Timings (CCP) TABLE 45-20: Capture/Compare/PWM Requirements (CCP) FIGURE 45-14: SPI Master Mode Timing (CKE = 0, SMP = 0) FIGURE 45-15: SPI Master Mode Timing (CKE = 1, SMP = 1) FIGURE 45-16: SPI Slave Mode Timing (CKE = 0) FIGURE 45-17: SPI Slave Mode Timing (CKE = 1) TABLE 45-21: SPI Mode requirements (Master Mode) TABLE 45-22: SPI Mode requirements (Slave Mode) FIGURE 45-18: I2C Bus Start/Stop Bits Timing TABLE 45-23: I2C Bus Start/Stop Bits Requirements FIGURE 45-19: I2C Bus Data Timing TABLE 45-24: I2C Bus Data Requirements TABLE 45-25: Temperature Indicator Requirements 46.0 DC and AC Characteristics Graphs and Charts 47.0 Packaging Information 47.1 Package Details Revision History The Microchip Website Customer Change Notification Service Customer Support Product Identification System

Купить PIC18F25K83T-I/SO на РадиоЛоцман.Цены — от 170 до 18 220 ₽

Купить PIC18F25K83T-I/SO на РадиоЛоцман.Цены — от 170 до 18 220 ₽