Datasheet TB9053FTG,TB9054FTG - Preliminary (Toshiba) - 9

| Производитель | Toshiba |

| Описание | Bi-CMOS Linear Integrated Circuit, Silicon Monolithic |

| Страниц / Страница | 36 / 9 — Preliminary |

| Формат / Размер файла | PDF / 2.2 Мб |

| Язык документа | английский |

Preliminary

20 предложений от 5 поставщиков Motor / Motion / Ignition Controllers & Drivers H-BRIDGE MTR DRV 2ch 5A/1ch 10A SPI, AEC-Q100/Q006, Power QFN40 |

| TB9053FTG(EL)

| от 206 ₽ | |

| TB9053FTG(EL)

| от 224 ₽ | |

| TB9053FTG(EL)

Toshiba | 451 ₽ | |

| TB9053FTG(EL)

Toshiba | от 478 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

link to page 5

Preliminary

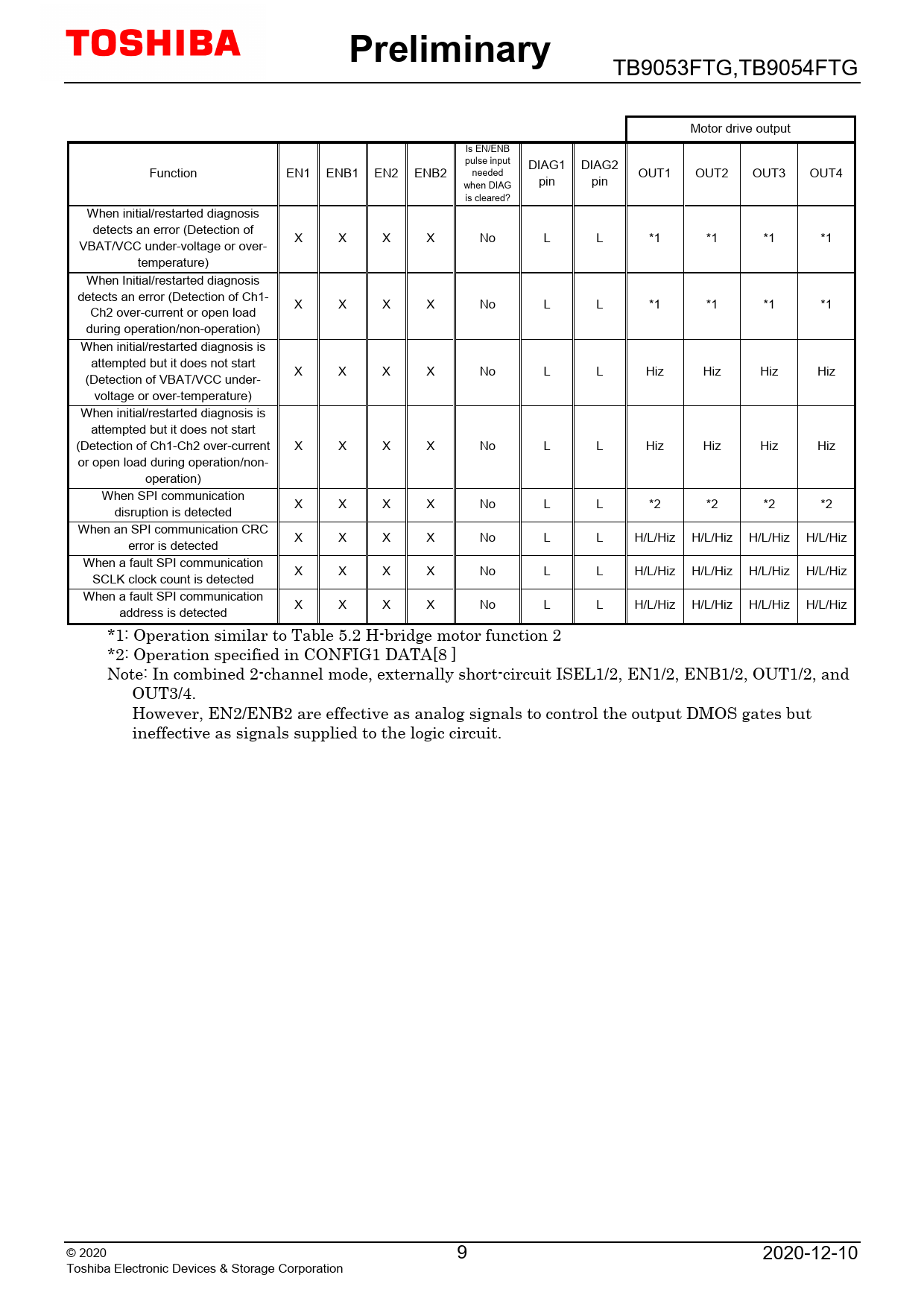

TB9053FTG,TB9054FTG Motor drive output Is EN/ENB pulse input Function EN1 ENB1 EN2 ENB2 DIAG1 DIAG2 needed when DIAG pin pin OUT1 OUT2 OUT3 OUT4 is cleared? When initial/restarted diagnosis detects an error (Detection of VBAT/VCC under-voltage or over- X X X X No L L *1 *1 *1 *1 temperature) When Initial/restarted diagnosis detects an error (Detection of Ch1- Ch2 over-current or open load X X X X No L L *1 *1 *1 *1 during operation/non-operation) When initial/restarted diagnosis is attempted but it does not start (Detection of VBAT/VCC under- X X X X No L L Hiz Hiz Hiz Hiz voltage or over-temperature) When initial/restarted diagnosis is attempted but it does not start (Detection of Ch1-Ch2 over-current X X X X No L L Hiz Hiz Hiz Hiz or open load during operation/non- operation) When SPI communication disruption is detected X X X X No L L *2 *2 *2 *2 When an SPI communication CRC error is detected X X X X No L L H/L/Hiz H/L/Hiz H/L/Hiz H/L/Hiz When a fault SPI communication SCLK clock count is detected X X X X No L L H/L/Hiz H/L/Hiz H/L/Hiz H/L/Hiz When a fault SPI communication address is detected X X X X No L L H/L/Hiz H/L/Hiz H/L/Hiz H/L/Hiz *1: Operation similar to Table 5.2 H-bridge motor function 2 *2: Operation specified in CONFIG1 DATA[8 ] Note: In combined 2-channel mode, externally short-circuit ISEL1/2, EN1/2, ENB1/2, OUT1/2, and OUT3/4. However, EN2/ENB2 are effective as analog signals to control the output DMOS gates but ineffective as signals supplied to the logic circuit. © 20 20 9 2020-12-10 Toshiba Electronic Devices & Storage Corporation

Купить TB9053FTG на РадиоЛоцман.Цены — от 206 до 516 ₽

Купить TB9053FTG на РадиоЛоцман.Цены — от 206 до 516 ₽