Datasheet SLG46826 (Dialog Semiconductor) - 4

| Производитель | Dialog Semiconductor |

| Описание | GreenPAK Programmable Mixed-signal Matrix with In System Programmability |

| Страниц / Страница | 188 / 4 — SLG46826. Figures. Datasheet. Revision 3.11. 10-Mar-2020 |

| Формат / Размер файла | PDF / 3.1 Мб |

| Язык документа | английский |

SLG46826. Figures. Datasheet. Revision 3.11. 10-Mar-2020

, Programmable Mixed Signal Matrix with ISP, 17 GPIOs, 19 LUTs, 1.8V to 5V, STQFN-20 (2mm x 3mm) |

| SLG46826VTR | 67 ₽ | |

| SLG46826VTR | 138 ₽ | |

| SLG46826VTR | по запросу | |

Модельный ряд для этого даташита

Текстовая версия документа

link to page 7 link to page 7 link to page 7 link to page 33 link to page 35 link to page 36 link to page 37 link to page 38 link to page 39 link to page 39 link to page 40 link to page 40 link to page 41 link to page 42 link to page 42 link to page 49 link to page 50 link to page 50 link to page 52 link to page 53 link to page 53 link to page 55 link to page 55 link to page 56 link to page 56 link to page 57 link to page 57 link to page 60 link to page 61 link to page 63 link to page 64 link to page 66 link to page 67 link to page 68 link to page 69 link to page 70 link to page 71 link to page 72 link to page 73 link to page 75 link to page 76 link to page 76 link to page 77 link to page 77 link to page 78 link to page 79 link to page 80 link to page 81 link to page 81 link to page 82 link to page 82 link to page 83 link to page 84 link to page 86 link to page 87 link to page 87 link to page 88 link to page 88

SLG46826

GreenPAK Programmable Mixed-Signal Matrix with In-System Programmability

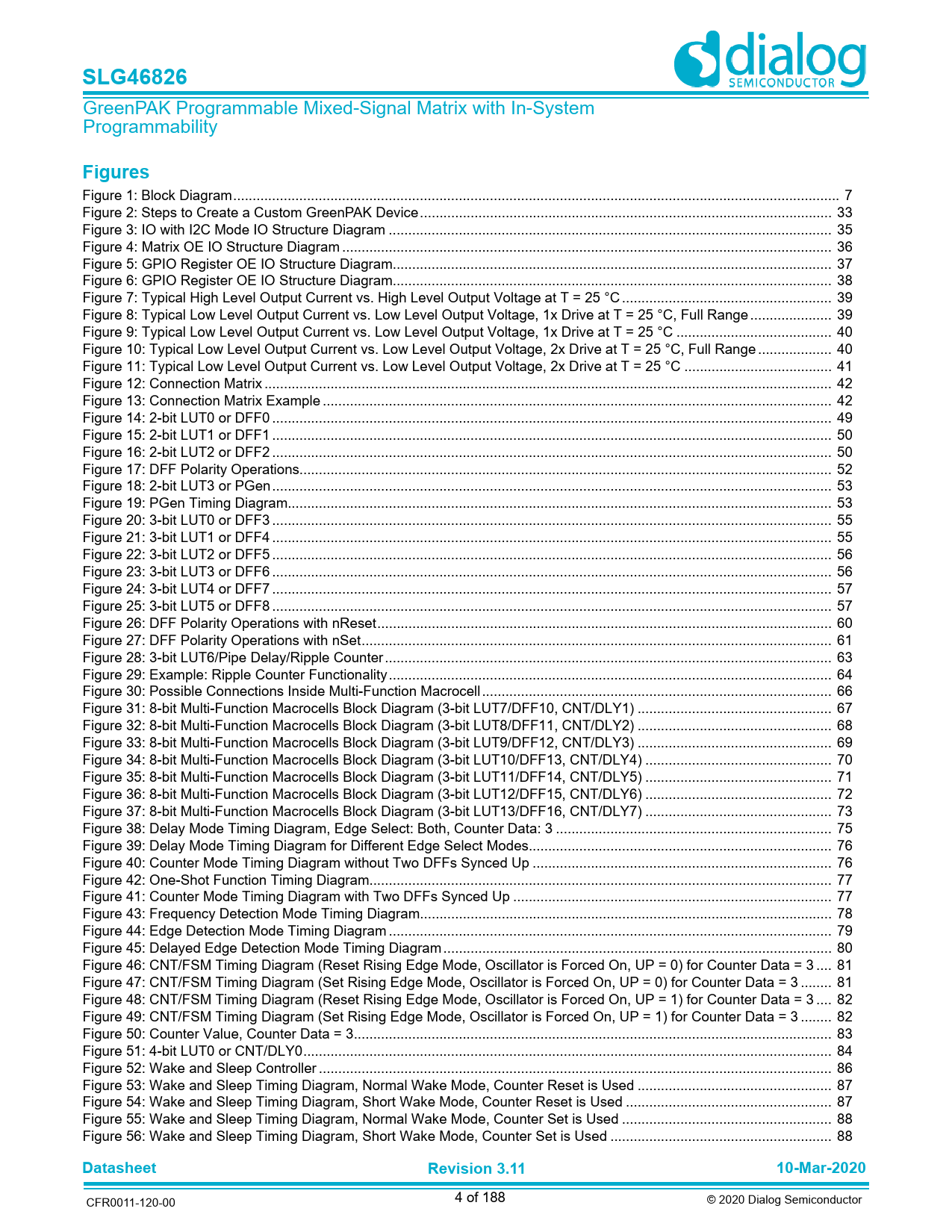

Figures

Figure 1: Block Diagram.. 7 Figure 2: Steps to Create a Custom GreenPAK Device.. 33 Figure 3: IO with I2C Mode IO Structure Diagram .. 35 Figure 4: Matrix OE IO Structure Diagram .. 36 Figure 5: GPIO Register OE IO Structure Diagram... 37 Figure 6: GPIO Register OE IO Structure Diagram... 38 Figure 7: Typical High Level Output Current vs. High Level Output Voltage at T = 25 °C .. 39 Figure 8: Typical Low Level Output Current vs. Low Level Output Voltage, 1x Drive at T = 25 °C, Full Range ... 39 Figure 9: Typical Low Level Output Current vs. Low Level Output Voltage, 1x Drive at T = 25 °C .. 40 Figure 10: Typical Low Level Output Current vs. Low Level Output Voltage, 2x Drive at T = 25 °C, Full Range ... 40 Figure 11: Typical Low Level Output Current vs. Low Level Output Voltage, 2x Drive at T = 25 °C .. 41 Figure 12: Connection Matrix .. 42 Figure 13: Connection Matrix Example ... 42 Figure 14: 2-bit LUT0 or DFF0 .. 49 Figure 15: 2-bit LUT1 or DFF1 .. 50 Figure 16: 2-bit LUT2 or DFF2 .. 50 Figure 17: DFF Polarity Operations... 52 Figure 18: 2-bit LUT3 or PGen.. 53 Figure 19: PGen Timing Diagram.. 53 Figure 20: 3-bit LUT0 or DFF3 .. 55 Figure 21: 3-bit LUT1 or DFF4 .. 55 Figure 22: 3-bit LUT2 or DFF5 .. 56 Figure 23: 3-bit LUT3 or DFF6 .. 56 Figure 24: 3-bit LUT4 or DFF7 .. 57 Figure 25: 3-bit LUT5 or DFF8 .. 57 Figure 26: DFF Polarity Operations with nReset... 60 Figure 27: DFF Polarity Operations with nSet... 61 Figure 28: 3-bit LUT6/Pipe Delay/Ripple Counter ... 63 Figure 29: Example: Ripple Counter Functionality .. 64 Figure 30: Possible Connections Inside Multi-Function Macrocell .. 66 Figure 31: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT7/DFF10, CNT/DLY1) .. 67 Figure 32: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT8/DFF11, CNT/DLY2) .. 68 Figure 33: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT9/DFF12, CNT/DLY3) .. 69 Figure 34: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT10/DFF13, CNT/DLY4) .. 70 Figure 35: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT11/DFF14, CNT/DLY5) .. 71 Figure 36: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT12/DFF15, CNT/DLY6) .. 72 Figure 37: 8-bit Multi-Function Macrocells Block Diagram (3-bit LUT13/DFF16, CNT/DLY7) .. 73 Figure 38: Delay Mode Timing Diagram, Edge Select: Both, Counter Data: 3 ... 75 Figure 39: Delay Mode Timing Diagram for Different Edge Select Modes.. 76 Figure 40: Counter Mode Timing Diagram without Two DFFs Synced Up ... 76 Figure 42: One-Shot Function Timing Diagram... 77 Figure 41: Counter Mode Timing Diagram with Two DFFs Synced Up .. 77 Figure 43: Frequency Detection Mode Timing Diagram.. 78 Figure 44: Edge Detection Mode Timing Diagram .. 79 Figure 45: Delayed Edge Detection Mode Timing Diagram .. 80 Figure 46: CNT/FSM Timing Diagram (Reset Rising Edge Mode, Oscillator is Forced On, UP = 0) for Counter Data = 3 .. 81 Figure 47: CNT/FSM Timing Diagram (Set Rising Edge Mode, Oscillator is Forced On, UP = 0) for Counter Data = 3 .. 81 Figure 48: CNT/FSM Timing Diagram (Reset Rising Edge Mode, Oscillator is Forced On, UP = 1) for Counter Data = 3 .. 82 Figure 49: CNT/FSM Timing Diagram (Set Rising Edge Mode, Oscillator is Forced On, UP = 1) for Counter Data = 3 .. 82 Figure 50: Counter Value, Counter Data = 3... 83 Figure 51: 4-bit LUT0 or CNT/DLY0.. 84 Figure 52: Wake and Sleep Controller .. 86 Figure 53: Wake and Sleep Timing Diagram, Normal Wake Mode, Counter Reset is Used .. 87 Figure 54: Wake and Sleep Timing Diagram, Short Wake Mode, Counter Reset is Used ... 87 Figure 55: Wake and Sleep Timing Diagram, Normal Wake Mode, Counter Set is Used .. 88 Figure 56: Wake and Sleep Timing Diagram, Short Wake Mode, Counter Set is Used ... 88

Datasheet Revision 3.11 10-Mar-2020

4 of 188 © 2020 Dialog Semiconductor CFR0011-120-00 Document Outline General Description Key Features Applications 1 Block Diagram 2 Pinout 2.1 Pin Configuration - STQFN- 20L 2.2 Pin Configuration - TSSOP-20L 3 Characteristics 3.1 Absolute Maximum Ratings 3.2 Electrostatic Discharge Ratings 3.3 Recommended Operating Conditions 3.4 Electrical Characteristics 3.5 Timing Characteristics 3.6 OSC Characteristics 3.6.1 OSC Specifications 3.6.2 OSC Power-On Delay 3.7 ACMP Specifications 3.8 Analog Temperature Sensor Characteristics 4 User Programmability 5 IO Pins 5.1 IO Pins 5.2 GPIO Pins 5.3 GPO Pins 5.4 GPI Pins 5.5 Pull-Up/Down Resistors 5.6 Fast Pull-up/down during Power-up 5.7 I2C Mode IO Structure (VDD or VDD2) 5.7.1 I2C Mode Structure (for SCL and SDA) 5.8 Matrix OE IO Structure (VDD or VDD2) 5.8.1 Matrix OE IO Structure (for IOs 1, 4, 5 with VDD, and IOs 8, 9, 10, 11, 12, 13, 14 with VDD2) 5.9 Register OE IO Structure (VDD or VDD2) 5.9.1 Register OE IO Structure (for IOs 0, 2, 3 with VDD) 5.10 Register OE IO Structure (VDD or VDD2) 5.10.1 Register OE IO Structure (for IO 6 with VDD, and IO 7 with VDD2) 5.11 IO Typical Performance 6 Connection Matrix 6.1 Matrix Input Table 6.2 Matrix Output Table 6.3 Connection Matrix Virtual Inputs 6.4 Connection Matrix Virtual Outputs 7 Combination Function Macrocells 7.1 2-Bit LUT or D Flip-Flop Macrocells 7.1.1 2-Bit LUT or D Flip-Flop Macrocell Used as 2-Bit LUT 7.1.2 Initial Polarity Operations 7.2 2-bit LUT or Programmable Pattern Generator 7.2.1 2-Bit LUT or PGen Macrocell Used as 2-Bit LUT 7.3 3-Bit LUT or D Flip-Flop with Set/Reset Macrocells 7.3.1 3-Bit LUT or D Flip-Flop Macrocells Used as 3-Bit LUTs 7.3.2 Initial Polarity Operations 7.4 3-Bit LUT or Pipe Delay/Ripple Counter Macrocell 7.4.1 3-Bit LUT or Pipe Delay Macrocells Used as 3-Bit LUT 8 Multi-Function Macrocells 8.1 3-Bit LUT or DFF/LATCH with 8-Bit Counter/Delay Macrocells 8.1.1 3-Bit LUT or 8-Bit CNT/DLY Block Diagrams 8.1.2 3-Bit LUT or CNT/DLYs Used as 3-Bit LUTs 8.2 CNT/DLY/FSM Timing Diagrams 8.2.1 Delay Mode CNT/DLY0 to CNT/DLY7 8.2.2 Count Mode (Count Data: 3), Counter Reset (Rising Edge Detect) CNT/DLY0 to CNT/DLY7 8.2.3 One-Shot Mode CNT/DLY0 to CNT/DLY7 8.2.4 Frequency Detection Mode CNT/DLY0 to CNT/DLY7 8.2.5 Edge Detection Mode CNT/DLY1 to CNT/DLY7 8.2.6 Delayed Edge Detection Mode CNT/DLY0 to CNT/DLY7 8.2.7 CNT/FSM Mode CNT/DLY0 8.2.8 Difference in Counter Value for Counter, Delay, One-Shot, and Frequency Detect Modes 8.3 4-Bit LUT or DFF/LATCH with 16-Bit Counter/Delay Macrocell 8.3.1 4-Bit LUT or 16-Bit CNT/DLY Block Diagram 8.3.2 4-Bit LUT or 16-Bit Counter/Delay Macrocells Used as 4-Bit LUTs 8.4 Wake and Sleep Controller 9 Analog Comparators 9.1 ACMP0H Block Diagram 9.2 ACMP1H Block Diagram 9.3 ACMP2L Block Diagram 9.4 ACMP3L Block Diagram 9.5 ACMP Typical Performance 10 Programmable Delay/Edge Detector 10.1 Programmable Delay Timing Diagram - Edge Detector Output 11 Additional Logic Function. Deglitch Filter 12 Voltage Reference 12.1 Voltage Reference Overview 12.2 Vref Selection Table 12.3 Vref Block Diagram 12.4 VREF Load Regulation 13 Clocking 13.1 Oscillator general description 13.2 Oscillator0 (2.048 kHz) 13.3 Oscillator1 (2.048 MHz) 13.4 Oscillator2 (25 MHz) 13.5 CNT/DLY Clock Scheme 13.6 External Clocking 13.6.1 IO0 Source for Oscillator0 (2.048 kHz) 13.6.2 IO10 Source for Oscillator1 (2.048 MHz) 13.6.3 IO8 Source for Oscillator2 (25 MHz) 13.7 Oscillators Power-On Delay 13.8 Oscillators Accuracy 14 Power-On Reset 14.1 General Operation 14.2 POR Sequence 14.3 Macrocells Output States During POR Sequence 14.3.1 Initialization 14.3.2 Power-Down 15 I2C Serial Communications Macrocell 15.1 I2C Serial Communications Macrocell Overview 15.2 I2C Serial Communications Device Addressing 15.3 I2C Serial General Timing 15.4 I2C Serial Communications Commands 15.4.1 Byte Write Command 15.4.2 Sequential Write Command 15.4.3 Current Address Read Command 15.4.4 Random Read Command 15.4.5 Sequential Read Command 15.4.6 I2C Serial Reset Command 15.5 Chip Configuration Data Protection 15.6 I2C Serial Command Register Map 15.7 I2C Additional Options 15.7.1 Reading Counter Data via I2C 15.7.2 I2C Expander 15.7.3 I2C Byte Write Bit Masking 16 Non-Volatile Memory 16.1 Serial NVM Write Operations 16.2 Serial NVM Read Operations 16.3 Serial NVM Erase Operations 16.4 Acknowledge Polling 16.5 Low power standby mode 16.6 Emulated EEPROM Write Protection 17 Analog Temperature Sensor 18 Register Definitions 18.1 Register Map 19 Package Top Marking System Definition 19.1 STQFN 20L 2 mm x 3 mm 0.4P FCD Package 19.2 TSSOP-20 20 Package Information 20.1 Package outlines for STQFN 20L 2 mm x 3 mm 0.4P FCD 20.2 Package outlines for TSSOP 20L 173 MIL Green 20.3 STQFN and TSSOP Handling 20.4 Soldering Information 21 Ordering Information 21.1 Tape and Reel Specifications 21.2 Carrier Tape Drawing and Dimensions 21.3 STQFN-20L 21.4 TSSOP-20L 22 Layout Guidelines 22.1 STQFN 20L 2 mm x 3 mm 0.4P FCD Package 22.2 TSSOP-20 Glossary Revision History