Datasheet MCP48FXBX4/8 (Microchip)

| Производитель | Microchip |

| Описание | 8/10/12-Bit Quad/Octal Voltage Output, 6 LSb INL Digital-to-Analog Converters with SPI Interface |

| Страниц / Страница | 112 / 1 — MCP48FXBX4/8. 8/10/12-Bit Quad/Octal Voltage Output, 6 LSb INL. … |

| Формат / Размер файла | PDF / 9.7 Мб |

| Язык документа | английский |

MCP48FXBX4/8. 8/10/12-Bit Quad/Octal Voltage Output, 6 LSb INL. Digital-to-Analog Converters with SPI Interface. Features

Модельный ряд для этого даташита

Текстовая версия документа

link to page 49 link to page 50

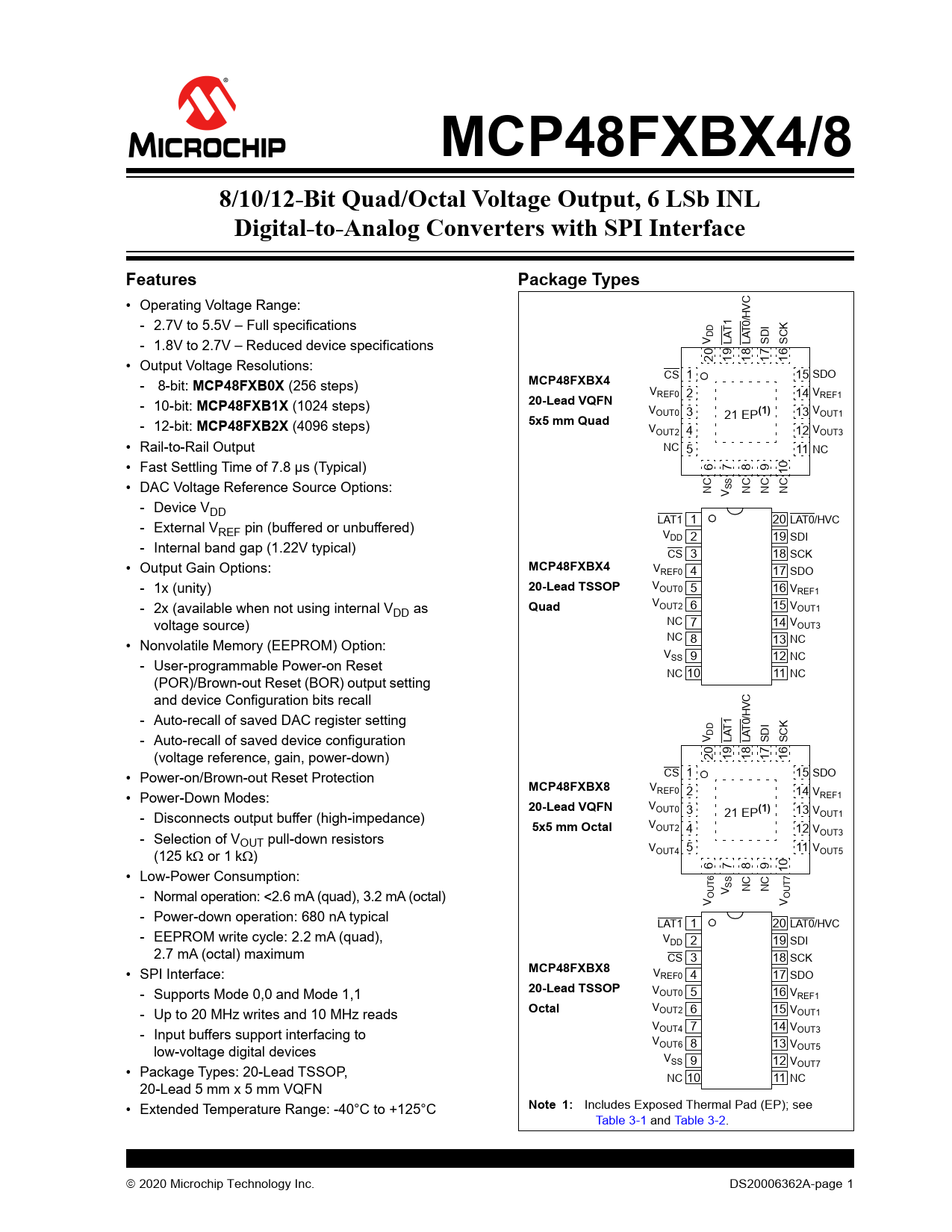

MCP48FXBX4/8 8/10/12-Bit Quad/Octal Voltage Output, 6 LSb INL Digital-to-Analog Converters with SPI Interface Features Package Types

• Operating Voltage Range: C V /H - 2.7V to 5.5V – Ful specifications 1 T T0 DD - 1.8V to 2.7V – Reduced device specifications V LA LA SDI SCK 20 19 18 17 16 • Output Voltage Resolutions: CS 1 15 SDO - 8-bit:

MCP48FXB0X

(256 steps)

MCP48FXBX4

VREF0 2 14 VREF1 - 10-bit:

MCP48FXB1X

(1024 steps)

20-Lead VQFN

VOUT0 3 21 EP

(1)

13 VOUT1 - 12-bit:

MCP48FXB2X

(4096 steps)

5x5 mm Quad

VOUT2 4 12 VOUT3 • Rail-to-Rail Output NC 5 11 NC • Fast Settling Time of 7.8 µs (Typical) 6 7 8 9 10 • DAC Voltage Reference Source Options: SS NC V NC NC NC - Device VDD LAT1 1 20 LAT0/HVC - Externa l VREF pin (buffered or unbuffered) VDD 2 19 SDI - Internal band gap (1.22V typical) CS 3 18 SCK • Output Gain Options:

MCP48FXBX4

VREF0 4 17 SDO - 1x (unity)

20-Lead TSSOP

VOUT0 5 16 VREF1 - 2x (available when not using internal V VOUT2 6 15 V DD as

Quad

OUT1 voltage source) NC 7 14 VOUT3 NC • Nonvolatile Memory (EEPROM) Option: 8 13 NC VSS 9 12 NC - User-programmable Power-on Reset NC 10 11 NC (POR)/Brown-out Reset (BOR) output setting and device Configuration bits recall C V - Auto-recall of saved DAC register setting /H T1 T0 DD - Auto-recall of saved device configuration V LA LA SDI SCK (voltage reference, gain, power-down) 20 19 18 17 16 • Power-on/Brown-out Reset Protection CS 1 15 SDO

MCP48FXBX8

V • Power-Down Modes: REF0 2 14 VREF1

20-Lead VQFN

VOUT0 3 13 V - Disconnects output buffer (high-impedance) 21 EP

(1)

OUT1

5x5 mm Octal

VOUT2 4 12 V - Selection of V OUT3 OUT pull-down resistors VOUT4 5 11 V (125 k or 1 k) OUT5 6 7 8 9 10 • Low-Power Consumption: 6 7 T SS NC NC T - Normal operation: <2.6 mA (quad), 3.2 mA (octal) V OU OU V V - Power-down operation: 680 nA typical LAT1 1 20 LAT0/HVC - EEPROM write cycle: 2.2 mA (quad), VDD 2 19 SDI 2.7 mA (octal) maximum CS 3 18 SCK • SPI Interface:

MCP48FXBX8

VREF0 4 17 SDO - Supports Mode 0,0 and Mode 1,1

20-Lead TSSOP

VOUT0 5 16 VREF1 - Up to 20 MHz writes and 10 MHz reads

Octal

VOUT2 6 15 VOUT1 VOUT4 7 14 V - Input buffers support interfacing to OUT3 VOUT6 8 13 V low-voltage digital devices OUT5 VSS 9 12 V • Package Types: 20-Lead TSSOP, OUT7 NC 10 11 NC 20-Lead 5 mm x 5 mm VQFN • Extended Temperature Range: -40°C to +125°C

Note 1:

Includes Exposed Thermal Pad (EP); see Table 3-1 and Table 3-2. 2020 Microchip Technology Inc. DS20006362A-page 1 Document Outline Features Package Types General Description Applications MCP48FXBX4/8 DAC Output Channel Block Diagram MCP48FXBX4 Block Diagram (Quad-Channel Output) MCP48FXBX8 Block Diagram (Octal-Channel Output) Device Features 1.0 Electrical Characteristics Absolute Maximum Ratings(†) DC Characteristics DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Characteristics (Continued) DC Notes: 1.1 Timing Waveforms and Requirements 1.1.1 Wiper Settling Time FIGURE 1-1: VOUT Settling Time Waveforms. TABLE 1-1: Wiper Settling Timing 1.1.2 Latch Pin (LAT) Timing FIGURE 1-2: LAT Pin Waveforms. TABLE 1-2: Lat Pin Timing 1.1.3 Reset and Power-Down Timing FIGURE 1-3: Power-on and Brown-out Reset Waveforms. FIGURE 1-4: SPI Power-Down Command Waveforms. TABLE 1-3: Reset and Power-Down Timing 1.2 SPI Mode Timing Waveforms and Requirements FIGURE 1-5: SPI Timing Waveforms – Mode 1,1. FIGURE 1-6: SPI Timing (Mode 0,0) Waveforms. TABLE 1-4: SPI Requirements (Mode 1,1) TABLE 1-5: SPI Requirements (Mode 0,0) Timing Table Notes: Temperature Specifications 2.0 Typical Performance Curves 2.1 Electrical Data FIGURE 2-1: Average Device Supply Current vs. FSCK Frequency, Voltage and Temperature – Active Interface, VRnB:VRnA = 00, (VDD Mode). FIGURE 2-2: Average Device Supply Current vs. FSCK Frequency, Voltage and Temperature – Active Interface, VRnB:VRnA = 01 (Band Gap Mode). FIGURE 2-3: Average Device Supply Current vs. FSCK Frequency, Voltage and Temperature – Active Interface, VRnB:VRnA = 11 (VREF Buffered Mode). FIGURE 2-4: Average Device Supply Current – Inactive Interface (SCK = VIH or VIL) vs. Voltage and Temperature, VRnB:VRnA = 00 (VDD Mode). FIGURE 2-5: Average Device Supply Current – Inactive Interface (SCK = VIH or VIL) vs. Voltage and Temperature, VRnB:VRnA = 01 (Band Gap Mode). FIGURE 2-6: Average Device Supply Current – Inactive Interface (SCK = VIH or VIL) vs. Voltage and Temperature, VRnB:VRnA = 11 (VREF Buffered Mode). FIGURE 2-7: Average Device Supply Current vs. FSCK Frequency, Voltage and Temperature – Active Interface, VRnB:VRnA = 10 (VREF Unbuffered Mode). FIGURE 2-8: Average Device Supply Active Current (IDDA) (at 5.5V and FSCK = 20 MHz) vs. Temperature and DAC Reference Voltage Mode. FIGURE 2-9: Average Device Supply Current – Inactive Interface (SCK = VIH or VIL) vs. Voltage and Temperature, VRnB:VRnA = 10 (VREF Unbuffered Mode). FIGURE 2-10: Power-Down Currents. 2.2 Linearity Data 2.2.1 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), VREF = VDD (VRnB:VRnA = 00), Gain = 1x, Code 100-4000 FIGURE 2-11: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-12: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-13: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-14: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-15: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-16: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.2 Integral Nonlinearity (INL) – MCP48FXB28 (12-Bit), VREF = VDD (VRnB:VRnA = 00), Gain = 1x, Code 64-4032 FIGURE 2-17: INL Error vs. DAC Code, T = 40°C, VDD = 5.5V. FIGURE 2-18: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-19: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-20: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-21: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-22: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.3 Differential Nonlinearity (DNL) – MCP48FXB28 (12-Bit), VREF = VDD (VRnB:VRnA = 00), Gain = 1x, Code 64-4032 FIGURE 2-23: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-24: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-25: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-26: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-27: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-28: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.4 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 2x, Code 100-4000 FIGURE 2-29: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-30: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-31: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-32: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-33: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-34: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.5 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 4x, Code 100-4000 FIGURE 2-35: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-36: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-37: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. 2.2.6 Integral Nonlinearity (INL) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 2x, Code 100-4000 FIGURE 2-38: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-39: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-40: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-41: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-42: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-43: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.7 Integral Nonlinearity (INL) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 4x, Code 100-4000 FIGURE 2-44: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-45: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-46: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. 2.2.8 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 2x, Code 100-4000 FIGURE 2-47: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-48: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-49: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-50: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-51: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-52: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.9 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), Band Gap Mode (VRnB:VRnA = 01), Gain = 4x, Code 100-4000 FIGURE 2-53: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-54: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-55: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. 2.2.10 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), External VREF Unbuffered Mode (VRnB:VRnA = 10), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-56: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-57: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C,VDD = 5.5V. FIGURE 2-58: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-59: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-60: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-61: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.11 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), External VREF Unbuffered Mode (VRnB:VRnA = 10), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-62: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-63: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C,VDD = 5.5V. FIGURE 2-64: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-65: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-66: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-67: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.12 Integral Nonlinearity Error (INL) – MCP48FXB28 (12-Bit), External VREF Mode, Unbuffered (VRnB:VRnA = 10), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-68: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-69: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-70: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-71: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-72: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-73: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.13 Integral Nonlinearity Error (INL) – MCP48FXB28 (12-Bit), External VREF Mode, Unbuffered (VRnB:VRnA = 10), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-74: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-75: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-76: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-77: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-78: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-79: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.14 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), External VREF Mode, Unbuffered (VRnB:VRnA = 10), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-80: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-81: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-82: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-83: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-84: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-85: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.15 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), External VREF Mode, Unbuffered (VRnB:VRnA = 10), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-86: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-87: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-88: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-89: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-90: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-91: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.16 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), External VREF Buffered Mode (VRnB:VRnA = 10), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-92: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-93: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C,VDD = 5.5V. FIGURE 2-94: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-95: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-96: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-97: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.17 Total Unadjusted Error (TUE) – MCP48FXB28 (12-Bit), External VREF Buffered Mode (VRnB:VRnA = 10), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-98: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-99: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C,VDD = 5.5V. FIGURE 2-100: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-101: Total Unadjusted Error (VOUT) vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-102: Total Unadjusted Error (VOUT) vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-103: Total Unadjusted Error (VOUT) vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.18 Integral Nonlinearity Error (INL) – MCP48FXB28 (12-Bit), External VREF Mode, Buffered (VRnB:VRnA = 11), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-104: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-105: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-106: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-107: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-108: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-109: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.19 Integral Nonlinearity Error (INL) – MCP48FXB28 (12-Bit), External VREF Mode, Buffered (VRnB:VRnA = 11), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-110: INL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-111: INL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-112: INL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-113: INL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-114: INL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-115: INL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.20 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), External VREF Mode, Buffered (VRnB:VRnA = 11), VREF = VDD, Gain = 1x, Code 100-4000 FIGURE 2-116: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-117: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-118: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-119: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-120: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-121: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 2.2.21 Differential Nonlinearity Error (DNL) – MCP48FXB28 (12-Bit), External VREF Mode, Buffered (VRnB:VRnA = 11), VREF = VDD/2, Gain = 2x, Code 100-4000 FIGURE 2-122: DNL Error vs. DAC Code, T = -40°C, VDD = 5.5V. FIGURE 2-123: DNL Error vs. DAC Code, T = +25°C, VDD = 5.5V. FIGURE 2-124: DNL Error vs. DAC Code, T = +125°C, VDD = 5.5V. FIGURE 2-125: DNL Error vs. DAC Code, T = -40°C, VDD = 2.7V. FIGURE 2-126: DNL Error vs. DAC Code, T = +25°C, VDD = 2.7V. FIGURE 2-127: DNL Error vs. DAC Code, T = +125°C, VDD = 2.7V. 3.0 Pin Descriptions TABLE 3-1: MCP48FXBX4 (Quad DAC) Pin Function Table TABLE 3-2: MCP48FXBX8 (Octal DAC) Pin Function Table 3.1 Positive Power Supply Input Pin (VDD) 3.2 Ground Pin (VSS) 3.3 Voltage Reference Pins (VREF) 3.4 Analog Output Voltage Pins (VOUTn) 3.5 Latch Pin (LAT)/High-Voltage Command Pin (HVC) 3.6 SPI – Chip Select Pin (CS) 3.7 SPI – Serial Data Input Pin (SDI) 3.8 SPI – Serial Data Output Pin (SDO) 3.9 SPI – Serial Clock Pin (SCK) 3.10 No Connect Pin (NC) 3.11 Exposed Pad Pin 4.0 General Description 4.1 Power-on Reset/Brown-out Reset (POR/BOR) 4.1.1 Power-on Reset 4.1.2 Brown-out Reset FIGURE 4-1: POR/BOR Operation. 4.2 Device Memory 4.2.1 Volatile Register Memory (RAM) 4.2.2 Nonvolatile Register Memory 4.2.3 Device Configuration Memory 4.2.4 Unimplemented Register Bits 4.2.5 Unimplemented (Reserved) Locations TABLE 4-1: MCP48FXBX4/8 Memory Map TABLE 4-2: Factory Default POR/BOR Values 4.2.6 WiperLock Technology TABLE 4-3: WiperLock™ Technology Configuration Bits – Functional Description 4.2.7 Device Registers 5.0 DAC Circuitry FIGURE 5-1: MCP48FXBX4/8 DAC Module Block Diagram. 5.1 Resistor Ladder FIGURE 5-2: Resistor Ladder Model. EQUATION 5-1: RS Calculation 5.2 Voltage Reference Selection FIGURE 5-3: Resistor Ladder Reference Voltage Selection Block Diagram. FIGURE 5-4: Reference Voltage Selection Implementation Block Diagram. 5.2.1 Buffered Mode 5.2.2 Unbuffered Mode 5.2.3 Band Gap Mode 5.3 Internal Band Gap TABLE 5-1: VOUT Using Band Gap 5.4 Output Buffer/VOUT Operation FIGURE 5-5: Output Driver Block Diagram. 5.4.1 Programmable Gain 5.4.2 Output Voltage EQUATION 5-2: Calculating Output Voltage (VOUT) 5.4.3 Step Voltage (VS) EQUATION 5-3: VS Calculation TABLE 5-2: Theoretical Step Voltage (VS)(1) 5.4.4 Output Slew Rate FIGURE 5-6: VOUT Pin Slew Rate. 5.4.5 Driving Resistive and Capacitive Loads FIGURE 5-7: Circuit to Stabilize the Output Buffer for Large Capacitive Loads (CL). 5.5 Power-Down Operation FIGURE 5-8: VOUT Power-Down Block Diagram. TABLE 5-3: Power-Down Bits and Output Resistive Load TABLE 5-4: DAC Current Sources 5.5.1 Exiting Power-Down 5.6 DAC Registers, Configuration Bits and Status Bits 5.7 Latch Pins (LATn) FIGURE 5-9: LAT and DAC Interaction. FIGURE 5-10: LAT Pin Operation Example. TABLE 5-5: DAC Input Code vs. Calculated Analog Output (VOUT) (VDD = 5.0V) 6.0 SPI Serial Interface Module 6.1 Overview 6.2 SPI Serial Interface FIGURE 6-1: Typical SPI Interface Block Diagram. 6.2.1 SPI Modes 6.3 Interface Pins (CS, SCK, SDI, SDO and LAT/HVC) 6.3.1 Serial Data In (SDI) 6.3.2 Serial Data Out (SDO) 6.3.3 Serial Clock (SCK) (SPI Frequency of Operation) TABLE 6-1: SCK Frequency 6.3.4 CS Signal 6.3.5 HVC Signal 6.4 Communication Data Rates 6.5 POR/BOR 7.0 SPI Device Commands TABLE 7-1: Command Bits Overview FIGURE 7-1: 8-Bit SPI Command Format. 7.1 Command Byte 7.2 Data Bytes FIGURE 7-2: 24-Bit SPI Command Format. TABLE 7-2: SPI Commands – Overview and Command Rate 7.3 Continuous Commands 7.4 Commands to Modify the Device Configuration Bits 7.5 High-Voltage Command (HVC) Signal 7.6 Error Condition 7.6.1 Aborting a Transmission 7.7 WRITE Command (Normal and High Voltage) 7.7.1 Single Write to Volatile Memory 7.7.2 Single Write to Nonvolatile Memory 7.7.3 Continuous Writes to Volatile Memory TABLE 7-3: Volatile Memory Addresses 7.7.4 Continuous Writes to Nonvolatile Memory 7.7.5 High-Voltage Command (HVC) Signal FIGURE 7-3: Write Single Memory Location Command – SDI and SDO States.(1) FIGURE 7-4: 24-Bit WRITE Command (C1:C0 = 00) – SPI Waveform (Mode 1,1). FIGURE 7-5: 24-Bit WRITE Command (C1:C0 = 00) – SPI Waveform (Mode 0,0). FIGURE 7-6: Continuous WRITE Commands (Volatile Memory Only). 7.8 READ Command (Normal and High Voltage) 7.8.1 LAT Pin Interaction 7.8.2 Single Read FIGURE 7-7: READ Command – SDI and SDO States. 7.8.3 Continuous Reads FIGURE 7-8: READ Command – Continuous Read Sequence. FIGURE 7-9: 24-Bit READ Command (C1:C0 = 11) – SPI Waveforms (Mode 1,1). FIGURE 7-10: 24-Bit READ Command (C1:C0 = 11) – SPI Waveforms (Mode 0,0). 7.9 Enable Configuration Bit (High Voltage) FIGURE 7-11: Enable Command Sequence. FIGURE 7-12: 8-Bit Enable Command (C1:C0 = 10) – SPI Waveforms (Mode 1,1). FIGURE 7-13: 8-Bit Enable Command (C1:C0 = 10) – SPI Waveforms (Mode 0,0). 7.10 Disable Configuration Bit (High Voltage) FIGURE 7-14: Disable Command Sequence. FIGURE 7-15: 8-Bit Disable Command (C1:C0 = 01) – SPI Waveforms (Mode 1,1). FIGURE 7-16: 8-Bit Disable Command (C1:C0 = 01) – SPI Waveforms (Mode 0,0). 8.0 Applications Information 8.1 Power Supply Considerations FIGURE 8-1: Example Circuit. 8.2 Layout Considerations TABLE 8-1: Package Footprint(1) 9.0 Development Support 9.1 Development Tools 9.2 Technical Documentation TABLE 9-1: Development Tools(1) TABLE 9-2: Technical Documentation FIGURE 9-1: MCP48FXBX4/8 Evaluation Board Circuit Using TSSOP20EV. 10.0 Packaging Information 10.1 Package Marking Information Appendix A: Revision History Revision A (May 2020) Appendix B: Terminology B.1 Resolution B.2 Least Significant Bit (LSb) EQUATION B-1: LSb Voltage Calculation B.3 Monotonic Operation FIGURE B-1: VW (VOUT). B.4 Full-Scale Error (EFS) EQUATION B-2: Full-Scale Error B.5 Zero-Scale Error (EZS) EQUATION B-3: Zero-Scale Error B.6 Total Unadjusted Error (ET) EQUATION B-4: Total Unadjusted Error Calculation B.7 Offset Error (EOS) FIGURE B-2: Offset Error and Zero-Scale Error. B.8 Offset Error Drift (EOSD) B.9 Gain Error (EG) FIGURE B-3: Gain Error and Full-Scale Error Example. EQUATION B-5: Example Gain Error B.10 Gain Error Drift (EGD) B.11 Integral Nonlinearity (INL) EQUATION B-6: INL Error FIGURE B-4: INL Accuracy. B.12 Differential Nonlinearity (DNL) EQUATION B-7: DNL Error FIGURE B-5: DNL Accuracy. B.13 Settling Time B.14 Major Code Transition Glitch B.15 Digital Feedthrough B.16 -3 dB Bandwidth B.17 Power Supply Sensitivity (PSS) EQUATION B-8: PSS Calculation B.18 Power Supply Rejection Ratio (PSRR) B.19 VOUT Temperature Coefficient B.20 Absolute Temperature Coefficient B.21 Noise Spectral Density Product Identification System Worldwide Sales and Service

Купить MCP48FVB04 на РадиоЛоцман.Цены — от 76 до 665 ₽

Купить MCP48FVB04 на РадиоЛоцман.Цены — от 76 до 665 ₽