| Производитель | Analog Devices |

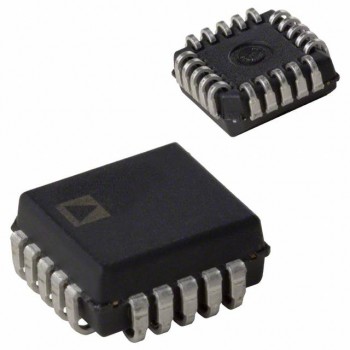

| Описание | Dual Ultrafast Voltage Comparator |

| Страниц / Страница | 16 / 8 — LATCH ENABLE. 50%. tPL. DIFFERENTIAL. VIN. VREF ± VOS. INPUT VOLTAGE. … |

| Формат / Размер файла | PDF / 207 Кб |

| Язык документа | английский |

Купить ADCMP565BPZ на РадиоЛоцман.Цены — от 133 до 2 033 ₽ Купить ADCMP565BPZ на РадиоЛоцман.Цены — от 133 до 2 033 ₽37 предложений от 19 поставщиков Микросхема Компаратор, ANALOG DEVICES ADCMP565BPZ Analog Comparator, Dual, High Speed, 2, 300 ps, 4.75V to 5.25V, -4.96V to -5.45V, PLCC, 20Pins... | |||

| ADCMP565BPZ Analog Devices | 133 ₽ | ||

| ADCMP565BPZ Analog Devices | от 283 ₽ | ||

| ADCMP565BPZ Analog Devices | от 334 ₽ | ||

| ADCMP565BPZ Analog Devices | по запросу | ||