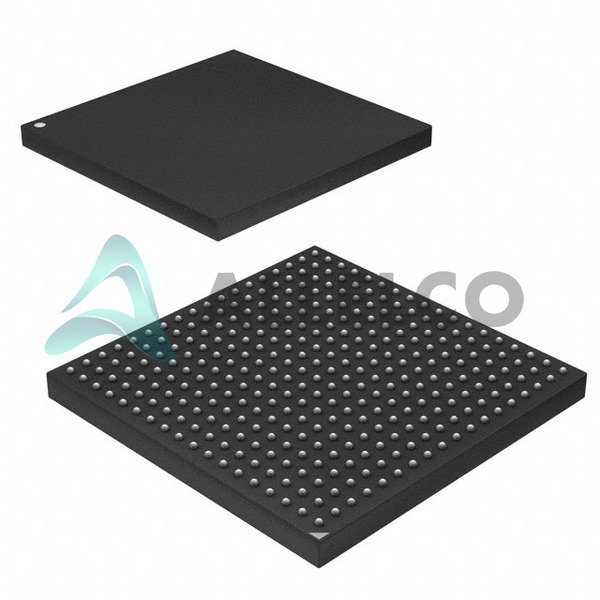

Datasheet VSC7430 (Microchip) - 7 Производитель Microchip Описание 6-Port Carrier Ethernet Switch with ViSAA, VeriTime, and Gigabit Ethernet PHYs Страниц / Страница 527 / 7 — link. to. page. 391. link. to. page. 391. link. to. page. 392. link. to. … Формат / Размер файла PDF / 7.8 Мб Язык документа

link. to. page. 391. link. to. page. 391. link. to. page. 392. link. to. page. 392. link. to. page. 394. link. to. page. 394. link. to. page. 395. link. to. page. 396. link. to. page. 396

Модельный ряд для этого даташита Текстовая версия документа link to page 391 link to page 391 link to page 392 link to page 392 link to page 394 link to page 394 link to page 395 link to page 396 link to page 396 link to page 396 link to page 397 link to page 397 link to page 397 link to page 398 link to page 399 link to page 399 link to page 400 link to page 400 link to page 400 link to page 401 link to page 401 link to page 402 link to page 403 link to page 403 link to page 406 link to page 409 link to page 409 link to page 409 link to page 409 link to page 411 link to page 412 link to page 412 link to page 413 link to page 413 link to page 415 link to page 415 link to page 416 link to page 417 link to page 417 link to page 417 link to page 417 link to page 417 link to page 417 link to page 418 link to page 418 link to page 420 link to page 422 link to page 423 link to page 424 link to page 425 link to page 425 link to page 427 link to page 427 link to page 428 link to page 429 3.31.5 Time of Day Time Stamping . 372 3.31.6 Time of Day Generation . 372 3.31.7 Multiple PTP Time Domains . 373 3.31.8 Register Interface to 1588 Functions . 373 3.31.9 Configuring I/O Delays . 375 3.32 VRAP Engine . 375 3.32.1 VRAP Request Frame Format . 376 3.32.2 VRAP Response Frame Format . 377 3.32.3 VRAP Header Format . 377 3.32.4 VRAP READ Command . 377 3.32.5 VRAP READ-MODIFY-WRITE Command . 378 3.32.6 VRAP IDLE Command . 378 3.32.7 VRAP PAUSE Command . 378 3.33 Energy Efficient Ethernet . 379 3.34 CPU Injection and Extraction . 380 3.34.1 Frame Injection . 380 3.34.2 Frame Extraction . 381 3.34.3 Forwarding to CPU . 381 3.34.4 Automatic Frame Injection (AFI) . 381 3.35 Priority-Based Flow Control (PFC) . 382 3.35.1 PFC Pause Frame Generation . 382 3.35.2 PFC Frame Reception . 383 3.36 Protection Switching . 384 3.36.1 Ethernet Ring Protection Switching . 384 3.36.2 Linear Protection Switching for E-Line Services . 387 3.36.3 Link Aggregation . 390 3.36.4 Port Protection Switching . 390 3.37 Clocking and Reset . 390 3.37.1 Pin Strapping . 390 4 VCore-III System and CPU Interfaces . 392 4.1 VCore-III Configurations . 393 4.2 Clocking and Reset . 393 4.2.1 Watchdog Timer . 394 4.3 Shared Bus . 394 4.3.1 VCore-III Shared Bus Arbitration . 396 4.3.2 Chip Register Region . 396 4.3.3 SI Flash Region . 397 4.3.4 DDR3/DDR3L Region . 398 4.3.5 PCIe Region . 398 4.4 VCore-III CPU . 398 4.4.1 Little Endian and Big Endian Support . 398 4.4.2 Software Debug and Development . 398 4.5 External CPU Support . 398 4.5.1 Register Access and Multimaster Systems . 399 4.5.2 Serial Interface in Slave Mode . 399 4.5.3 MIIM Interface in Slave Mode . 401 4.5.4 Access to the VCore Shared Bus . 403 4.5.5 Mailbox and Semaphores . 404 4.6 PCIe Endpoint Controller . 405 4.6.1 Accessing Endpoint Registers . 406 4.6.2 Enabling the Endpoint . 406 4.6.3 Base Address Registers Inbound Requests . 408 4.6.4 Outbound Interrupts . 408 4.6.5 Outbound Access . 409 4.6.6 Power Management . 410 VMDS-10480 VSC7430 Datasheet Revision 4.1 vii Document Outline 1 Revision History 1.1 Revision 4.1 1.2 Revision 4.0 2 Product Overview 2.1 General Features 2.1.1 Layer 2 and Layer 3 Forwarding 2.1.2 Carrier Ethernet Support 2.1.3 Timing and Synchronization 2.1.4 Quality of Service (QoS) 2.1.5 Security 2.1.6 Management 2.1.7 Product Parameters 2.2 Applications 2.2.1 Wireless Backhaul 2.2.2 Network Interface Device (NID) 2.2.3 Carrier Ethernet Switch with MPLS-TP 2.2.4 Small Cell Application 3 Functional Descriptions 3.1 Register Notations 3.2 Functional Overview 3.2.1 Frame Arrival in Ports and Port Modules 3.2.2 Basic Classification 3.2.3 Virtualized Service Aware Architecture (ViSAA™) 3.2.4 Security and Control Protocol Classification 3.2.5 Policing 3.2.6 Layer 2 Forwarding 3.2.7 Layer 3 Forwarding 3.2.8 Shared Queue System and Hierarchical Scheduler 3.2.9 Rewriter and Frame Departure 3.2.10 CPU Port Module 3.2.11 Synchronous Ethernet and Precision Time Protocol (PTP) 3.2.12 Ethernet and MPLS OAM 3.2.13 CPU Subsystem 3.3 Frame Headers 3.3.1 Internal Frame Header Placement 3.3.2 Internal Frame Header Layout 3.3.3 VStaX Header 3.4 Port Numbering and Mappings 3.4.1 Supported SerDes Interfaces 3.4.2 Dual-Media Mode 3.4.3 Logical Port Numbers 3.5 SERDES1G 3.6 SERDES6G 3.7 Copper Transceivers 3.7.1 Register Access 3.7.2 Cat5 Twisted Pair Media Interface 3.7.3 Wake-On-LAN and SecureOn 3.7.4 Ethernet Inline Powered Devices 3.7.5 IEEE 802.3af PoE Support 3.7.6 ActiPHY™ Power Management 3.7.7 Testing Features 3.7.8 VeriPHY™ Cable Diagnostics 3.8 DEV1G and DEV2G5 Port Modules 3.8.1 MAC 3.8.2 Half-Duplex Mode 3.8.3 Physical Coding Sublayer (PCS) 3.8.4 Port Statistics 3.9 Assembler 3.9.1 Setting Up a Port in the Assembler 3.9.2 Setting Up a Port for Frame Injection 3.9.3 Setting Up MAC Control Sublayer PAUSE Frame Detection 3.9.4 Setting Up PFC 3.9.5 Setting Up Assembler Port Statistics 3.9.6 Setting Up the Loopback Path 3.10 Versatile Content-Aware Processor (VCAP) 3.10.1 Configuring VCAP 3.10.2 Wide VCAP Entries and Actions 3.10.3 Individual VCAPs 3.10.4 VCAP Programming Examples 3.11 Pipeline Points 3.11.1 Pipeline Definitions 3.12 Analyzer 3.12.1 Initializing the Analyzer 3.13 VCAP CLM Keys and Actions 3.13.1 Keys Overview 3.13.2 VCAP CLM X1 Key Details 3.13.3 VCAP CLM X2 Key Details 3.13.4 VCAP CLM X4 Key Details 3.13.5 VCAP CLM X8 Key Details 3.13.6 VCAP CLM X16 Key Details 3.13.7 VCAP CLM Actions 3.14 Analyzer Classifier 3.14.1 Basic Classifier 3.14.2 VCAP CLM Processing 3.14.3 QoS Mapping Table 3.14.4 Ingress Protection Table (IPT) 3.14.5 Layer 2 Control Protocol Processing 3.14.6 Y.1731 Ethernet MIP 3.14.7 Analyzer Classifier Diagnostics 3.15 VLAN and MSTP 3.15.1 Private VLAN 3.15.2 VLAN Pseudo Code 3.16 VCAP LPM: Keys and Action 3.16.1 VCAP LPM SGL_IP4 Key Details 3.16.2 VCAP LPM DBL_IP4 Key Details 3.16.3 VCAP LPM SGL_IP6 Key Details 3.16.4 VCAP LPM DBL_IP6 Key Details 3.16.5 VCAP LPM Actions 3.17 IP Processing 3.17.1 IP Source/Destination Guard 3.17.2 IP Routing 3.17.3 Statistics 3.17.4 IGMP/MLD Snooping Switch 3.18 VCAP IS2 Keys and Actions 3.18.1 VCAP IS2 Keys 3.18.2 VCAP IS2 Actions 3.19 Analyzer Access Control Lists 3.19.1 VCAP IS2 3.19.2 Analyzer Access Control List Frame Rewriting 3.20 Analyzer Layer 2 Forwarding and Learning 3.20.1 Analyzer MAC Table 3.20.2 MAC Table Updates 3.20.3 CPU Access to MAC Table 3.20.4 SCAN Command 3.20.5 Forwarding Lookups 3.20.6 Source Check and Automated Learning 3.20.7 Automated Aging (AUTOAGE) 3.20.8 Service Handling 3.20.9 Interrupt Handling 3.21 Analyzer Access Control Forwarding, Policing, and Statistics 3.21.1 Mask Handling 3.21.2 Policing 3.21.3 Analyzer Statistics 3.21.4 Analyzer sFlow Sampling 3.21.5 Mirroring 3.22 Versatile OAM Processor (VOP) 3.22.1 VOP Blocks 3.22.2 Versatile OAM Endpoint (VOE) Functions 3.22.3 Supported OAM PDUs 3.22.4 VOE Locations 3.23 VOP Common Functions 3.23.1 Accessing the VOP 3.23.2 VOE Hierarchy 3.23.3 VOE Frame Injection and Extraction 3.23.4 Loss Measurement (LM) Counters 3.23.5 Port Count-All Rx/Tx Counters 3.23.6 Basic VOP Configuration 3.23.7 Loss of Continuity Controller 3.23.8 Hit-Me-Once Controller 3.23.9 Interrupt Controller 3.23.10 Ethernet Configuration 3.23.11 MPLS-TP Configuration 3.24 VOE: Ethernet OAM 3.24.1 Ethernet VOE Functions 3.24.2 Continuity Check Messages (CCM) 3.24.3 VOE LOCC Configuration 3.24.4 Test Frames (TST) 3.24.5 Loopback Frames (LBM/LBR) 3.24.6 Frame Loss Measurement, Single-Ended 3.24.7 Frame Loss Measurement, Dual-Ended 3.24.8 Synthetic Loss Measurement 3.24.9 Synthetic Loss Measurement, Single-Ended 3.24.10 Synthetic Loss Measurement, Dual-Ended 3.24.11 Delay Measurement 3.24.12 Single-Ended Delay Measurement (SE-DM: DMM/DMR) 3.24.13 Dual-Ended Delay Measurement (DE-DM: 1DM) 3.24.14 Generic/Unknown Opcodes 3.24.15 Link Trace 3.24.16 Non-OAM Sequence Numbering 3.24.17 Service Activation Test (SAT) 3.24.18 G.8113.1 Specific Functions 3.25 VOE: MPLS-TP OAM 3.25.1 MPLS-TP VOE Functions 3.25.2 Bidirectional Forwarding Detection (BFD) Implementation 3.25.3 BFD Functional Overview 3.25.4 BFD Configuration 3.25.5 BFD Frame Reception 3.25.6 BFD Frame Transmission 3.25.7 BFD VOE Functions 3.25.8 BFD Statistics 3.26 Shared Queue System and Hierarchical Scheduler 3.26.1 Analyzer Result 3.26.2 Buffer Control 3.26.3 Forwarding 3.26.4 Congestion Control 3.26.5 Queue Mapping 3.26.6 Queue Congestion Control 3.26.7 Scheduling 3.26.8 Queue System Initialization 3.26.9 Miscellaneous Features 3.27 Automatic Frame Injector 3.27.1 Injection Tables 3.27.2 Frame Table 3.27.3 Delay Triggered Injection 3.27.4 Timer Triggered Injection 3.27.5 Injection Queues 3.27.6 Adding Injection Frame 3.27.7 Starting Injection 3.27.8 Stopping Injection 3.27.9 Removing Injection Frames 3.27.10 Port Parameters 3.28 Rewriter 3.28.1 Rewriter Operation 3.28.2 Supported Ports 3.28.3 Supported Frame Formats 3.28.4 Rewriter Initialization 3.28.5 VCAP_ES0 Lookup 3.28.6 Mapping Tables 3.28.7 VLAN Editing 3.28.8 DSCP Remarking 3.28.9 VStaX Header Insertion 3.28.10 Forwarding to GCPU 3.28.11 Layer 3 Routing 3.28.12 OAM Frame Handling 3.28.13 Mirror Frames 3.28.14 MPLS Editing 3.28.15 Internal Frame Header Insertion 3.28.16 Frame Injection from Internal CPU 3.29 Disassembler 3.29.1 Setting Up Ports 3.29.2 Maintaining the Cell Buffer 3.29.3 Setting Up MAC Control Sublayer PAUSE Function 3.29.4 Setting up Flow Control in Half-Duplex Mode 3.29.5 Setting Up Frame Aging 3.29.6 Setting Up Transmit Data Rate Limiting 3.29.7 Error Detection 3.30 Layer 1 Timing 3.31 Hardware Time Stamping 3.31.1 One-Step Functions 3.31.2 Calculation Overview 3.31.3 Detecting Calculation Issues 3.31.4 Two-Step Functions 3.31.5 Time of Day Time Stamping 3.31.6 Time of Day Generation 3.31.7 Multiple PTP Time Domains 3.31.8 Register Interface to 1588 Functions 3.31.9 Configuring I/O Delays 3.32 VRAP Engine 3.32.1 VRAP Request Frame Format 3.32.2 VRAP Response Frame Format 3.32.3 VRAP Header Format 3.32.4 VRAP READ Command 3.32.5 VRAP READ-MODIFY-WRITE Command 3.32.6 VRAP IDLE Command 3.32.7 VRAP PAUSE Command 3.33 Energy Efficient Ethernet 3.34 CPU Injection and Extraction 3.34.1 Frame Injection 3.34.2 Frame Extraction 3.34.3 Forwarding to CPU 3.34.4 Automatic Frame Injection (AFI) 3.35 Priority-Based Flow Control (PFC) 3.35.1 PFC Pause Frame Generation 3.35.2 PFC Frame Reception 3.36 Protection Switching 3.36.1 Ethernet Ring Protection Switching 3.36.2 Linear Protection Switching for E-Line Services 3.36.3 Link Aggregation 3.36.4 Port Protection Switching 3.37 Clocking and Reset 3.37.1 Pin Strapping 4 VCore-III System and CPU Interfaces 4.1 VCore-III Configurations 4.2 Clocking and Reset 4.2.1 Watchdog Timer 4.3 Shared Bus 4.3.1 VCore-III Shared Bus Arbitration 4.3.2 Chip Register Region 4.3.3 SI Flash Region 4.3.4 DDR3/DDR3L Region 4.3.5 PCIe Region 4.4 VCore-III CPU 4.4.1 Little Endian and Big Endian Support 4.4.2 Software Debug and Development 4.5 External CPU Support 4.5.1 Register Access and Multimaster Systems 4.5.2 Serial Interface in Slave Mode 4.5.3 MIIM Interface in Slave Mode 4.5.4 Access to the VCore Shared Bus 4.5.5 Mailbox and Semaphores 4.6 PCIe Endpoint Controller 4.6.1 Accessing Endpoint Registers 4.6.2 Enabling the Endpoint 4.6.3 Base Address Registers Inbound Requests 4.6.4 Outbound Interrupts 4.6.5 Outbound Access 4.6.6 Power Management 4.6.7 Device Reset Using PCIe 4.7 Frame DMA 4.7.1 DMA Control Block Structures 4.7.2 Enabling and Disabling FDMA Channels 4.7.3 Channel Counters 4.7.4 FDMA Events and Interrupts 4.7.5 FDMA Extraction 4.7.6 FDMA Injection 4.7.7 Manual Mode 4.8 VCore-III System Peripherals 4.8.1 SI Boot Controller 4.8.2 SI Master Controller 4.8.3 DDR3/DDR3L Memory Controller 4.8.4 Timers 4.8.5 UARTs 4.8.6 Two-Wire Serial Interface 4.8.7 MII Management Controller 4.8.8 GPIO Controller 4.8.9 Serial GPIO Controller 4.8.10 Fan Controller 4.8.11 Temperature Sensor 4.8.12 Memory Integrity Monitor 4.8.13 Interrupt Controller 5 Registers 6 Electrical Specifications 6.1 DC Characteristics 6.1.1 Reference Clock 6.1.2 PLL Clock Output 6.1.3 DDR3/DDR3L SDRAM Interface 6.1.4 SERDES1G 6.1.5 SERDES6G 6.1.6 GPIO, SI, JTAG, and Miscellaneous Signals 6.1.7 Thermal Diode 6.2 AC Characteristics 6.2.1 Reference Clock 6.2.2 PLL Clock Outputs 6.2.3 SERDES1G 6.2.4 SERDES6G 6.2.5 Reset Timing 6.2.6 MII Management 6.2.7 Serial Interface (SI) Boot Master Mode 6.2.8 Serial Interface (SI) Master Mode 6.2.9 Serial Interface (SI) for Slave Mode 6.2.10 DDR SDRAM Interface 6.2.11 JTAG Interface 6.2.12 Serial Inputs/Outputs 6.2.13 Recovered Clock Outputs 6.2.14 Two-Wire Serial Interface 6.2.15 IEEE 1588 Time Tick Outputs 6.3 Current and Power Consumption 6.3.1 Current Consumption 6.3.2 Power Consumption 6.3.3 Power Supply Sequencing 6.4 Operating Conditions 6.5 Stress Ratings 7 Pin Descriptions 7.1 Pin Diagram 7.2 Pins by Function 7.2.1 DDR SDRAM Interface 7.2.2 General-Purpose Inputs and Outputs 7.2.3 JTAG Interface 7.2.4 MII Management Interface 7.2.5 Miscellaneous 7.2.6 PCI Express Interface 7.2.7 Power Supplies and Ground 7.2.8 SERDES1G 7.2.9 SERDES6G 7.2.10 Serial CPU Interface 7.2.11 System Clock Interface 7.2.12 Twisted Pair Interface 7.3 234Pins by Number 7.4 Pins by Name 8 Package Information 8.1 Package Drawing 8.2 Thermal Specifications 8.3 Moisture Sensitivity 9 Design Guidelines 9.1 Power Supplies 9.2 Power Supply Decoupling 9.2.1 Reference Clock 9.2.2 Single-Ended REFCLK Input 9.3 Interfaces 9.3.1 General Recommendations 9.3.2 SerDes Interfaces (SGMII, 2.5G) 9.3.3 Serial Interface 9.3.4 PCI Express Interface 9.3.5 Two-Wire Serial Interface 9.3.6 DDR3 SDRAM Interface 9.3.7 Thermal Diode External Connection 10 Design Considerations 11 Ordering Information

Купить VSC7430XMT на РадиоЛоцман.Цены — от 100 до 443 949 ₽

Купить VSC7430XMT на РадиоЛоцман.Цены — от 100 до 443 949 ₽