Datasheet ADAU1772 (Analog Devices)

| Производитель | Analog Devices |

| Описание | 4 ADC, 2 DAC Low-Power Codec with Audio Processor |

| Страниц / Страница | 116 / 1 — Four ADC, Two DAC Low Power Codec. with Audio Processor. Data Sheet. … |

| Версия | C |

| Формат / Размер файла | PDF / 6.5 Мб |

| Язык документа | английский |

Four ADC, Two DAC Low Power Codec. with Audio Processor. Data Sheet. ADAU1772. FEATURES

Модельный ряд для этого даташита

Текстовая версия документа

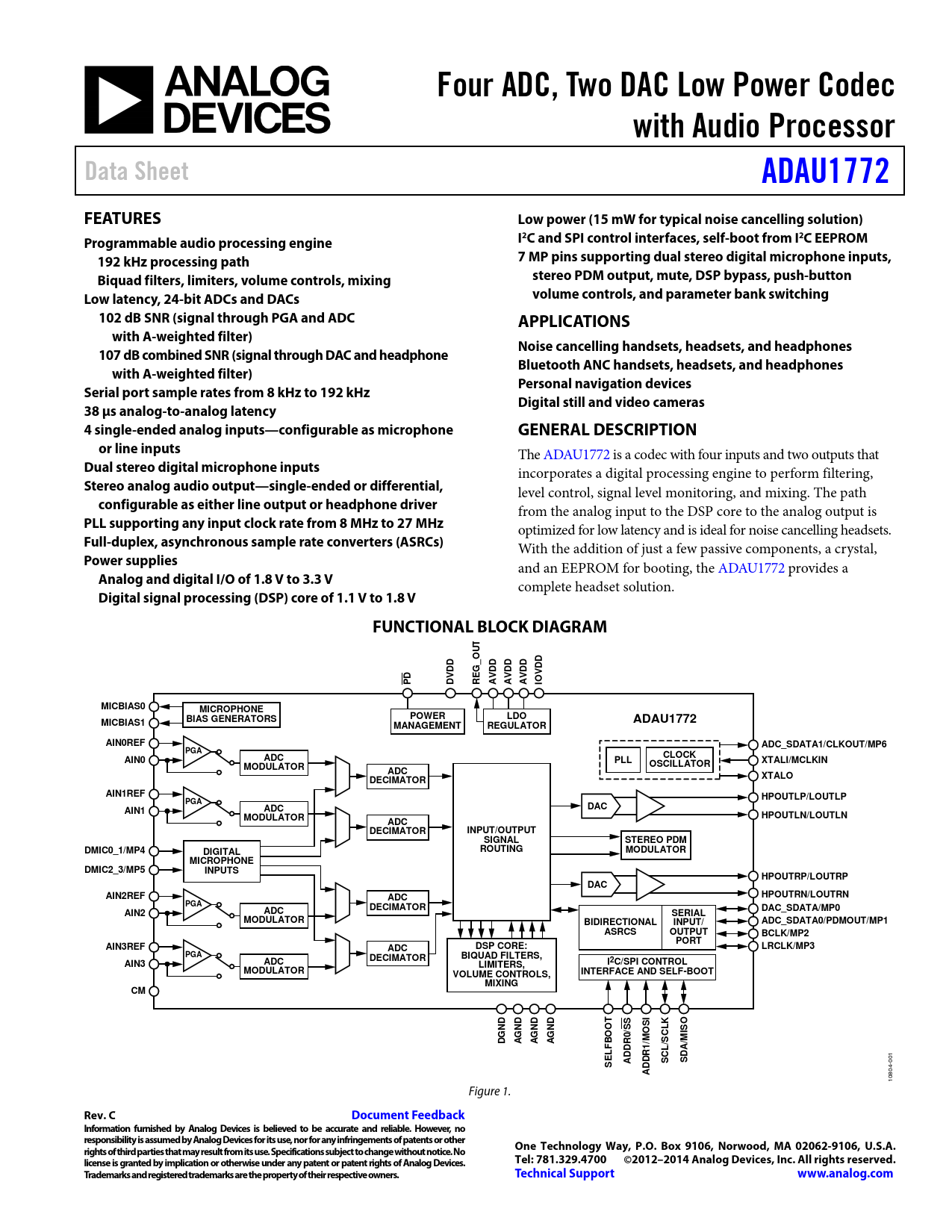

Four ADC, Two DAC Low Power Codec with Audio Processor Data Sheet ADAU1772 FEATURES Low power (15 mW for typical noise cancelling solution) Programmable audio processing engine I2C and SPI control interfaces, self-boot from I2C EEPROM 192 kHz processing path 7 MP pins supporting dual stereo digital microphone inputs, Biquad filters, limiters, volume controls, mixing stereo PDM output, mute, DSP bypass, push-button Low latency, 24-bit ADCs and DACs volume controls, and parameter bank switching 102 dB SNR (signal through PGA and ADC APPLICATIONS with A-weighted filter) Noise cancelling handsets, headsets, and headphones 107 dB combined SNR (signal through DAC and headphone Bluetooth ANC handsets, headsets, and headphones with A-weighted filter) Personal navigation devices Serial port sample rates from 8 kHz to 192 kHz Digital still and video cameras 38 μs analog-to-analog latency 4 single-ended analog inputs—configurable as microphone GENERAL DESCRIPTION or line inputs

The ADAU1772 is a codec with four inputs and two outputs that

Dual stereo digital microphone inputs

incorporates a digital processing engine to perform filtering,

Stereo analog audio output—single-ended or differential,

level control, signal level monitoring, and mixing. The path

configurable as either line output or headphone driver

from the analog input to the DSP core to the analog output is

PLL supporting any input clock rate from 8 MHz to 27 MHz

optimized for low latency and is ideal for noise cancelling headsets.

Full-duplex, asynchronous sample rate converters (ASRCs)

With the addition of just a few passive components, a crystal,

Power supplies

and an EEPROM for booting, the ADAU1772 provides a

Analog and digital I/O of 1.8 V to 3.3 V

complete headset solution.

Digital signal processing (DSP) core of 1.1 V to 1.8 V FUNCTIONAL BLOCK DIAGRAM UT _O D DD G DD DD DD D PD DV RE AV AV AV IOV MICBIAS0 MICROPHONE BIAS GENERATORS POWER LDO MICBIAS1 ADAU1772 MANAGEMENT REGULATOR AIN0REF ADC_SDATA1/CLKOUT/MP6 PGA ADC CLOCK AIN0 PLL XTALI/MCLKIN MODULATOR OSCILLATOR ADC XTALO DECIMATOR AIN1REF HPOUTLP/LOUTLP PGA ADC DAC AIN1 MODULATOR HPOUTLN/LOUTLN ADC DECIMATOR INPUT/OUTPUT SIGNAL STEREO PDM DMIC0_1/MP4 DIGITAL ROUTING MODULATOR MICROPHONE DMIC2_3/MP5 INPUTS HPOUTRP/LOUTRP DAC AIN2REF ADC HPOUTRN/LOUTRN PGA ADC DECIMATOR DAC_SDATA/MP0 AIN2 SERIAL MODULATOR BIDIRECTIONAL INPUT/ ADC_SDATA0/PDMOUT/MP1 ASRCS OUTPUT BCLK/MP2 PORT AIN3REF ADC DSP CORE: LRCLK/MP3 PGA BIQUAD FILTERS, ADC DECIMATOR AIN3 LIMITERS, I2C/SPI CONTROL MODULATOR VOLUME CONTROLS, INTERFACE AND SELF-BOOT MIXING CM S I ND ND ND ND S S LK SO OOT O C DG AG AG AG M /MI L/S A LFB E C SD S ADDR0/ S

001

ADDR1/

10804- Figure 1.

Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2012–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

Document Outline Features Applications General Description Functional Block Diagram Revision History Specifications Analog Performance Specifications Crystal Amplifier Specifications Digital Input/Output Specifications Power Supply Specifications Typical Power Consumption Digital Filters Digital Timing Specifications Digital Timing Diagrams Absolute Maximum Ratings Thermal Resistance ESD Caution Pin Configuration and Function Descriptions Typical Performance Characteristics System Block Diagrams Theory of Operation System Clocking and Power-Up Clock Initialization PLL Bypass Setup PLL Enabled Setup Control Port Access During Initialization PLL Input Clock Divider Integer Mode Fractional Mode Clock Output Power Sequencing Power-Down Considerations Signal Routing Input Signal Paths Analog Inputs Signal Polarity Input Impedance Analog Microphone Inputs Analog Line Inputs Precharging Input Capacitors Microphone Bias Digital Microphone Input Analog-to-Digital Converters ADC Full-Scale Level Digital ADC Volume Control High-Pass Filter Output Signal Paths Analog Outputs Headphone Output Headphone Output Power-Up Sequencing Ground-Centered Headphone Configuration Pop-and-Click Suppression Line Outputs Digital-to-Analog Converters DAC Full-Scale Level Digital DAC Volume Control PDM Output Asynchronous Sample Rate Converters Signal Levels Signal Processing Instructions Data Memory Parameters Control Port Burst Mode Communication I2C Port Addressing I2C Read and Write Operations SPI Port Read/Write Subaddress Data Bytes Self-Boot EEPROM Size CRC Delay Boot Time Multipurpose Pins Push-Button Volume Controls Limiter Compression Enable Parameter Bank Switching Mute DSP Bypass Mode Serial Data Input/Output Ports Tristating Unused Channels Applications Information Power Supply Bypass Capacitors Layout Grounding Exposed Pad PCB Design Register Summary Register Details Clock Control Register PLL Denominator MSB Register PLL Denominator LSB Register PLL Numerator MSB Register PLL Numerator LSB Register PLL Integer Setting Register PLL Lock Flag Register CLKOUT Setting Selection Register Regulator Control Register Core Control Register Filter Engine and Limiter Control Register DB Value Register 0 Read DB Value Register 1 Read DB Value Register 2 Read Core Channel 0/Core Channel 1 Input Select Register Core Channel 2/Core Channel 3 Input Select Register DAC Input Select Register PDM Modulator Input Select Register Serial Data Output 0/Serial Data Output 1 Input Select Register Serial Data Output 2/Serial Data Output 3 Input Select Register Serial Data Output 4/Serial Data Output 5 Input Select Register Serial Data Output 6/Serial Data Output 7 Input Select Register ADC_SDATA0/ADC_SDATA1 Channel Select Register Output ASRC0/Output ASRC1 Source Register Output ASRC2/Output ASRC3 Source Register Input ASRC Channel Select Register ADC0/ADC1 Control 0 Register ADC2/ADC3 Control 0 Register ADC0/ADC1 Control 1 Register ADC2/ADC3 Control 1 Register ADC0 Volume Control Register ADC1 Volume Control Register ADC2 Volume Control Register ADC3 Volume Control Register PGA Control 0 Register PGA Control 1 Register PGA Control 2 Register PGA Control 3 Register PGA Slew Control Register PGA 10 dB Gain Boost Register Input and Output Capacitor Charging Register DSP Bypass Path Register DSP Bypass Gain for PGA0 Register DSP Bypass Gain for PGA1 Register MIC_BIAS0_1 Control Register DAC Control Register DAC0 Volume Control Register DAC1 Volume Control Register Headphone Output Mutes Register Serial Port Control 0 Register Serial Port Control 1 Register TDM Output Channel Disable Register PDM Enable Register PDM Pattern Setting Register MP0 Function Setting Register MP1 Function Setting Register MP2 Function Setting Register MP3 Function Setting Register MP4 Function Setting Register MP5 Function Setting Register MP6 Function Setting Register Push-Button Volume Settings Register Push-Button Volume Control Assignment Register Debounce Modes Register Headphone Line Output Select Register Decimator Power Control Register ASRC Interpolator and DAC Modulator Power Control Register Analog Bias Control 0 Register Analog Bias Control 1 Register Digital Pin Pull-Up Control 0 Register Digital Pin Pull-Up Control 1 Register Digital Pin Pull-Down Control 0 Register Digital Pin Pull-Down Control 1 Register Digital Pin Drive Strength Control 0 Register Digital Pin Drive Strength Control 1 Register Outline Dimensions Ordering Guide

Купить ADAU1772BCPZ-RL на РадиоЛоцман.Цены — от 12 до 47 352 ₽

Купить ADAU1772BCPZ-RL на РадиоЛоцман.Цены — от 12 до 47 352 ₽