Datasheet 48L256 (Microchip) - 6

| Производитель | Microchip |

| Описание | 256-Kbit SPI Serial EERAM |

| Страниц / Страница | 36 / 6 — 48L256. FIGURE 1-4:. SERIAL OUTPUT TIMING. TABLE 1-3:. AC TEST … |

| Формат / Размер файла | PDF / 527 Кб |

| Язык документа | английский |

48L256. FIGURE 1-4:. SERIAL OUTPUT TIMING. TABLE 1-3:. AC TEST CONDITIONS. AC Waveform. Timing Measurement Reference Level

Модельный ряд для этого даташита

Текстовая версия документа

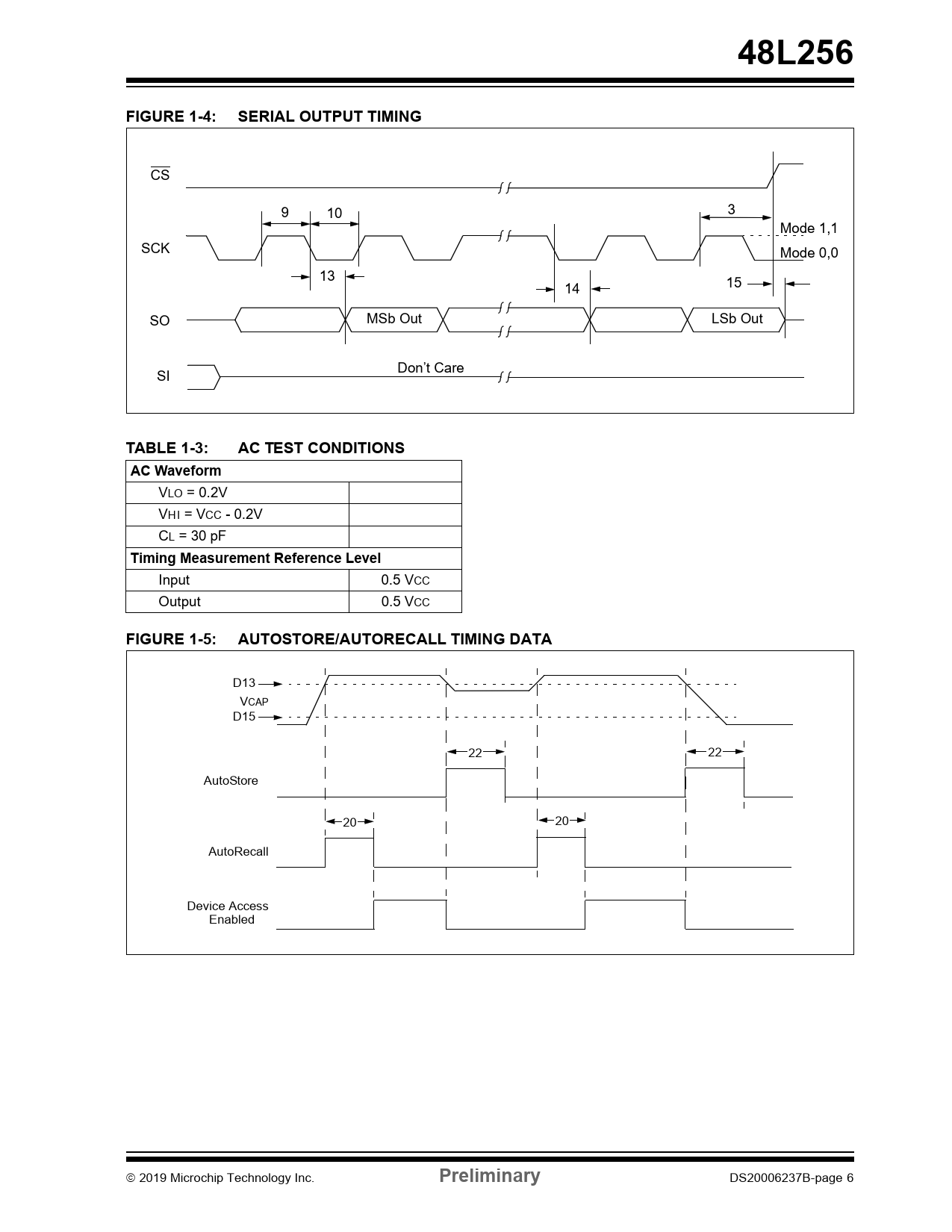

48L256 FIGURE 1-4: SERIAL OUTPUT TIMING

CS 9 10 3 Mode 1,1 SCK Mode 0,0 13 15 14 SO MSb Out LSb Out Don’t Care SI

TABLE 1-3: AC TEST CONDITIONS AC Waveform

VLO = 0.2V VHI = VCC - 0.2V CL = 30 pF

Timing Measurement Reference Level

Input 0.5 VCC Output 0.5 VCC

FIGURE 1-5: AUTOSTORE/AUTORECALL TIMING DATA

D13 VCAP D15 22 22 AutoStore 20 20 AutoRecall Device Access Enabled 2019 Microchip Technology Inc.

Preliminary

DS20006237B-page 6 Document Outline Serial SRAM Features Hidden EEPROM Backup Features Other Features of the 48L256 Packages Package Types (not to scale) Pin Function Table General Description Block Diagram Normal Device Operation Vcc Power-Off Event 1.0 Electrical Characteristics Absolute Maximum Ratings† TABLE 1-1: DC Characteristics TABLE 1-2: AC Characteristics TABLE 1-3: AC Test Conditions 2.0 Pin Descriptions TABLE 2-1: Pin Function Table 2.1 Chip Select (CS) 2.2 Serial Output (SO) 2.3 Serial Input (SI) 2.4 Serial Clock (SCK) 2.5 Hold (HOLD) 3.0 Memory Organization 3.1 Data Array Organization 3.2 16-Bit Nonvolatile User Space 3.3 Device Registers 3.3.1 STATUS Register 4.0 Functional Description FIGURE 4-1: SPI Mode 0 and Mode 3 4.1 Interfacing the 48L256 on the SPI Bus 4.1.1 Selecting the Device 4.1.2 Sending Data to the Device 4.1.3 Receiving Data from the Device 4.2 Device Opcodes 4.2.1 Serial Opcode 4.2.2 Hold Function FIGURE 4-2: Hold Mode 5.0 Write Enable and Disable 5.1 Write Enable Instruction (WREN) FIGURE 5-1: WREN Waveform 5.2 Write Disable Instruction (WRDI) FIGURE 5-2: WRDI Waveform 6.0 STATUS Register 6.1 Block Write-Protect Bits TABLE 6-2: Block Write-Protect Bits 6.2 Write Enable Latch 6.3 Ready/Busy Status Latch 6.4 Read STATUS Register (RDSR) FIGURE 6-1: RDSR Waveform 6.5 Write STATUS Register (WRSR) FIGURE 6-2: WRSR Waveform 7.0 Read Operations 7.1 Reading from the SRAM (READ) FIGURE 7-1: Read SRAM (READ) Waveform 7.2 Read Last Successfully Written Address (RDLSWA) FIGURE 7-2: Read Last Successfully Written Address Waveform 8.0 Write Commands 8.1 Write Instruction Sequences 8.1.1 SRAM Byte Write FIGURE 8-1: SRAM Byte Write Waveform 8.1.2 Continuous Write FIGURE 8-2: Continuous SRAM Write Waveform 9.0 Nonvolatile User Space Access 9.1 Write Nonvolatile User Space (WRNUR) 9.2 Read Nonvolatile User Space (RDNUR) 10.0 Secure Operations 10.1 Secure Write 10.2 Secure Read TABLE 10-1: Secure Write Bits 11.0 Store/Recall Operations 11.1 Automatic Store on Any Power Disruption 11.2 Automatic Recall to SRAM 11.3 Software Store Command FIGURE 11-1: Software Store 11.4 Software Recall Command FIGURE 11-2: Software Recall 11.5 Polling Routine FIGURE 11-3: Polling Flow 12.0 Hibernation FIGURE 12-1: Hibernate Waveform 13.0 Trip Voltage 13.1 Power Switchover 14.0 Packaging Information 14.1 Package Marking Information Appendix A: Revision History Product ID System Trademarks Worldwide Sales and Service

Купить 48L256T-I/SN на РадиоЛоцман.Цены — от 172 до 178 ₽

Купить 48L256T-I/SN на РадиоЛоцман.Цены — от 172 до 178 ₽