Datasheet VIPER26K (STMicroelectronics) - 2

| Производитель | STMicroelectronics |

| Описание | 1050 V High voltage converter |

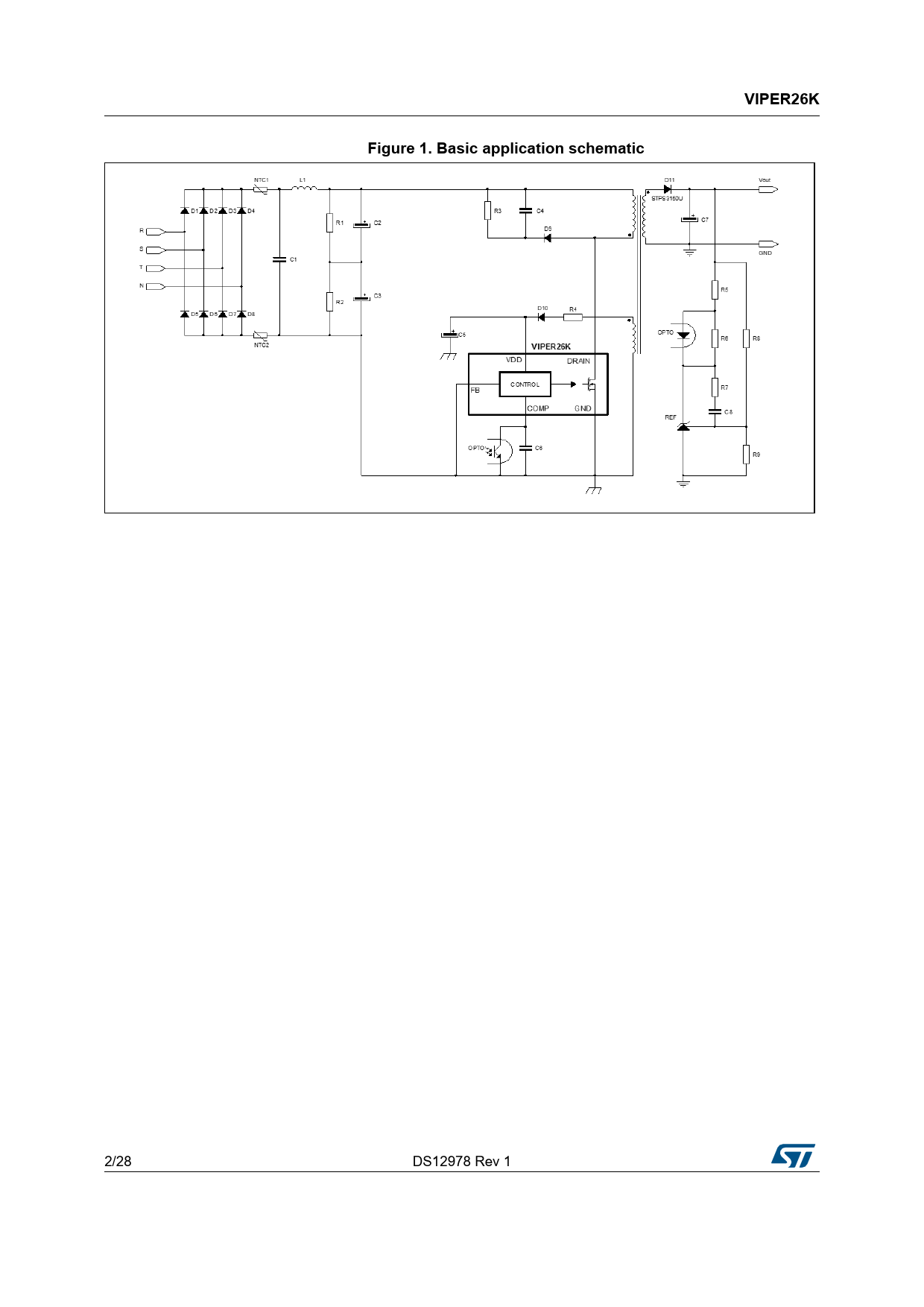

| Страниц / Страница | 28 / 2 — VIPER26K. Figure 1. Basic application schematic |

| Формат / Размер файла | PDF / 1.1 Мб |

| Язык документа | английский |

VIPER26K. Figure 1. Basic application schematic

35 предложений от 14 поставщиков AC to DC Switching Converter SMPS Controller 60kHz T/R 16-Pin SO N |

| VIPER265KDTR

STMicroelectronics | от 27 ₽ | |

| VIPER265KDTR

STMicroelectronics | 139 ₽ | |

| VIPER265KDTR

| 7 439 ₽ | |

| VIPER265KDTR

STMicroelectronics | по запросу | |

Модельный ряд для этого даташита

Текстовая версия документа

VIPER26K Figure 1. Basic application schematic

2/28 DS12978 Rev 1 Document Outline Figure 1. Basic application schematic 1 Pin setting Figure 2. Connection diagram Table 1. Pin description 2 Electrical and thermal ratings Table 2. Absolute maximum ratings Table 3. Thermal data Figure 3. RthJA Table 4. Avalanche characteristics 3 Electrical characteristics Table 5. Power section Table 6. Supply section Table 7. Controller section 3.1 Typical electrical characteristics Figure 4. IDLIM vs. Tj Figure 5. FOSC vs. Tj Figure 6. VHV_START vs. Tj Figure 7. VREF_FB vs. Tj Figure 8. IDD0 vs. Tj Figure 9. IDD1 vs. Tj Figure 10. GM vs. Tj Figure 11. HCOMP vs. Tj Figure 12. ICOMP(source/sink) vs. Tj Figure 13. ICOMP(max source) vs. Tj Figure 14. Power MOSFET capacitances variation vs. VDS @ VGS=0, f=1MHz Figure 15. VBVDSS vs. TJ .. Figure 16. RDS(on) vs. Tj Figure 17. Maximum avalanche energy vs. Tj Figure 18. SOA SSOP10 package 4 General description 4.1 Block diagram Figure 19. Block diagram 4.2 Typical power capability Table 8. Typical power 4.3 Primary MOSFET 4.4 High voltage startup Figure 20. Timing diagram: normal power-up and power-down sequences 4.5 Oscillator 4.6 Soft-start 4.7 Current limit set point 4.8 FB pin and COMP pin Figure 21. Feedback circuit Figure 22. COMP pin vs. IDLIM 4.9 Burst mode Figure 23. Load-dependent operating modes: timing diagram 4.10 Automatic auto restart after overload or short-circuit Figure 24. Timing diagram: OLP sequence 4.11 Open loop failure protection 4.12 Thermal shutdown Figure 25. Timing diagram: OLP sequence 5 Application information Figure 26. Typical isolated flyback configuration with secondary regulation Figure 27. Typical isolated flyback configuration with primary regulation Figure 28. Typical non isolated flyback configuration Figure 29. Ultra wide range Buck configuration 5.1 Layout guidelines and design recommendations Figure 30. Recommended routing for flyback converter Figure 31. Recommended routing for Buck converter 6 Package information 6.1 SO16N package information Figure 32. SO16N package outline Table 9. SO16N mechanical data 7 Order code Table 10. Order codes 8 Revision history Table 11. Document history

Купить VIPER265KDTR на РадиоЛоцман.Цены — от 27 до 7 439 ₽

Купить VIPER265KDTR на РадиоЛоцман.Цены — от 27 до 7 439 ₽