Datasheet ADRF6518 (Analog Devices)

| Производитель | Analog Devices |

| Описание | 1.1 GHz Variable Gain Amplifiers and Baseband Programmable Filters |

| Страниц / Страница | 39 / 1 — 1.1 GHz Variable Gain Amplifiers and. Baseband Programmable Filters. Data … |

| Версия | A |

| Формат / Размер файла | PDF / 1.6 Мб |

| Язык документа | английский |

1.1 GHz Variable Gain Amplifiers and. Baseband Programmable Filters. Data Sheet. ADRF6518. FEATURES. FUNCTIONAL BLOCK DIAGRAM

Модельный ряд для этого даташита

Текстовая версия документа

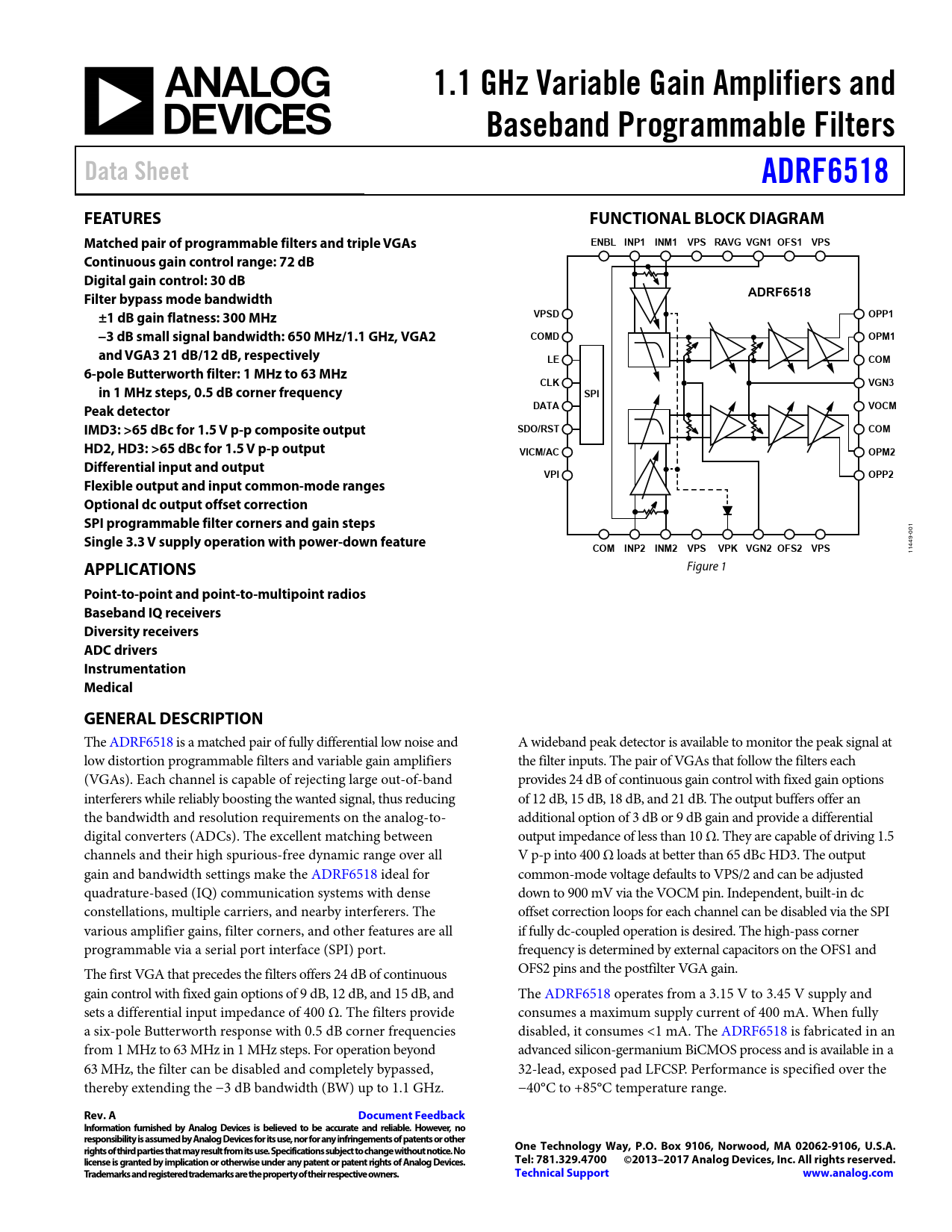

1.1 GHz Variable Gain Amplifiers and Baseband Programmable Filters Data Sheet ADRF6518 FEATURES FUNCTIONAL BLOCK DIAGRAM Matched pair of programmable filters and triple VGAs ENBL INP1 INM1 VPS RAVG VGN1 OFS1 VPS Continuous gain control range: 72 dB Digital gain control: 30 dB ADRF6518 Filter bypass mode bandwidth ±1 dB gain flatness: 300 MHz VPSD OPP1 −3 dB small signal bandwidth: 650 MHz/1.1 GHz, VGA2 COMD OPM1 and VGA3 21 dB/12 dB, respectively LE COM 6-pole Butterworth filter: 1 MHz to 63 MHz CLK VGN3 in 1 MHz steps, 0.5 dB corner frequency SPI DATA VOCM Peak detector IMD3: >65 dBc for 1.5 V p-p composite output SDO/RST COM HD2, HD3: >65 dBc for 1.5 V p-p output VICM/AC OPM2 Differential input and output VPI OPP2 Flexible output and input common-mode ranges Optional dc output offset correction SPI programmable filter corners and gain steps

1 00

Single 3.3 V supply operation with power-down feature COM INP2 INM2 VPS VPK VGN2 OFS2 VPS

11449-

APPLICATIONS

Figure 1

Point-to-point and point-to-multipoint radios Baseband IQ receivers Diversity receivers ADC drivers Instrumentation Medical GENERAL DESCRIPTION

The ADRF6518 is a matched pair of fully differential low noise and A wideband peak detector is available to monitor the peak signal at low distortion programmable filters and variable gain amplifiers the filter inputs. The pair of VGAs that follow the filters each (VGAs). Each channel is capable of rejecting large out-of-band provides 24 dB of continuous gain control with fixed gain options interferers while reliably boosting the wanted signal, thus reducing of 12 dB, 15 dB, 18 dB, and 21 dB. The output buffers offer an the bandwidth and resolution requirements on the analog-to- additional option of 3 dB or 9 dB gain and provide a differential digital converters (ADCs). The excellent matching between output impedance of less than 10 Ω. They are capable of driving 1.5 channels and their high spurious-free dynamic range over all V p-p into 400 Ω loads at better than 65 dBc HD3. The output gain and bandwidth settings make the ADRF6518 ideal for common-mode voltage defaults to VPS/2 and can be adjusted quadrature-based (IQ) communication systems with dense down to 900 mV via the VOCM pin. Independent, built-in dc constellations, multiple carriers, and nearby interferers. The offset correction loops for each channel can be disabled via the SPI various amplifier gains, filter corners, and other features are all if fully dc-coupled operation is desired. The high-pass corner programmable via a serial port interface (SPI) port. frequency is determined by external capacitors on the OFS1 and The first VGA that precedes the filters offers 24 dB of continuous OFS2 pins and the postfilter VGA gain. gain control with fixed gain options of 9 dB, 12 dB, and 15 dB, and The ADRF6518 operates from a 3.15 V to 3.45 V supply and sets a differential input impedance of 400 Ω. The filters provide consumes a maximum supply current of 400 mA. When fully a six-pole Butterworth response with 0.5 dB corner frequencies disabled, it consumes <1 mA. The ADRF6518 is fabricated in an from 1 MHz to 63 MHz in 1 MHz steps. For operation beyond advanced silicon-germanium BiCMOS process and is available in a 63 MHz, the filter can be disabled and completely bypassed, 32-lead, exposed pad LFCSP. Performance is specified over the thereby extending the −3 dB bandwidth (BW) up to 1.1 GHz. −40°C to +85°C temperature range.

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2013–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

Document Outline FEATURES APPLICATIONS FUNCTIONAL BLOCK DIAGRAM GENERAL DESCRIPTION REVISION HISTORY SPECIFICATIONS TIMING DIAGRAMS ABSOLUTE MAXIMUM RATINGS ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS FILTER MODE BYPASS MODE MIXED POWER AND FILTER MODES CHARACTERIZATION NOISE FIGURE CALCULATION REGISTER MAP AND CODES THEORY OF OPERATION INPUT VGAs Driving ADRF6518 Single-Ended PEAK DETECTOR PROGRAMMABLE FILTERS Bypassing the Filters VARIABLE GAIN AMPLIFIERS (VGAs) OUTPUT BUFFERS/ADC DRIVERS DC OFFSET COMPENSATION LOOP PROGRAMMING THE ADRF6518 NOISE CHARACTERISTICS DISTORTION CHARACTERISTICS MAXIMIZING THE DYNAMIC RANGE KEY PARAMETERS FOR QUADRATURE-BASED RECEIVERS APPLICATIONS INFORMATION BASIC CONNECTIONS SUPPLY DECOUPLING INPUT SIGNAL PATH OUTPUT SIGNAL PATH DC OFFSET COMPENSATION LOOP ENABLED COMMON-MODE BYPASSING SERIAL PORT CONNECTIONS ENABLE/DISABLE FUNCTION GAIN PIN DECOUPLING PEAK DETECTOR CONNECTIONS ERROR VECTOR MAGNITUDE (EVM) PERFORMANCE EVM TEST SETUP EVM MEASUREMENT EVM SYSTEM MEASUREMENT EFFECT OF FILTER BW ON EVM PULL-DOWN RESISTORS FOR DISABLE FUNCTION INSTABILITY AT HIGH GAIN IN FILTER BYPASS MODE INSTABILITY AT LOW FILTER CORNERS AND LOW POWER MODE PEAK DETECTOR BANDWIDTH AND SLEW RATE LINEAR OPERATION OF THE ADRF6518 EVALUATION BOARD EVALUATION BOARD CONTROL SOFTWARE SCHEMATICS AND ARTWORK OUTLINE DIMENSIONS ORDERING GUIDE

Купить ADRF6518ACPZ-WP на РадиоЛоцман.Цены — от 1 913 до 104 986 ₽

Купить ADRF6518ACPZ-WP на РадиоЛоцман.Цены — от 1 913 до 104 986 ₽