Datasheet AD9271 (Analog Devices)

| Производитель | Analog Devices |

| Описание | Octal LNA/VGA/AAF/ADC and Crosspoint Switch |

| Страниц / Страница | 60 / 1 — Octal LNA/VGA/AAF/ADC. and Crosspoint Switch. AD9271. FEATURES. … |

| Версия | B |

| Формат / Размер файла | PDF / 2.1 Мб |

| Язык документа | английский |

Octal LNA/VGA/AAF/ADC. and Crosspoint Switch. AD9271. FEATURES. FUNCTIONAL BLOCK DIAGRAM. 8 channels of LNA, VGA, AAF, and ADC

18 предложений от 14 поставщиков Микросхема Преобразователь AD, AFE General Purpose 8ADC 12Bit 1.8V/3.3V Automotive 100Pin TQFP EP Tray |

| AD9271BSVZ-50

Analog Devices | 5 025 ₽ | |

| AD9271BSVZ-50

Analog Devices | 12 087 ₽ | |

| AD9271BSVZ-50

Analog Devices | 12 718 ₽ | |

| AD9271BSVZ-50

Analog Devices | по запросу | |

Модельный ряд для этого даташита

Текстовая версия документа

Octal LNA/VGA/AAF/ADC and Crosspoint Switch AD9271 FEATURES FUNCTIONAL BLOCK DIAGRAM 8 channels of LNA, VGA, AAF, and ADC D N DD D BY V Low noise preamplifier (LNA) AV PDW ST DR Input-referred noise = 1.1 nV/√Hz @ 5 MHz typical, LOSW-A gain = 18 dB AD9271 LO-A SPI-programmable gain = 14 dB/15.6 dB/18 dB LI-A 12-BIT SERIAL DOUTA+ Single-ended input; V LNA VGA IN maximum = 400 mV p-p/ LG-A ADC LVDS DOUTA– AAF 333 mV p-p/250 mV p-p LOSW-B Dual-mode active input impedance matching LO-B LI-B DOUTB+ Bandwidth (BW) > 70 MHz 12-BIT LNA SERIAL VGA LG-B ADC LVDS DOUTB– Full-scale (FS) output = 2 V p-p differential AAF LOSW-C Variable gain amplifier (VGA) LO-C Gain range = −6 dB to +24 dB LI-C 12-BIT DOUTC+ LNA SERIAL VGA LG-C ADC LVDS DOUTC– Linear-in-dB gain control AAF LOSW-D Antialiasing filter (AAF) LO-D 3rd-order Butterworth cutoff LI-D 12-BIT DOUTD+ LNA SERIAL VGA Programmable from 8 MHz to 18 MHz LG-D ADC LVDS DOUTD– AAF Analog-to-digital converter (ADC) LOSW-E LO-E 12 bits at 10 MSPS to 50 MSPS LI-E 12-BIT SERIAL DOUTE+ SNR = 70 dB LNA VGA LG-E ADC LVDS DOUTE– AAF SFDR = 80 dB LOSW-F Serial LVDS (ANSI-644, IEEE 1596.3 reduced range link) LO-F LI-F DOUTF+ Data and frame clock outputs 12-BIT LNA SERIAL VGA LG-F ADC LVDS DOUTF– Includes crosspoint switch to support AAF LOSW-G continuous wave (CW) Doppler LO-G Low power, 150 mW per channel at 12 bits/40 MSPS (TGC) LI-G 12-BIT DOUTG+ LNA SERIAL VGA LG-G ADC LVDS DOUTG– 90 mW per channel in CW Doppler AAF LOSW-H Single 1.8 V supply (3.3 V supply for CW Doppler output bias) LO-H Flexible power-down modes LI-H 12-BIT DOUTH+ LNA SERIAL VGA Overload recovery in <10 ns LG-H ADC LVDS DOUTH– AAF Fast recovery from low power standby mode, <2 μs E R C E 100-lead TQFP L A E LI FCO+ IA A RT F T IP R FCO– PO DA RAT LT APPLICATIONS SER REFERENCE TE U DCO+ IN SWITCH M DCO– ARRAY Medical imaging/ultrasound Automotive radar D + – /– B T K + – D SE EF F F IO GENERAL DESCRIPTION K K IN IN IAS V N CSB 0]+ VR RE RE SD SCL CL CL GA GA RB SE

01

CW

0 The AD9271 is designed for low cost, low power, small size,

D[5: W

304-

C

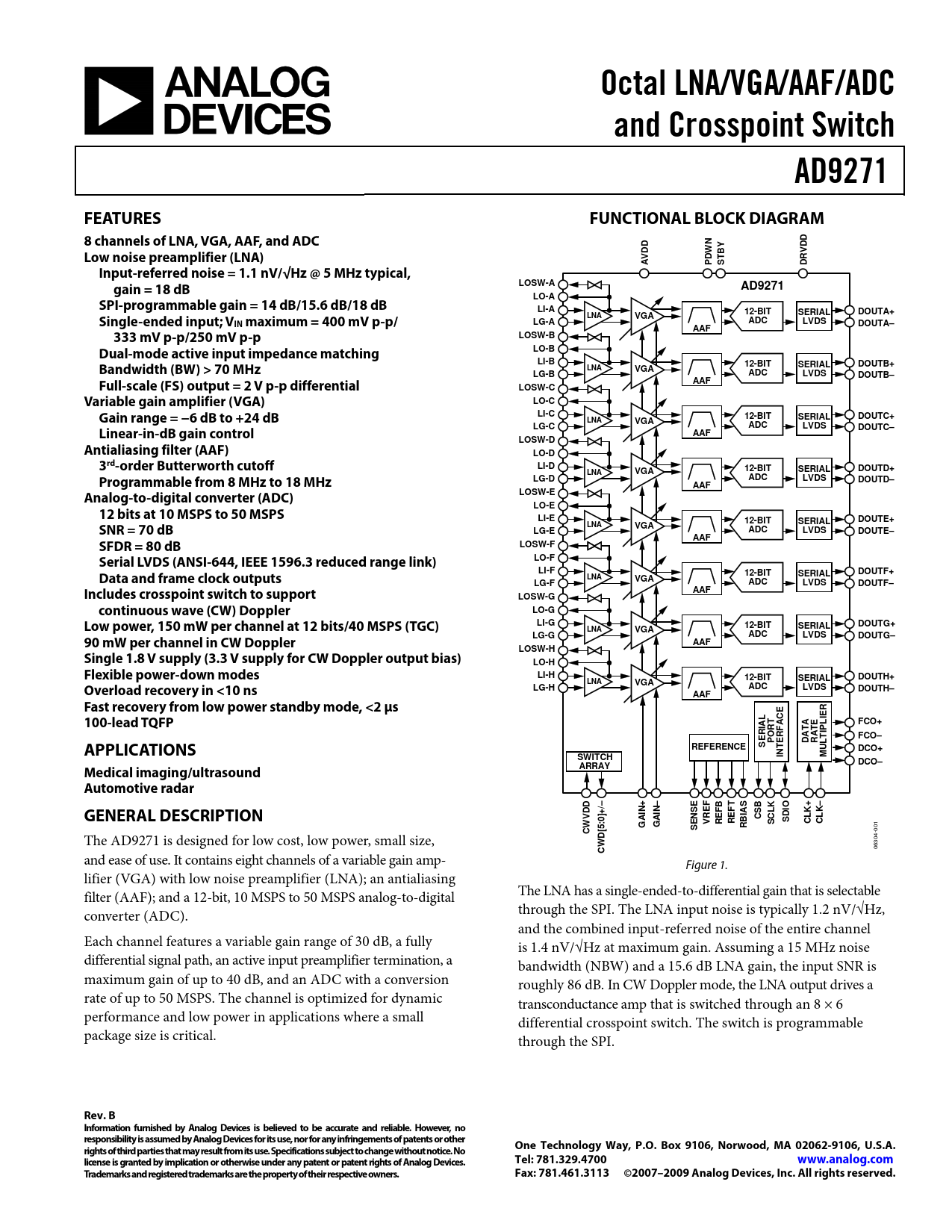

06 and ease of use. It contains eight channels of a variable gain amp- Figure 1. lifier (VGA) with low noise preamplifier (LNA); an antialiasing filter (AAF); and a 12-bit, 10 MSPS to 50 MSPS analog-to-digital The LNA has a single-ended-to-differential gain that is selectable converter (ADC). through the SPI. The LNA input noise is typically 1.2 nV/√Hz, and the combined input-referred noise of the entire channel Each channel features a variable gain range of 30 dB, a fully is 1.4 nV/√Hz at maximum gain. Assuming a 15 MHz noise differential signal path, an active input preamplifier termination, a bandwidth (NBW) and a 15.6 dB LNA gain, the input SNR is maximum gain of up to 40 dB, and an ADC with a conversion roughly 86 dB. In CW Doppler mode, the LNA output drives a rate of up to 50 MSPS. The channel is optimized for dynamic transconductance amp that is switched through an 8 × 6 performance and low power in applications where a small differential crosspoint switch. The switch is programmable package size is critical. through the SPI.

Rev. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 www.analog.com Trademarks and registered trademarks are the property of their respective owners. Fax: 781.461.3113 ©2007–2009 Analog Devices, Inc. All rights reserved.

Document Outline FEATURES APPLICATIONS GENERAL DESCRIPTION FUNCTIONAL BLOCK DIAGRAM TABLE OF CONTENTS REVISION HISTORY PRODUCT HIGHLIGHTS SPECIFICATIONS AC SPECIFICATIONS DIGITAL SPECIFICATIONS SWITCHING SPECIFICATIONS ADC TIMING DIAGRAMS ABSOLUTE MAXIMUM RATINGS THERMAL IMPEDANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS EQUIVALENT CIRCUITS TYPICAL PERFORMANCE CHARACTERISTICS THEORY OF OPERATION ULTRASOUND CHANNEL OVERVIEW Low Noise Amplifier (LNA) Active Impedance Matching LNA Noise INPUT OVERDRIVE Input Overload Protection CW DOPPLER OPERATION Crosspoint Switch TGC OPERATION Variable Gain Amplifier Gain Control VGA Noise Antialiasing Filter ADC CLOCK INPUT CONSIDERATIONS Clock Duty Cycle Considerations Clock Jitter Considerations Power Dissipation and Power-Down Mode Digital Outputs and Timing SDIO Pin SCLK Pin CSB Pin RBIAS Pin Voltage Reference Internal Reference Operation External Reference Operation SERIAL PORT INTERFACE (SPI) HARDWARE INTERFACE MEMORY MAP READING THE MEMORY MAP TABLE RESERVED LOCATIONS DEFAULT VALUES LOGIC LEVELS APPLICATIONS INFORMATION DESIGN GUIDELINES Power and Ground Recommendations Exposed Paddle Thermal Heat Slug Recommendations EVALUATION BOARD POWER SUPPLIES INPUT SIGNALS OUTPUT SIGNALS DEFAULT OPERATION AND JUMPER SELECTION SETTINGS QUICK START PROCEDURE SCHEMATICS AND ARTWORK OUTLINE DIMENSIONS ORDERING GUIDE

Купить AD9271BSVZ-50 на РадиоЛоцман.Цены — от 895 до 17 950 ₽

Купить AD9271BSVZ-50 на РадиоЛоцман.Цены — от 895 до 17 950 ₽