Datasheet AD9284 (Analog Devices)

| Производитель | Analog Devices |

| Описание | 8-Bit, 250 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| Страниц / Страница | 24 / 1 — 8-Bit, 250 MSPS, 1.8 V Dual. Analog-to-Digital Converter (ADC). Data … |

| Версия | A |

| Формат / Размер файла | PDF / 1.4 Мб |

| Язык документа | английский |

8-Bit, 250 MSPS, 1.8 V Dual. Analog-to-Digital Converter (ADC). Data Sheet. AD9284. FEATURES. GENERAL DESCRIPTION

Модельный ряд для этого даташита

Текстовая версия документа

8-Bit, 250 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) Data Sheet AD9284 FEATURES GENERAL DESCRIPTION Single 1.8 V supply operation

The AD9284 is a dual 8-bit, monolithic sampling, analog-to-digital

SNR: 49.3 dBFS at 200 MHz input at 250 MSPS

converter (ADC) that supports simultaneous operation and is

SFDR: 65 dBc at 200 MHz input at 250 MSPS

optimized for low cost, low power, and ease of use. Each ADC

Low power: 314 mW at 250 MSPS

operates at up to a 250 MSPS conversion rate with outstanding

On-chip reference and track-and-hold

dynamic performance.

1.2 V p-p analog input range for each channel

The ADC requires a single 1.8 V supply and an encode clock for

Differential input with 500 MHz bandwidth

full performance operation. No external reference components

LVDS-compliant digital output

are required for many applications. The digital outputs are LVDS

DNL: ±0.2 LSB

compatible.

Serial port control options Offset binary, Gray code, or twos complement data format

The AD9284 is available in a Pb-free, 48-lead LFCSP that is

Optional clock duty cycle stabilizer

specified over the industrial temperature range of −40°C to +85°C.

Built-in selectable digital test pattern generation PRODUCT HIGHLIGHTS Pin-programmable power-down function Available in 48-lead LFCSP

1. Integrated Dual 8-Bit, 250 MSPS ADC. 2. Single 1.8 V Supply Operation with LVDS Outputs.

APPLICATIONS

3. Power-Down Option Control ed via a Pin-Programmable

Communications

Setting.

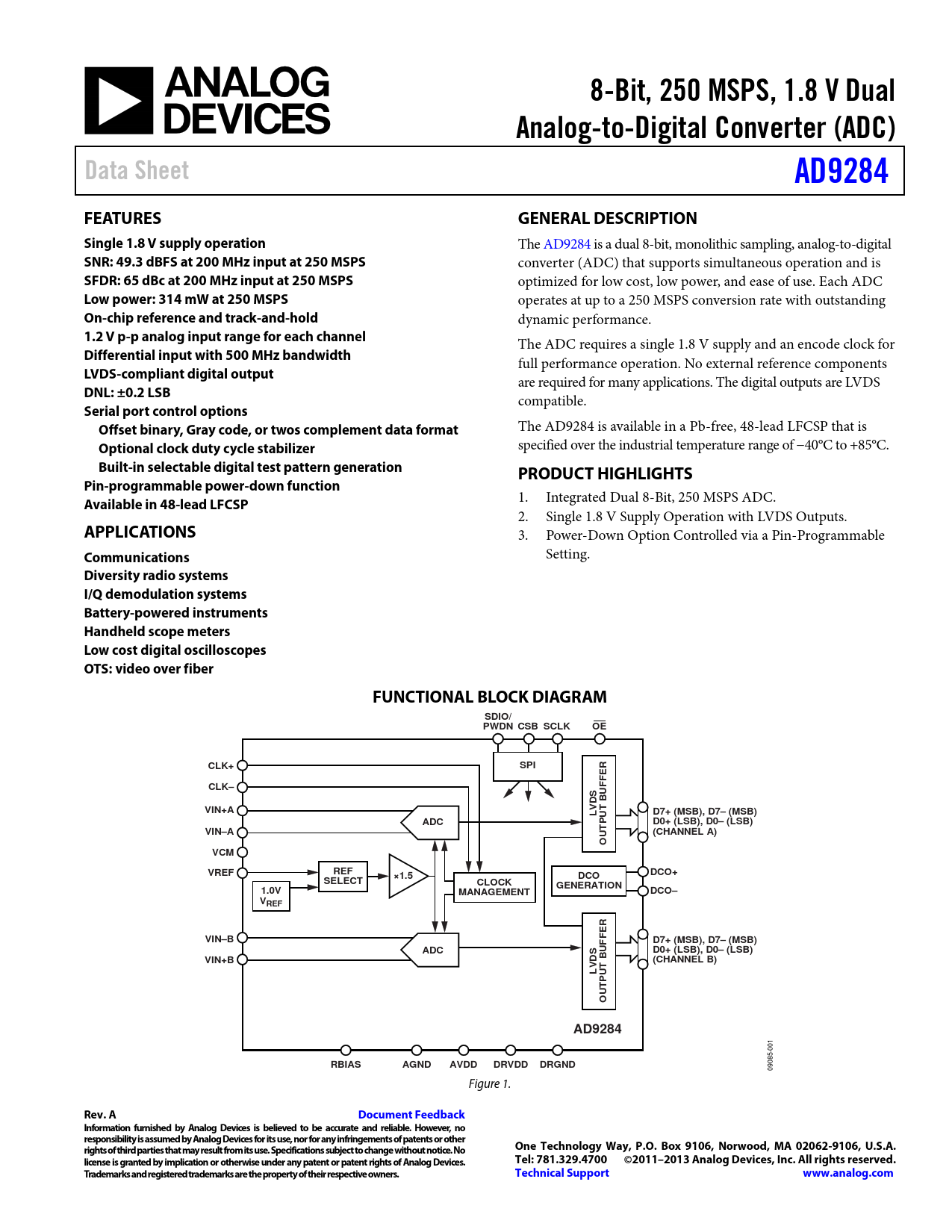

Diversity radio systems I/Q demodulation systems Battery-powered instruments Handheld scope meters Low cost digital oscilloscopes OTS: video over fiber FUNCTIONAL BLOCK DIAGRAM SDIO/ PWDN CSB SCLK OE CLK+ SPI R CLK– FFE U DS VIN+A V T B L U D7+ (MSB), D7– (MSB) ADC D0+ (LSB), D0– (LSB) TP VIN–A (CHANNEL A) OU VCM VREF REF ×1.5 DCO DCO+ SELECT CLOCK GENERATION 1.0V MANAGEMENT DCO– VREF R VIN–B FFE D7+ (MSB), D7– (MSB) ADC U D0+ (LSB), D0– (LSB) VIN+B DS (CHANNEL B) V T B L U TP OU AD9284

001

RBIAS AGND AVDD DRVDD DRGND

09085- Figure 1.

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2011–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

Document Outline Features Applications General Description Product Highlights Functional Block Diagram Revision History Specifications DC Specifications AC Specifications Digital Specifications Switching Specifications SPI Timing Specifications Timing Diagram Absolute Maximum Ratings Thermal Resistance ESD Caution Pin Configuration and Function Descriptions Typical Performance Characteristics Equivalent Circuits Theory of Operation ADC Architecture Analog Input Considerations Differential Input Configurations Voltage Reference RBIAS Clock Input Considerations Clock Input Options Digital Outputs Digital Output Enable Function () Built-In Self-Test (BIST) and Output Test Built-In Self-Test (BIST) Output Test Modes Serial Port Interface (SPI) Configuration Using the SPI Hardware Interface Configuration Without the SPI SPI Accessible Features Memory Map Reading the Memory Map Register Table Open Locations Default Values Logic Levels Transfer Register Map Channel-Specific Registers Memory Map Register Table Memory Map Register Descriptions Voltage Reference (Register 0x18) Bits[7:5]—Reserved Bits[4:0]—Voltage Reference Applications Information Design Guidelines Power and Ground Recommendations Exposed Paddle Thermal Heat Sink Recommendations VCM RBIAS Reference Decoupling SPI Port Outline Dimensions Ordering Guide

Купить AD9284BCPZRL7-250 на РадиоЛоцман.Цены — от 317 до 247 864 ₽

Купить AD9284BCPZRL7-250 на РадиоЛоцман.Цены — от 317 до 247 864 ₽