DatasheetsDatasheet ADSP-21371, ADSP-21375 (Analog …

Datasheet ADSP-21371, ADSP-21375 (Analog Devices)

| Производитель | Analog Devices |

| Описание | SHARC Processor |

| Страниц / Страница | 56 / 1 — SHARC Processor. ADSP-21371. /ADSP-21375. SUMMARY. DEDICATED AUDIO … |

| Версия | D |

| Формат / Размер файла | PDF / 1.3 Мб |

| Язык документа | английский |

SHARC Processor. ADSP-21371. /ADSP-21375. SUMMARY. DEDICATED AUDIO COMPONENTS

Модельный ряд для этого даташита

Текстовая версия документа

link to page 56 link to page 56

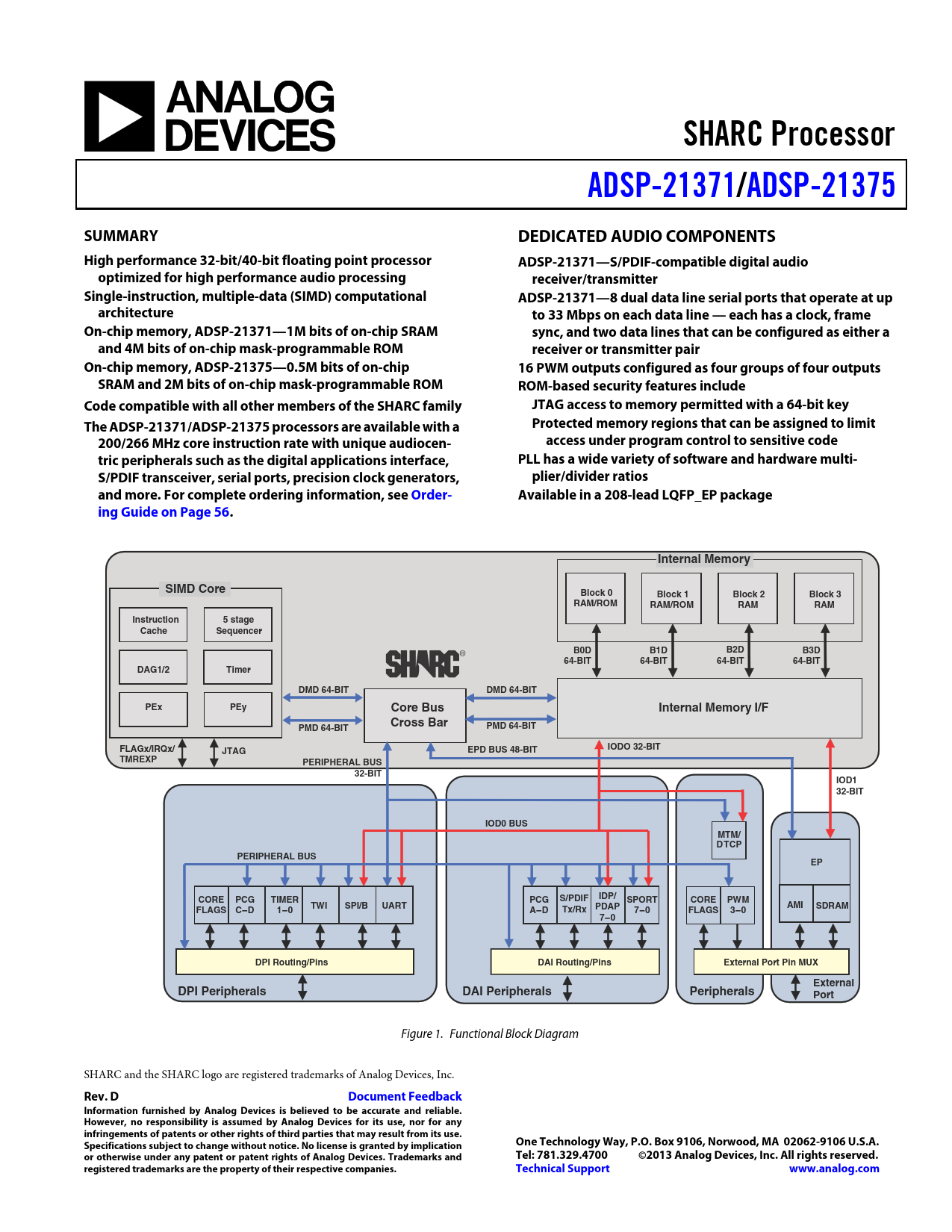

SHARC Processor ADSP-21371 /ADSP-21375 SUMMARY DEDICATED AUDIO COMPONENTS High performance 32-bit/40-bit floating point processor ADSP-21371—S/PDIF-compatible digital audio optimized for high performance audio processing receiver/transmitter Single-instruction, multiple-data (SIMD) computational ADSP-21371—8 dual data line serial ports that operate at up architecture to 33 Mbps on each data line — each has a clock, frame On-chip memory, ADSP-21371—1M bits of on-chip SRAM sync, and two data lines that can be configured as either a and 4M bits of on-chip mask-programmable ROM receiver or transmitter pair On-chip memory, ADSP-21375—0.5M bits of on-chip 16 PWM outputs configured as four groups of four outputs SRAM and 2M bits of on-chip mask-programmable ROM ROM-based security features include Code compatible with all other members of the SHARC family JTAG access to memory permitted with a 64-bit key The ADSP-21371/ADSP-21375 processors are available with a Protected memory regions that can be assigned to limit 200/266 MHz core instruction rate with unique audiocen- access under program control to sensitive code tric peripherals such as the digital applications interface, PLL has a wide variety of software and hardware multi- S/PDIF transceiver, serial ports, precision clock generators, plier/divider ratios and more. For complete ordering information, see Order- Available in a 208-lead LQFP_EP package ing Guide on Page 56 . Internal Memory SIMD Core Block 0 Block 1 Block 2 Block 3 RAM/ROM RAM/ROM RAM RAM Instruction 5 stage Cache Sequencer B0D B1D B2D B3D 64-BIT 64-BIT 64-BIT 64-BIT

S

DAG1/2 Timer DMD 64-BIT DMD 64-BIT PEx PEy Core Bus Internal Memory I/F Cross Bar PMD 64-BIT PMD 64-BIT IODO 32-BIT FLAGx/IRQx/ EPD BUS 48-BIT JTAG TMREXP PERIPHERAL BUS 32-BIT IOD1 32-BIT IOD0 BUS MTM/ D TCP PERIPHERAL BUS EP CORE PCG TIMER PCG IDP/ S/PDIF SPORT CORE PWM TWI SPI/B UART PDAP AMI SDRAM FLAGS C-D 1-0 A-D Tx/Rx 7-0 FLAGS 3-0 7-0 DPI Routing/Pins DAI Routing/Pins External Port Pin MUX External DPI Peripherals DAI Peripherals Peripherals Port

Figure 1. Functional Block Diagram SHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.

Rev. D Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. or otherwise under any patent or patent rights of Analog Devices. Trademarks and Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. registered trademarks are the property of their respective companies. Technical Support www.analog.com

Document Outline Summary Dedicated Audio Components Table Of Contents Revision History General Description SHARC Family Core Architecture SIMD Computational Engine Independent, Parallel Computation Units Data Register File Context Switch Universal Registers Timer Single-Cycle Fetch of an Instruction and Four Operands Instruction Cache Data Address Generators with Zero-Overhead Hardware Circular Buffer Support Flexible Instruction Set On-Chip Memory On-Chip Memory Bandwidth ROM-Based Security Family Peripheral Architecture External Port SDRAM Controller External Memory Code Execution External Port Throughput Asynchronous Memory Controller Pulse-Width Modulation Digital Applications Interface (DAI) Serial Ports S/PDIF-Compatible Digital Audio Receiver/Transmitter Input Data Port (IDP) Precision Clock Generator (PCG) Digital Peripheral Interface (DPI) Serial Peripheral (Compatible) Interface UART Port Peripheral Timers 2-Wire Interface Port (TWI) I/O Processor Features DMA Controller Delay Line DMA Scatter/Gather DMA System Design Program Booting Power Supplies Target Board JTAG Emulator Connector Development Tools Integrated Development Environments (IDEs) EZ-KIT Lite Evaluation Board EZ-KIT Lite Evaluation Kits Software Add-Ins for CrossCore Embedded Studio Board Support Packages for Evaluation Hardware Middleware Packages Algorithmic Modules Designing an Emulator-Compatible DSP Board (Target) Additional Information Related Signal Chains Pin Function Descriptions ADSP-21371/ADSP-21375 Specifications Operating Conditions Electrical Characteristics Package Information Maximum Power Dissipation Absolute Maximum Ratings ESD Sensitivity Timing Specifications Core Clock Requirements Voltage Controlled Oscillator Power-Up Sequencing Clock Input Clock Signals Reset Running Reset Core Timer Interrupts Timer PWM_OUT Cycle Timing Timer WDTH_CAP Timing Pin to Pin Direct Routing (DAI and DPI) Precision Clock Generator (Direct Pin Routing) Flags SDRAM Interface Timing Memory Read—Bus Master Memory Write—Bus Master Serial Ports Input Data Port (IDP) Parallel Data Acquisition Port (PDAP) Pulse-Width Modulation Generators (PWM) S/PDIF Transmitter S/PDIF Transmitter-Serial Input Waveforms S/PDIF Transmitter Input Data Timing Oversampling Clock (HFCLK) Switching Characteristics S/PDIF Receiver Internal Digital PLL Mode SPI Interface—Master SPI Interface—Slave Universal Asynchronous Receiver-Transmitter (UART) Port—Receive and Transmit Timing TWI Controller Timing JTAG Test Access Port and Emulation Output Drive Currents Test Conditions Capacitive Loading Thermal Characteristics 208-Lead LQFP_EP Pinout Package Dimensions Automotive Products Ordering Guide

Купить ADSP-21375BSWZ-2B на РадиоЛоцман.Цены — от 11 до 117 737 ₽

Купить ADSP-21375BSWZ-2B на РадиоЛоцман.Цены — от 11 до 117 737 ₽