Datasheet ADAU1702 (Analog Devices) - 8

| Производитель | Analog Devices |

| Описание | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| Страниц / Страница | 52 / 8 — ADAU1702. Data Sheet. Digital Timing Diagrams. tBIH. tLIH. INPUT_BCLK. … |

| Версия | D |

| Формат / Размер файла | PDF / 1.2 Мб |

| Язык документа | английский |

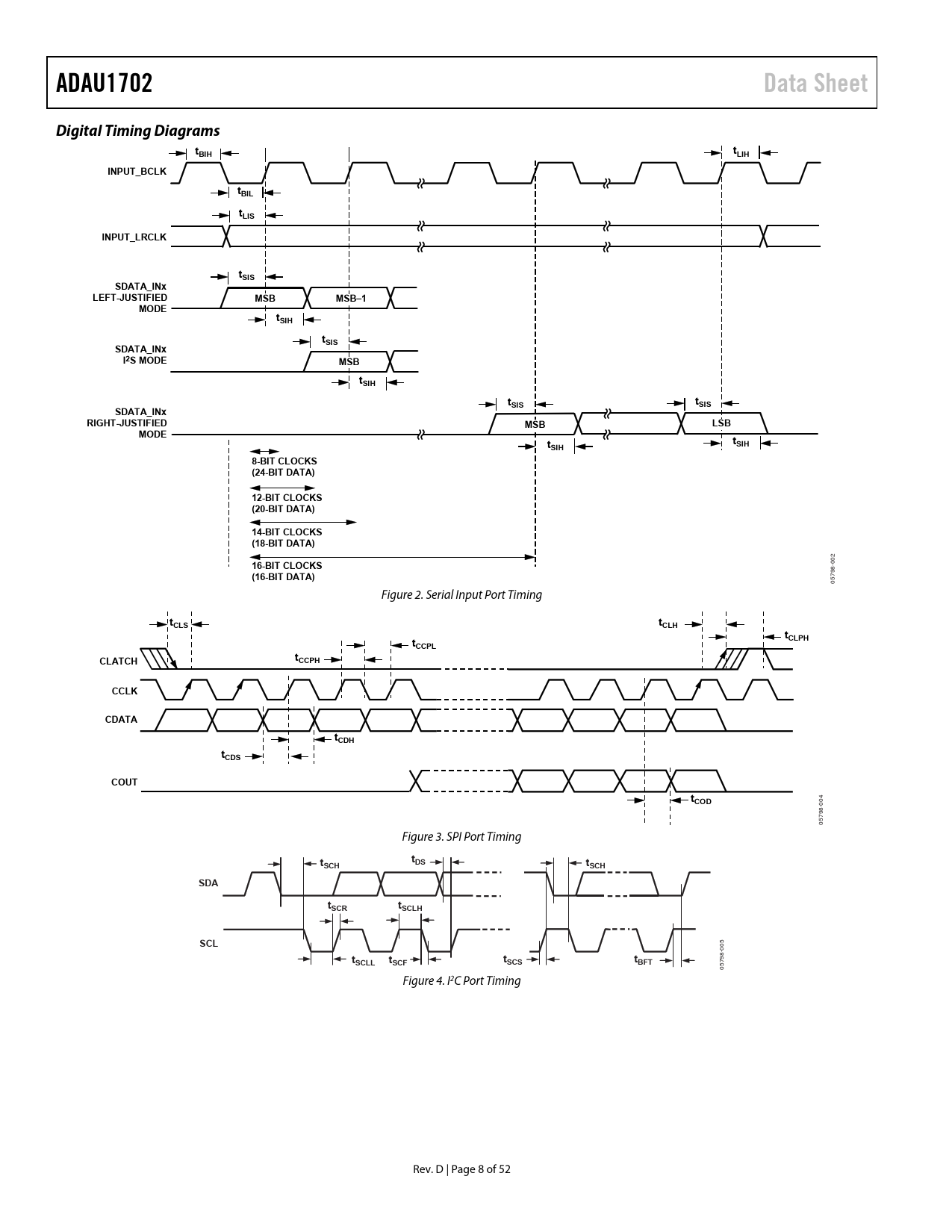

ADAU1702. Data Sheet. Digital Timing Diagrams. tBIH. tLIH. INPUT_BCLK. tBIL. tLIS. INPUT_LRCLK. tSIS. SDATA_INx. LEFT-JUSTIFIED. MSB. MSB–1. MODE

35 предложений от 19 поставщиков Интегральные микросхемы Встроенные микросхемы - Цифровые сигнальные процессоры (ЦСП) |

| ADAU1702JSTZ

Analog Devices | от 14 ₽ | |

| ADAU1702JSTZ

Analog Devices | 345 ₽ | |

| ADAU1702JSTZ

Analog Devices | от 536 ₽ | |

| ADAU1702JSTZ-RL

Analog Devices | по запросу | |

Модельный ряд для этого даташита

Текстовая версия документа

ADAU1702 Data Sheet Digital Timing Diagrams tBIH tLIH INPUT_BCLK tBIL tLIS INPUT_LRCLK tSIS SDATA_INx LEFT-JUSTIFIED MSB MSB–1 MODE tSIH tSIS SDATA_INx I2S MODE MSB tSIH t t SIS SIS SDATA_INx RIGHT-JUSTIFIED MSB LSB MODE t t SIH SIH 8-BIT CLOCKS (24-BIT DATA) 12-BIT CLOCKS (20-BIT DATA) 14-BIT CLOCKS (18-BIT DATA)

02

16-BIT CLOCKS

0 8-

(16-BIT DATA)

79 05 Figure 2. Serial Input Port Timing

tCLS tCLH t t CLPH CCPL CLATCH tCCPH CCLK CDATA tCDH tCDS COUT t

4

COD

00 8- 79 05 Figure 3. SPI Port Timing

t t SCH DS tSCH SDA tSCR tSCLH SCL

5 0 0

t

8-

SCLL t tSCS t SCF BFT

79 05 Figure 4. I2C Port Timing Rev. D | Page 8 of 52 Document Outline FEATURES APPLICATIONS GENERAL DESCRIPTION TABLE OF CONTENTS REVISION HISTORY FUNCTIONAL BLOCK DIAGRAM SPECIFICATIONS ANALOG PERFORMANCE DIGITAL INPUT/OUTPUT POWER PLL AND OSCILLATOR REGULATOR DIGITAL TIMING SPECIFICATIONS Digital Timing Diagrams ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS SYSTEM BLOCK DIAGRAM THEORY OF OPERATION INITIALIZATION POWER-UP SEQUENCE CONTROL REGISTERS SETUP DSP Core Control Register (Address 2076) DAC Setup Register (Address 2087) RECOMMENDED PROGRAM/PARAMETER LOADING PROCEDURE POWER REDUCTION MODES USING THE OSCILLATOR SETTING MASTER CLOCK/PLL MODE VOLTAGE REGULATOR AUDIO ADCs AUDIO DACs CONTROL PORTS I2C PORT Addressing I2C Read and Write Operations SPI PORT Chip Address R/ Subaddress Data Bytes SELF-BOOT EEPROM Format Writeback SIGNAL PROCESSING NUMERIC FORMATS Numerical Format: 5.23 PROGRAMMING RAMS AND REGISTERS ADDRESS MAPS PARAMETER RAM Direct Read/Write Safeload Write DATA RAM READ/WRITE DATA FORMATS CONTROL REGISTER MAP CONTROL REGISTER DETAILS ADDRESS 2048 TO ADDRESS 2055 (0x0800 TO 0x0807)—INTERFACE REGISTERS ADDRESS 2056 (0x0808)—GPIO PIN SETTING REGISTER ADDRESS 2057 TO ADDRESS 2060 (0x0809 TO 0x080C)—AUXILIARY ADC DATA REGISTERS ADDRESS 2064 TO ADDRESS 2068 (0x0810 TO 0x0814)—SAFELOAD DATA REGISTERS ADDRESS 2069 TO ADDRESS 2073 (0x0815 TO 0x0819)—SAFELOAD ADDRESS REGISTERS ADDRESS 2074 TO ADDRESS 2075 (0x081A TO 0x081B)—DATA CAPTURE REGISTERS ADDRESS 2076 (0x081C)—DSP CORE CONTROL REGISTER ADDRESS 2078 (0x081E)—SERIAL OUTPUT CONTROL REGISTER ADDRESS 2079 (0x081F)—SERIAL INPUT CONTROL REGISTER ADDRESS 2080 TO ADDRESS 2081 (0x0820 TO 0x0821)—MULTIPURPOSE PIN CONFIGURATION REGISTERS ADDRESS 2082 (0x0822)—AUXILIARY ADC AND POWER CONTROL REGISTER ADDRESS 2084 (0x0824)—AUXILIARY ADC ENABLE REGISTER ADDRESS 2086 (0x0826)—OSCILLATOR POWER-DOWN REGISTER ADDRESS 2087 (0x0827)—DAC SETUP MULTIPURPOSE PINS AUXILIARY ADC GENERAL-PURPOSE INPUT/OUTPUT PINS SERIAL DATA INPUT/OUTPUT PORTS LAYOUT RECOMMENDATIONS PARTS PLACEMENT GROUNDING TYPICAL APPLICATION SCHEMATICS SELF-BOOT MODE I2C CONTROL SPI CONTROL OUTLINE DIMENSIONS ORDERING GUIDE

Купить ADAU1702JSTZ на РадиоЛоцман.Цены — от 14 до 1 616 ₽

Купить ADAU1702JSTZ на РадиоЛоцман.Цены — от 14 до 1 616 ₽