Datasheet ADP5043 (Analog Devices)

| Производитель | Analog Devices |

| Описание | Micro-PMU with 0.8 A Buck, 300 mA LDO, Supervisory, Watchdog, and Manual Reset |

| Страниц / Страница | 30 / 1 — Micro PMU with 800 mA Buck, 300 mA LDO,. Supervisory, Watchdog, and … |

| Версия | B |

| Формат / Размер файла | PDF / 1.5 Мб |

| Язык документа | английский |

Micro PMU with 800 mA Buck, 300 mA LDO,. Supervisory, Watchdog, and Manual Reset. Data Sheet. ADP5043. FEATURES

Модельный ряд для этого даташита

Текстовая версия документа

Micro PMU with 800 mA Buck, 300 mA LDO, Supervisory, Watchdog, and Manual Reset Data Sheet ADP5043 FEATURES GENERAL DESCRIPTION Input voltage range: 2.3 V to 5.5 V

The ADP5043 combines one high performance buck regulator

One 800 mA buck regulator

and one low dropout (LDO) regulator in a small 20-lead LFCSP

One 300 mA LDO

to meet demanding performance and board space requirements.

20-lead, 4 mm × 4 mm LFCSP package

The high switching frequency of the buck regulator enables use

Initial regulator accuracy: ±1%

of tiny multilayer external components and minimizes board space.

Overcurrent and thermal protection Soft start

The MODE pin selects the buck’s mode of operation. When set

Undervoltage lockout

to logic high, the buck regulator operates in forced PWM mode.

Open-drain processor reset with threshold monitoring

When the MODE pin is set to logic low, the buck regulator

±1.5% threshold accuracy over the full temperate range

operates in PWM mode when the load is around the nominal

Guaranteed reset output valid to V

value. When the load current falls below a predefined threshold,

CC = 1 V Dual watchdog for secure systems

the regulator operates in power save mode (PSM) improving

Watchdog 1 controls reset

the light-load efficiency.

Watchdog 2 controls reset and regulators power cycle

The low quiescent current, low dropout voltage, and wide input

Buck regulator key specifications

voltage range of the ADP5043 LDO extend the battery life of

Current-mode topology for excellent transient response

portable devices. The LDO maintains a power supply rejection

3 MHz operating frequency

of greater than 60 dB for frequencies as high as 10 kHz while

Uses tiny multilayer inductors and capacitors

operating with a low headroom voltage.

Mode pin selects forced PWM or auto PFM/PSM modes

Each regulator is activated by a high level on the respective

100% duty cycle low dropout mode

enable pin. The ADP5043 is available with factory programmable

LDO key specifications

default output voltages and can be set to a wide range of options.

Low VIN from 1.7 V to 5.5 V Stable with1 μF ceramic output capacitors

The ADP5043 contains supervisory circuits that monitor

High PSRR, 60 dB up to 1 kHz/10 kHz

power supply voltage levels and code execution integrity in

Low output noise

microprocessor-based systems. The ADP5043 also provides

Low dropout voltage: 150 mV at 300 mA load

power-on reset signals. An on-chip dual watchdog timer can

−40°C to +125°C junction temperature range

reset the microprocessor or power cycle the system (Watchdog 2) if it fails to strobe within a preset timeout period.

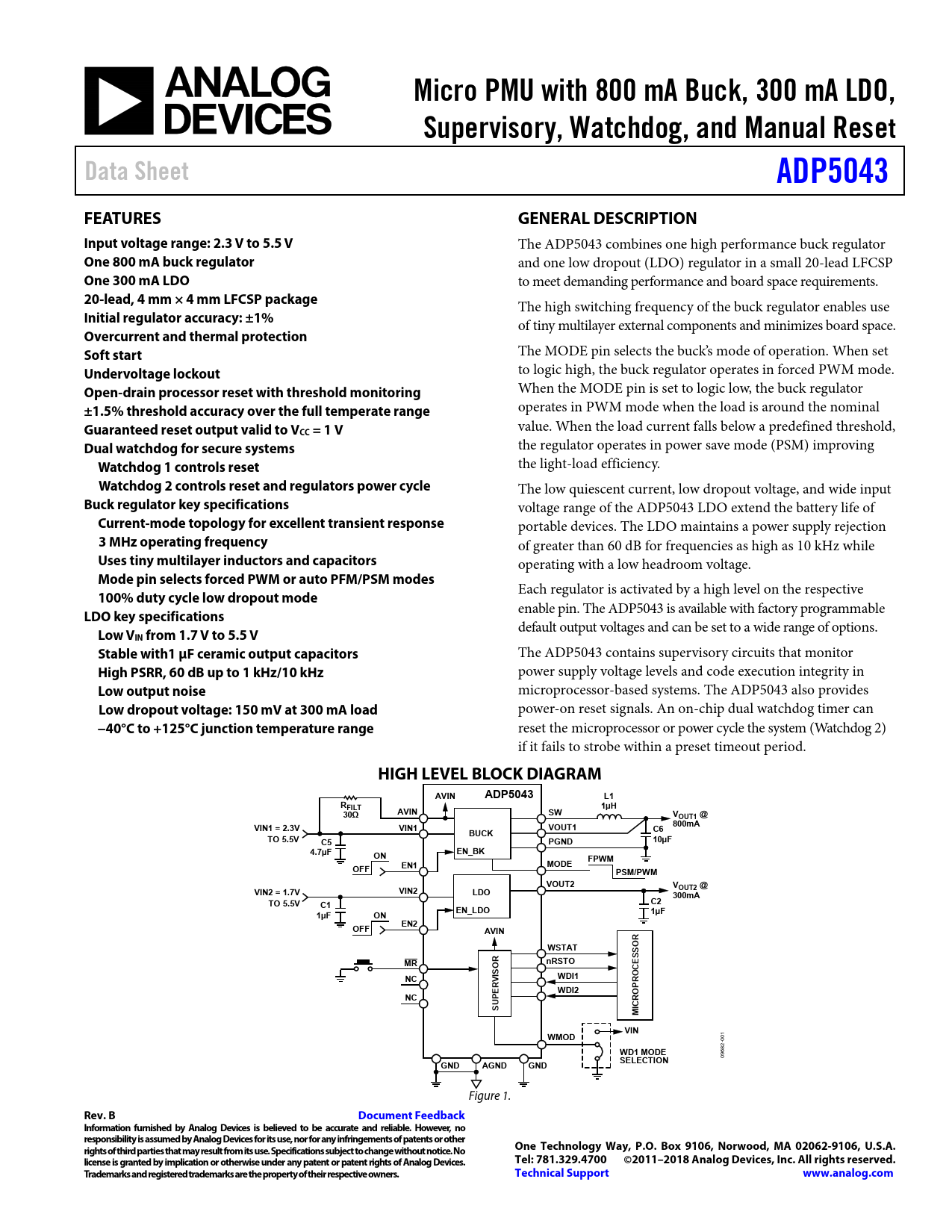

HIGH LEVEL BLOCK DIAGRAM AVIN ADP5043 L1 RFILT 1µH AVIN SW 30Ω VOUT1 @ VIN1 = 2.3V VIN1 VOUT1 800mA C6 BUCK TO 5.5V C5 PGND 10µF 4.7µF EN_BK ON FPWM MODE EN1 OFF PSM/PWM VOUT2 V VIN2 = 1.7V VIN2 LDO OUT2 @ 300mA C2 TO 5.5V C1 EN_LDO 1µF 1µF ON EN2 OFF AVIN R WSTAT MR R nRSTO ESSO C SO O NC VI WDI1 PR WDI2 O NC PER R C SU MI VIN WMOD

001

WD1 MODE

682-

SELECTION

09

GND AGND GND

Figure 1.

Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2011–2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

Document Outline FEATURES GENERAL DESCRIPTION HIGH LEVEL BLOCK DIAGRAM TABLE OF CONTENTS REVISION HISTORY SPECIFICATIONS GENERAL SPECIFICATIONS SUPERVISORY SPECIFICATIONS BUCK SPECIFICATIONS LDO SPECIFICATIONS INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS THERMAL DATA THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS THEORY OF OPERATION POWER MANAGEMENT UNIT Thermal Protection Undervoltage Lockout Enable/Shutdown BUCK SECTION Control Scheme PWM Mode Power Save Mode (PSM) PSM Current Threshold Short-Circuit Protection Soft Start Current Limit 100% Duty Operation LDO SECTION SUPERVISORY SECTION Reset Output Manual Reset Input Watchdog 1 Input Watchdog 2 Input Watchdog Status Indicator APPLICATIONS INFORMATION BUCK EXTERNAL COMPONENT SELECTION Inductor Output Capacitor Input Capacitor LDO CAPACITOR SELECTION Output Capacitor Input Bypass Capacitor Input and Output Capacitor Properties SUPERVISORY SECTION Watchdog 1 Input Current Negative-Going VCC Transients Watchdog Software Considerations PCB LAYOUT GUIDELINES POWER DISSIPATION/THERMAL CONSIDERATIONS Buck Regulator Power Dissipation LDO Regulator Power Dissipation Junction Temperature EVALUATION BOARD SCHEMATICS AND ARTWORK SUGGESTED LAYOUT BILL OF MATERIALS APPLICATION DIAGRAM FACTORY PROGRAMMABLE OPTIONS OUTLINE DIMENSIONS ORDERING GUIDE

Купить ADP5043ACPZ-1-R7 на РадиоЛоцман.Цены — от 90 до 24 990 ₽

Купить ADP5043ACPZ-1-R7 на РадиоЛоцман.Цены — от 90 до 24 990 ₽