Datasheet ADXL354, ADXL355 (Analog Devices) - 10

| Производитель | Analog Devices |

| Описание | Low Noise, Low Drift, Low Power 3-Axis Accelerometer with digital output |

| Страниц / Страница | 42 / 10 — ADXL354/ADXL355. Data Sheet. Y D. CS/SCL 1. 11 VSUPPLY. SCLK/VSSIO 2. … |

| Версия | A |

| Формат / Размер файла | PDF / 1.6 Мб |

| Язык документа | английский |

ADXL354/ADXL355. Data Sheet. Y D. CS/SCL 1. 11 VSUPPLY. SCLK/VSSIO 2. ADXL355. 10 V1P8ANA. TOP VIEW. MOSI/SDA 3. (Not to Scale). VSS

38 предложений от 17 поставщиков Датчики Ускорения, Accelerometer Triple ±2.048g/±4.096g/±8.192g 3.3V 14Pin CLLCC Tray |

| ADXL355BEZ()

Analog Devices | от 138 ₽ | |

| ADXL355BEZ-RL7

Analog Devices | 4 745 ₽ | |

| ADXL355BEZ

Analog Devices | от 10 342 ₽ | |

| ADXL355BEZ-RL7

Analog Devices | по запросу | |

Модельный ряд для этого даташита

Текстовая версия документа

ADXL354/ADXL355 Data Sheet Y D T2 T1 DR IN IN 14 13 12 CS/SCL 1 11 VSUPPLY Y SCLK/VSSIO 2 ADXL355 10 V1P8ANA TOP VIEW MOSI/SDA 3 (Not to Scale) 9 VSS X MISO/ASEL 4 8 V1P8DIG Z 5 6 7 O O D E DDI SSI V V V R

006 05-

RESE

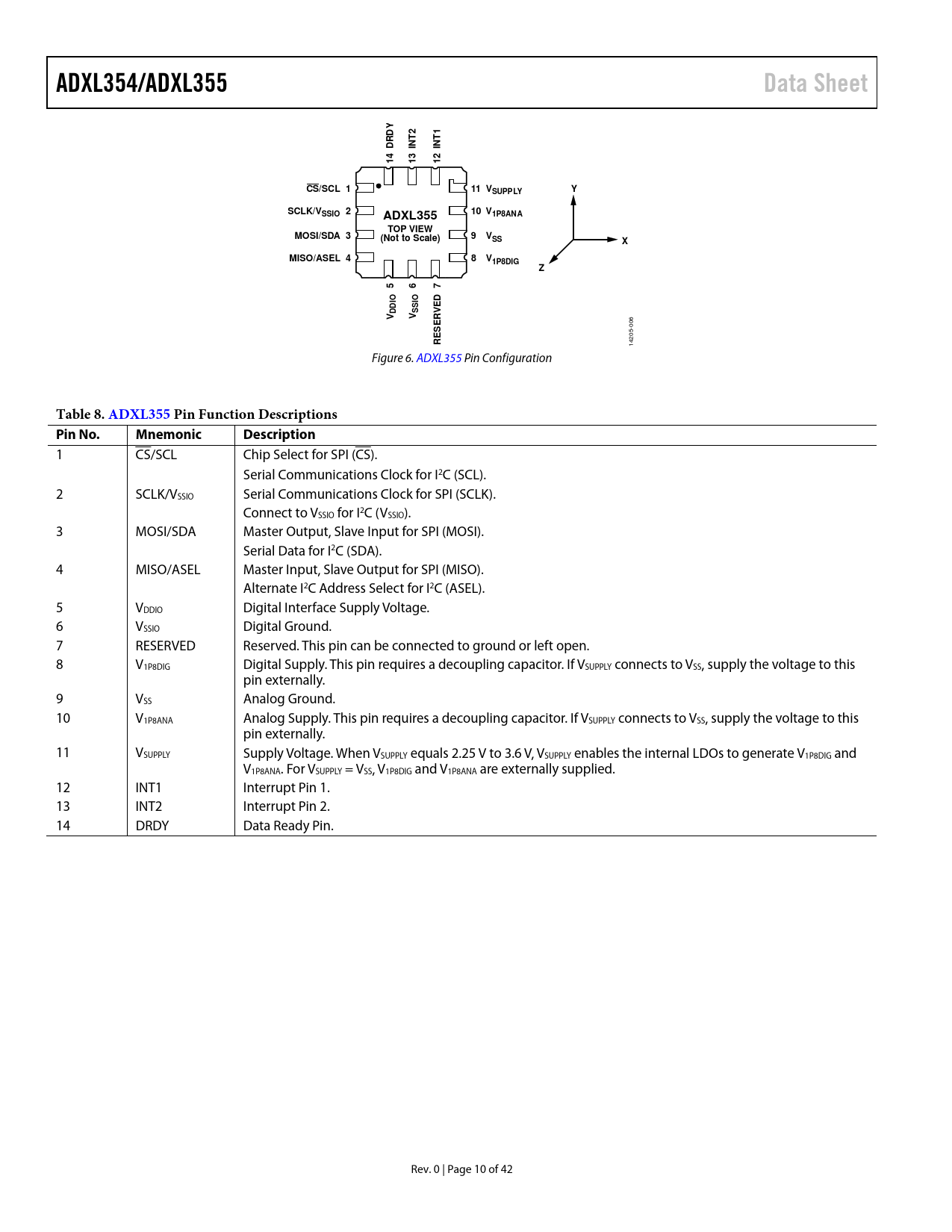

142 Figure 6. ADXL355 Pin Configuration

Table 8. ADXL355 Pi n Function Descriptions Pin No. Mnemonic Description

1 CS/SCL Chip Select for SPI (CS). Serial Communications Clock for I2C (SCL). 2 SCLK/VSSIO Serial Communications Clock for SPI (SCLK). Connect to VSSIO for I2C (VSSIO). 3 MOSI/SDA Master Output, Slave Input for SPI (MOSI). Serial Data for I2C (SDA). 4 MISO/ASEL Master Input, Slave Output for SPI (MISO). Alternate I2C Address Select for I2C (ASEL). 5 VDDIO Digital Interface Supply Voltage. 6 VSSIO Digital Ground. 7 RESERVED Reserved. This pin can be connected to ground or left open. 8 V1P8DIG Digital Supply. This pin requires a decoupling capacitor. If VSUPPLY connects to VSS, supply the voltage to this pin externally. 9 VSS Analog Ground. 10 V1P8ANA Analog Supply. This pin requires a decoupling capacitor. If VSUPPLY connects to VSS, supply the voltage to this pin externally. 11 VSUPPLY Supply Voltage. When VSUPPLY equals 2.25 V to 3.6 V, VSUPPLY enables the internal LDOs to generate V1P8DIG and V1P8ANA. For VSUPPLY = VSS, V1P8DIG and V1P8ANA are externally supplied. 12 INT1 Interrupt Pin 1. 13 INT2 Interrupt Pin 2. 14 DRDY Data Ready Pin. Rev. 0 | Page 10 of 42 Document Outline FEATURES APPLICATIONS GENERAL DESCRIPTION FUNCTIONAL BLOCK DIAGRAMS TABLE OF CONTENTS REVISION HISTORY SPECIFICATIONS ANALOG OUTPUT FOR THE ADXL354 DIGITAL OUTPUT FOR THE ADXL355 SPI DIGITAL INTERFACE CHARACTERISTICS FOR THE ADXL355 I2C DIGITAL INTERFACE CHARACTERISTICS FOR THE ADXL355 ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS ROOT ALLAN VARIANCE (RAV) ADXL355 CHARACTERISTICS THEORY OF OPERATION ANALOG OUTPUT DIGITAL OUTPUT AXES OF ACCELERATION SENSITIVITY POWER SEQUENCING POWER SUPPLY DESCRIPTION VSUPPLY V1P8ANA V1P8DIG VDDIO OVERRANGE PROTECTION SELF TEST FILTER SERIAL COMMUNICATIONS SPI PROTOCOL I2C PROTOCOL READING ACCELERATION OR TEMPERATURE DATA FROM THE INTERFACE FIFO INTERRUPTS DATA_RDY DRDY PIN FIFO_FULL FIFO_OVR ACTIVITY NVM_BUSY EXTERNAL SYNCHRONIZATION AND INTERPOLATION EXT_SYNC = 00—No External Sync or Interpolation EXT_SYNC = 10—External Sync with Interpolation EXT_SYNC = 01—External Sync and External Clock ADXL355 REGISTER MAP REGISTER DEFINITIONS ANALOG DEVICES ID REGISTER Address: 0x00, Reset: 0xAD, Name: DEVID_AD ANALOG DEVICES MEMS ID REGISTER Address: 0x01, Reset: 0x1D, Name: DEVID_MST DEVICE ID REGISTER Address: 0x02, Reset: 0xED, Name: PARTID PRODUCT REVISION ID REGISTER Address: 0x03, Reset: 0x00, Name: REVID STATUS REGISTER Address: 0x04, Reset: 0x00, Name: STATUS FIFO ENTRIES REGISTER Address: 0x05, Reset: 0x00, Name: FIFO_ENTRIES TEMPERATURE DATA REGISTERS Address: 0x06, Reset: 0x00, Name: TEMP2 Address: 0x07, Reset: 0x00, Name: TEMP1 X-AXIS DATA REGISTERS Address: 0x08, Reset: 0x00, Name: XDATA3 Address: 0x09, Reset: 0x00, Name: XDATA2 Address: 0x0A, Reset: 0x00, Name: XDATA1 Y-AXIS DATA REGISTERS Address: 0x0B, Reset: 0x00, Name: YDATA3 Address: 0x0C, Reset: 0x00, Name: YDATA2 Address: 0x0D, Reset: 0x00, Name: YDATA1 Z-AXIS DATA REGISTERS Address: 0x0E, Reset: 0x00, Name: ZDATA3 Address: 0x0F, Reset: 0x00, Name: ZDATA2 Address: 0x10, Reset: 0x00, Name: ZDATA1 FIFO ACCESS REGISTER Address: 0x11, Reset: 0x00, Name: FIFO_DATA X-AXIS OFFSET TRIM REGISTERS Address: 0x1E, Reset: 0x00, Name: OFFSET_X_H Address: 0x1F, Reset: 0x00, Name: OFFSET_X_L Y-AXIS OFFSET TRIM REGISTERS Address: 0x20, Reset: 0x00, Name: OFFSET_Y_H Address: 0x21, Reset: 0x00, Name: OFFSET_Y_L Z-AXIS OFFSET TRIM REGISTERS Address: 0x22, Reset: 0x00, Name: OFFSET_Z_H Address: 0x23, Reset: 0x00, Name: OFFSET_Z_L ACTIVITY ENABLE REGISTER Address: 0x24, Reset: 0x00, Name: ACT_EN ACTIVITY THRESHOLD REGISTERS Address: 0x25, Reset: 0x00, Name: ACT_THRESH_H Address: 0x26, Reset: 0x00, Name: ACT_THRESH_L ACTIVITY COUNT REGISTER Address: 0x27, Reset: 0x01, Name: ACT_COUNT FILTER SETTINGS REGISTER Address: 0x28, Reset: 0x00, Name: Filter FIFO SAMPLES REGISTER Address: 0x29, Reset: 0x60, Name: FIFO_SAMPLES INTERRUPT PIN (INTx) FUNCTION MAP REGISTER Address: 0x2A, Reset: 0x00, Name: INT_MAP DATA SYNCHRONIZATION Address: 0x2B, Reset: 0x00, Name: Sync I2C SPEED, INTERRUPT POLARITY, AND RANGE REGISTER Address: 0x2C, Reset: 0x81, Name: Range POWER CONTROL REGISTER Address: 0x2D, Reset: 0x01, Name: POWER_CTL SELF TEST REGISTER Address: 0x2E, Reset: 0x00, Name: SELF_TEST RESET REGISTER Address: 0x2F, Reset: 0x00, Name: Reset RECOMMENDED SOLDERING PROFILE PCB FOOTPRINT PATTERN PACKAGING AND ORDERING INFORMATION OUTLINE DIMENSIONS BRANDING INFORMATION ORDERING GUIDE

Купить ADXL355BEZ на РадиоЛоцман.Цены — от 138 до 307 996 ₽

Купить ADXL355BEZ на РадиоЛоцман.Цены — от 138 до 307 996 ₽