Datasheet MCP4728 (Microchip) - 4

| Производитель | Microchip |

| Описание | 12-Bit, Quad Digital-to-Analog Converter with EEPROM Memory |

| Страниц / Страница | 68 / 4 — MCP4728. ELECTRICAL CHARACTERISTICS (CONTINUED). Electrical … |

| Формат / Размер файла | PDF / 3.0 Мб |

| Язык документа | английский |

MCP4728. ELECTRICAL CHARACTERISTICS (CONTINUED). Electrical Specifications:. Parameter. Symbol. Min. Typical. Max. Units. Conditions

Модельный ряд для этого даташита

Текстовая версия документа

link to page 3 link to page 3 link to page 3 link to page 3 link to page 14 link to page 15 link to page 3

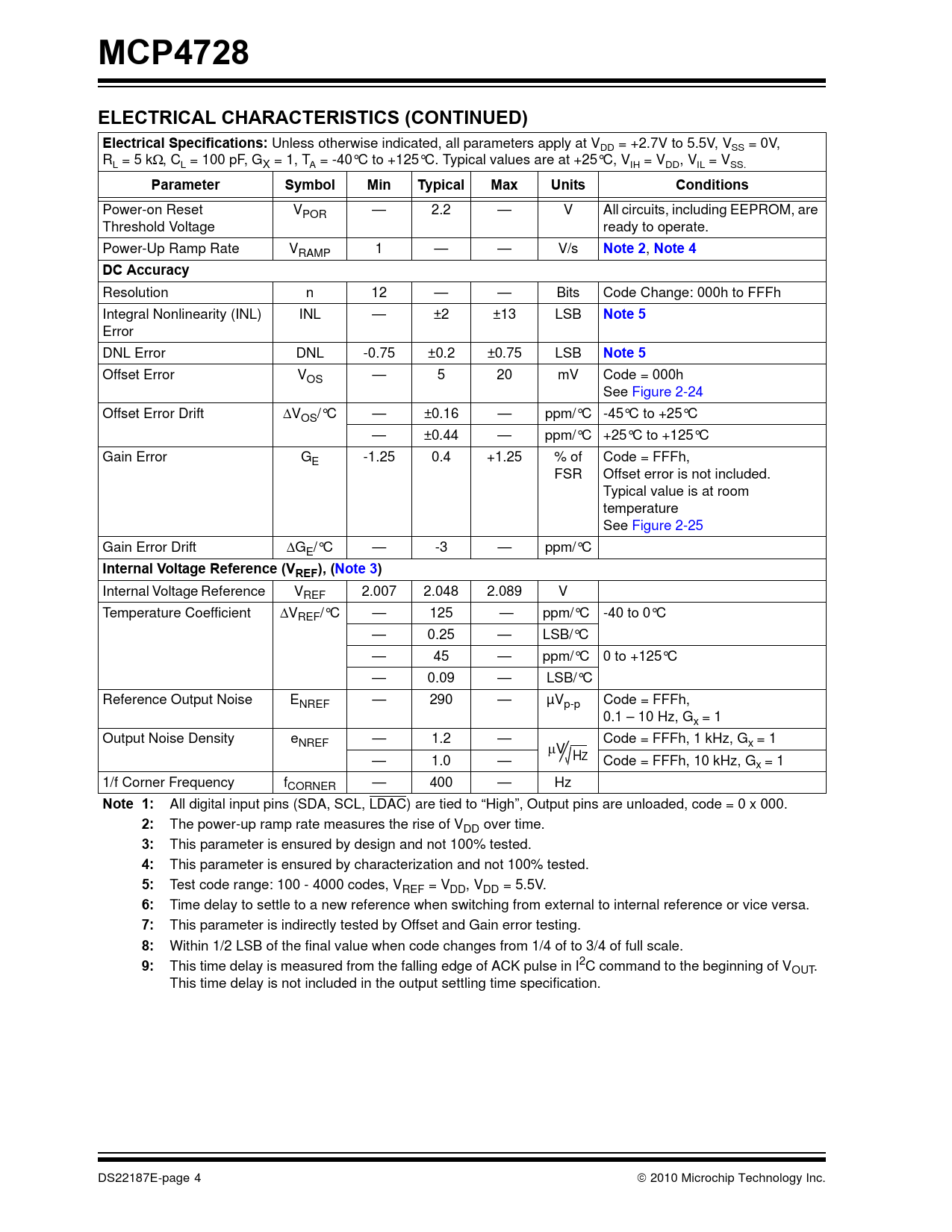

MCP4728 ELECTRICAL CHARACTERISTICS (CONTINUED) Electrical Specifications:

Unless otherwise indicated, all parameters apply at VDD = +2.7V to 5.5V, VSS = 0V, RL = 5 kΩ, CL = 100 pF, GX = 1, TA = -40°C to +125°C. Typical values are at +25°C, VIH = VDD, VIL = VSS.

Parameter Symbol Min Typical Max Units Conditions

Power-on Reset VPOR — 2.2 — V All circuits, including EEPROM, are Threshold Voltage ready to operate. Power-Up Ramp Rate VRAMP 1 — — V/s

Note 2

,

Note 4 DC Accuracy

Resolution n 12 — — Bits Code Change: 000h to FFFh Integral Nonlinearity (INL) INL — ±2 ±13 LSB

Note 5

Error DNL Error DNL -0.75 ±0.2 ±0.75 LSB

Note 5

Offset Error VOS — 5 20 mV Code = 000h See Figure 2-24 Offset Error Drift ΔVOS/°C — ±0.16 — ppm/°C -45°C to +25°C — ±0.44 — ppm/°C +25°C to +125°C Gain Error GE -1.25 0.4 +1.25 % of Code = FFFh, FSR Offset error is not included. Typical value is at room temperature See Figure 2-25 Gain Error Drift ΔGE/°C — -3 — ppm/°C

Internal Voltage Reference (VREF), (Note 3 )

Internal Voltage Reference VREF 2.007 2.048 2.089 V Temperature Coefficient ΔVREF/°C — 125 — ppm/°C -40 to 0°C — 0.25 — LSB/°C — 45 — ppm/°C 0 to +125°C — 0.09 — LSB/°C Reference Output Noise ENREF — 290 — µVp-p Code = FFFh, 0.1 – 10 Hz, Gx = 1 Output Noise Density eNREF — 1.2 — Code = FFFh, 1 kHz, Gx = 1 μV — 1.0 — HZ Code = FFFh, 10 kHz, Gx = 1 1/f Corner Frequency fCORNER — 400 — Hz

Note 1:

All digital input pins (SDA, SCL, LDAC) are tied to “High”, Output pins are unloaded, code = 0 x 000.

2:

The power-up ramp rate measures the rise of VDD over time.

3:

This parameter is ensured by design and not 100% tested.

4:

This parameter is ensured by characterization and not 100% tested.

5:

Test code range: 100 - 4000 codes, VREF = VDD, VDD = 5.5V.

6:

Time delay to settle to a new reference when switching from external to internal reference or vice versa.

7:

This parameter is indirectly tested by Offset and Gain error testing.

8:

Within 1/2 LSB of the final value when code changes from 1/4 of to 3/4 of full scale.

9:

This time delay is measured from the falling edge of ACK pulse in I2C command to the beginning of VOUT. This time delay is not included in the output settling time specification. DS22187E-page 4 © 2010 Microchip Technology Inc. Document Outline 1.0 Electrical Characteristics FIGURE 1-1: I2C Bus Timing Data. FIGURE 1-2: LDAC Pin Timing vs. VOUT Update. 2.0 Typical Performance Curves FIGURE 2-1: INL vs. Code (TA = +25°C). FIGURE 2-2: INL vs. Code (TA = +25°C). FIGURE 2-3: INL vs. Code (TA = +25°C). FIGURE 2-4: DNL vs. Code (TA = +25°C). FIGURE 2-5: DNL vs. Code (TA = +25°C). FIGURE 2-6: DNL vs. Code (TA = +25°C). FIGURE 2-7: INL vs. Code (TA = +25°C). FIGURE 2-8: INL vs. Code (TA = +25°C). FIGURE 2-9: INL vs. Code and Temperature. FIGURE 2-10: DNL vs. Code (TA = +25°C). FIGURE 2-11: DNL vs. Code (TA = +25°C). FIGURE 2-12: DNL vs. Code and Temperature. FIGURE 2-13: INL vs. Code and Temperature. FIGURE 2-14: INL vs. Code and Temperature. FIGURE 2-15: INL vs. Code and Temperature. FIGURE 2-16: DNL vs. Code and Temperature. FIGURE 2-17: DNL vs. Code and Temperature. FIGURE 2-18: DNL vs. Code and Temperature. FIGURE 2-19: INL vs. Code and Temperature. FIGURE 2-20: Full Scale Error vs. Temperature (Code = FFFh, VREF = Internal). FIGURE 2-21: Full Scale Error vs. Temperature (Code = FFFh, VREF = VDD). FIGURE 2-22: DNL vs. Code and Temperature. FIGURE 2-23: Zero Scale Error vs. Temperature (Code = 000h, VREF = Internal). FIGURE 2-24: Offset Error (Zero Scale Error). FIGURE 2-25: Absolute DAC Output Error (VDD = 5.5V). FIGURE 2-26: Full Scale Settling Time (VREF = VDD, VDD = 5V, UDAC = 1, Code Change: 000h to FFFh). FIGURE 2-27: Half Scale Settling Time (VREF = VDD, VDD = 5V, UDAC = 1, Code Change: 000h to 7FFh). FIGURE 2-28: Full Scale Settling Time (VREF = Internal, VDD = 5V, UDAC = 1, Gain = x1, Code Change: 000h to FFFh). FIGURE 2-29: Full Scale Settling Time (VREF = VDD, VDD = 5V, UDAC = 1, Code Change: FFFh to 000h). FIGURE 2-30: Half Scale Settling Time (VREF = VDD, VDD = 5V, UDAC = 1, Code Change: 7FFh to 000h). FIGURE 2-31: Full Scale Settling Time (VREF = Internal, VDD = 5V, UDAC = 1, Gain = x1, Code Change: FFFh to 000h). FIGURE 2-32: Half Scale Settling Time (VREF = Internal, VDD = 5V, UDAC = 1, Gain = x1, Code Change: 000h to 7FFh). FIGURE 2-33: Exiting Power Down Mode (Code: FFFh, VREF = Internal, VDD = 5V, Gain = x1, for all Channels.). FIGURE 2-34: Entering Power Down Mode (Code: FFFh, VREF = Internal, VDD = 5V, Gain = x1, PD1= PD0 = 1, No External Load). FIGURE 2-35: Half Scale Settling Time (VREF = Internal, VDD = 5V, UDAC = 1, Gain = x1, Code Change: 7FFh to 000h). FIGURE 2-36: Exiting Power Down Mode (Code: FFFh, VREF = VDD, VDD = 5V, for all Channels). FIGURE 2-37: Entering Power Down Mode (Code: FFFh, VREF = VDD, VDD = 5V, PD1= PD0 = 1, No External Load). FIGURE 2-38: VOUT Time Delay when VREF changes from Internal Reference to VDD. FIGURE 2-39: VOUT Time Delay when VREF changes from VDD to Internal Reference. FIGURE 2-40: Channel Cross Talk (VREF = VDD, VDD = 5V). FIGURE 2-41: Code Change Glitch (VREF = External, VDD = 5V, No External Load), Code Change: 800h to 7FFh. FIGURE 2-42: Code Change Glitch (VREF = Internal, VDD = 5V, Gain = 1, No External Load), Code Change: 800h to 7FFh. FIGURE 2-43: VOUT vs. Resistive Load. FIGURE 2-44: IDD vs. Temperature (VREF = Vdd, VDD = 5V, Code = FFFh). FIGURE 2-45: IDD vs. Temperature (VREF = VDD, VDD = 2.7V, Code = FFFh). FIGURE 2-46: IDD vs. Temperature (VREF = VDD, All channels are in Normal Mode, Code = FFFh). FIGURE 2-47: IDD vs. Temperature (VREF = Internal, VREF = 5V, Code = FFFh). FIGURE 2-48: IDD vs. Temperature (VREF = Internal, VDD = 2.7V, Code = FFFh). FIGURE 2-49: IDD vs. Temperature (VREF = Internal , All Channels are in Normal Mode, Code = FFFh). FIGURE 2-50: IDD vs. Temperature (VREF = Internal , All Channels are in Powered Down). FIGURE 2-51: Source Current Capability (VREF = VDD, Code = FFFh). FIGURE 2-52: Sink Current Capability (VREF = VDD, Code = 000h). 3.0 Pin Descriptions TABLE 3-1: Pin Function Table 3.1 Supply Voltage Pins (VDD, VSS) 3.2 Serial Clock Pin (SCL) 3.3 Serial Data Pin (SDA) 3.4 LDAC Pin 3.5 RDY/BSY Status Indicator Pin 3.6 Analog Output Voltage Pins (VOUT A, VOUT B, VOUT C, VOUT D) 4.0 Theory of Device Operation 4.1 Power-on Reset (POR) 4.2 Reset Conditions 4.3 Output Amplifier 4.4 DAC Input Registers and Non-Volatile EEPROM Memory TABLE 4-1: Input Register MAP (Volatile) TABLE 4-2: EEPROM Memory MAP and FACTORY DEFAULT Settings TABLE 4-3: Configuration Bits 4.5 Voltage Reference 4.6 LSB Size TABLE 4-4: LSB SIZES (example) 4.7 DAC Output Voltage 4.8 Output Voltage Update TABLE 4-5: LDAC and UDAC conditions Vs. Output Update 4.9 DAC Input Code Vs. DAC Analog Output TABLE 4-6: DAC Input Code Vs. Analog Output (VOUT) 4.10 Normal and Power-Down Modes TABLE 4-7: Power-down bits FIGURE 4-1: Output Stage for Power-Down Mode. 5.0 I2C Serial Interface Communications 5.1 Overview of I2C Serial Interface Communications 5.2 I2C BUS CHARACTERISTICS FIGURE 5-1: Data Transfer Sequence On The Serial Bus. 5.3 MCP4728 Device Addressing FIGURE 5-2: Device Addressing. 5.4 I2C General Call Commands FIGURE 5-3: General Call Reset. FIGURE 5-4: General Call Wake-Up. FIGURE 5-5: General Call Software Update. FIGURE 5-6: General Call Read I2C Address. 5.5 Writing and Reading Registers and EEPROM 5.6 Write Commands for DAC Registers and EEPROM TABLE 5-1: Write Command Types TABLE 5-2: DAC Channel Selection Bits for Sequential Write Command FIGURE 5-7: Fast Write Command: Write DAC Input Registers Sequentially from Channel A to D. FIGURE 5-8: Multi-Write Command: Write Multiple DAC Input Registers. FIGURE 5-9: Sequential Write Command: Write DAC Input Registers and EEPROM Sequentially from Starting Channel to Channel D. The sequential input register starts with the "Starting Channel" and ends at Channel D. For example, if DAC1:DAC0 = 00, then i... FIGURE 5-10: Single Write Command: Write to a Single DAC Input Register and EEPROM. FIGURE 5-11: Write Command: Write I2C Address Bits to the DAC Registers and EEPROM. FIGURE 5-12: Write Command: Write Voltage Reference Selection Bit (VREF) to the DAC Input Registers. FIGURE 5-13: Write Command: Write Power-Down Selection Bits (PD1, PD0) to the DAC Input Registers. See Table 4-7 for the power-down bit setting. FIGURE 5-14: Write Command: Write Gain Selection Bit (GX) to the DAC Input Registers. FIGURE 5-15: Read Command and Device Outputs. 6.0 Terminology 6.1 Resolution 6.2 Least Significant Bit (LSB) 6.3 Integral Nonlinearity (INL) FIGURE 6-1: INL Accuracy. 6.4 Differential Nonlinearity (DNL) FIGURE 6-2: DNL Accuracy. 6.5 Offset Error FIGURE 6-3: Offset Error. 6.6 Gain Error 6.7 Full Scale Error (FSE) FIGURE 6-4: Gain Error and Full Scale Error. 6.8 Gain Error Drift 6.9 Offset Error Drift 6.10 Settling Time 6.11 Major-Code Transition Glitch 6.12 Digital Feedthrough 6.13 Analog Crosstalk 6.14 DAC-to-DAC Crosstalk 6.15 Power-Supply Rejection Ratio (PSRR) 7.0 Typical Applications 7.1 Connecting to I2C BUS Using Pull-Up Resistors FIGURE 7-1: Example of the MCP4728 Device Connection. FIGURE 7-2: I2C Bus Connection Test. 7.2 Layout Considerations 7.3 Power Supply Considerations 7.4 Using Power Saving Feature 7.5 Using Nonvolatile EEPROM Memory 7.6 Application Examples TABLE 7-1: Example: Setting Vout of each channel FIGURE 7-3: Using the MCP4728 for Set Point or Threshold Calibration. FIGURE 7-4: Sequential Write Command for Setting Test Points in Figure 7-3. FIGURE 7-5: Example of Writing Fast Write Command for Various VOUT. VREF = VDD For All Channels. 8.0 Development Support 8.1 Evaluation & Demonstration Boards FIGURE 8-1: MCP4728 Evaluation Board. FIGURE 8-2: Setup for the MCP4728 Evaluation Board with PICkit™ Serial Analyzer. FIGURE 8-3: Example of PICkit™ Serial User Interface. 9.0 Packaging Information 9.1 Package Marking Information Corporate Office Atlanta Boston Chicago Cleveland Fax: 216-447-0643 Dallas Detroit Kokomo Toronto Fax: 852-2401-3431 Australia - Sydney China - Beijing China - Shanghai India - Bangalore Korea - Daegu Korea - Seoul Singapore Taiwan - Taipei Fax: 43-7242-2244-393 Denmark - Copenhagen France - Paris Germany - Munich Italy - Milan Spain - Madrid UK - Wokingham Worldwide Sales and Service Trademarks Worldwide Sales