Datasheet MCP6V26, MCP6V27, MCP6V28 (Microchip) - 10

| Производитель | Microchip |

| Описание | The MCP6V26/7/8 family of operational amplifiers has input offset voltage correction for very low offset and offset drift |

| Страниц / Страница | 50 / 10 — MCP6V26/7/8. Note:. 160. 1)0,000. 10n. DD = 5.5V. 155. ts (A. (d 150. … |

| Формат / Размер файла | PDF / 2.2 Мб |

| Язык документа | английский |

MCP6V26/7/8. Note:. 160. 1)0,000. 10n. DD = 5.5V. 155. ts (A. (d 150. 1,000. VDD = 5.5V. rren. 145. DD = 2.3V. p o. 140. 100p. 100. ffset Cu. -L 135. , O. 130. 10p

Модельный ряд для этого даташита

Текстовая версия документа

MCP6V26/7/8 Note:

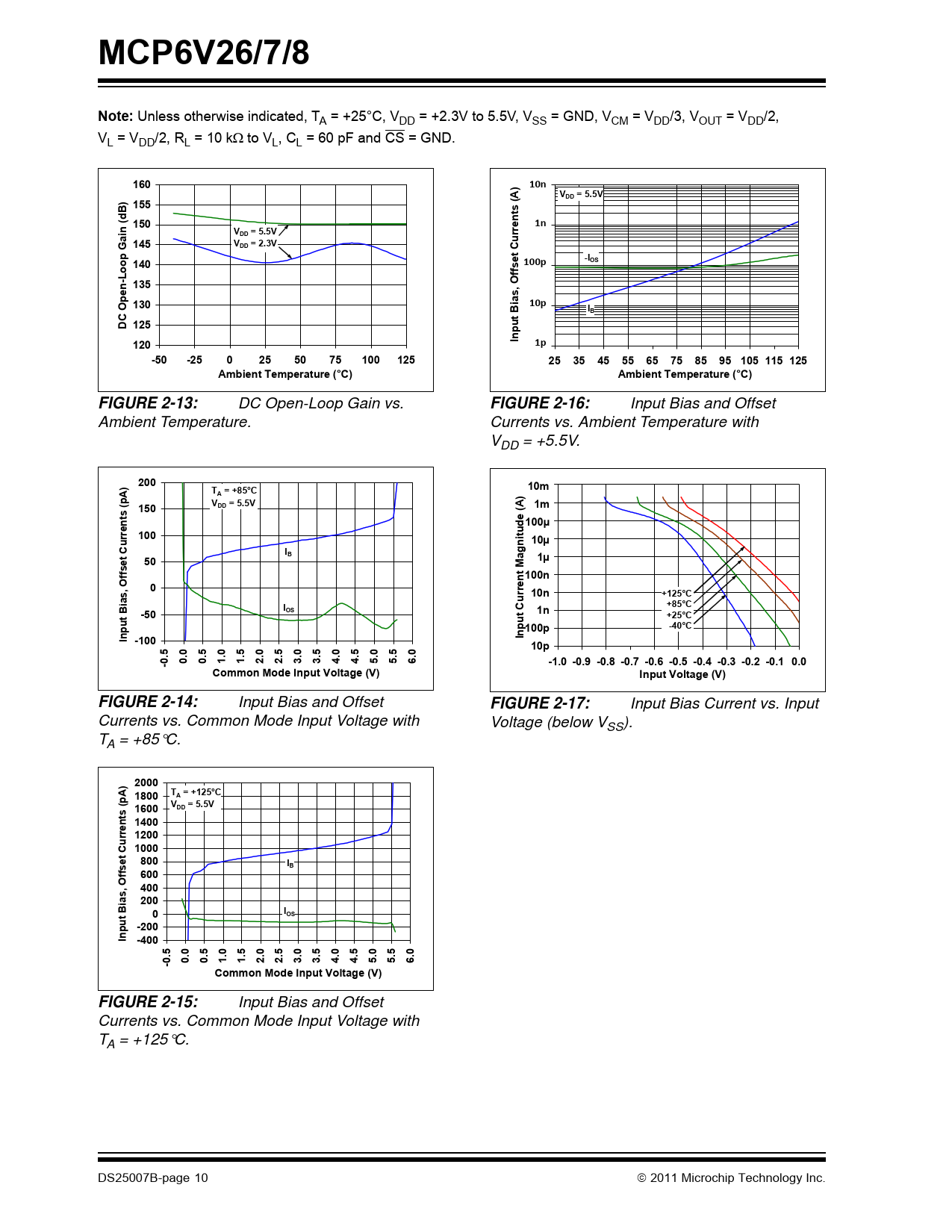

Unless otherwise indicated, TA = +25°C, VDD = +2.3V to 5.5V, VSS = GND, VCM = VDD/3, VOUT = VDD/2, VL = VDD/2, RL = 10 kΩ to VL, CL = 60 pF and CS = GND.

160 1)0,000 10n V ) DD = 5.5V 155 B ts (A (d 150 1,000 1n in VDD = 5.5V rren 145 V Ga DD = 2.3V p o -I 140 OS 100p o 100 ffset Cu -L 135 en , O p as 130 10 10p I t Bi B DC O 125 u p In 120 1 1p -50 -25 0 25 50 75 100 125 25 35 45 55 65 75 85 95 105 115 125 Ambient Temperature (°C) Ambient Temperature (°C) FIGURE 2-13:

DC Open-Loop Gain vs.

FIGURE 2-16:

Input Bias and Offset Ambient Temperature. Currents vs. Ambient Temperature with VDD = +5.5V.

200 ) 1.E-0 10 2 m A TA = +85°C p ) 1.E-03 150 VDD = 5.5V 1m ts ( 1.e (AE-0 10 4 0µ rren 100 itud u 1.E-05 10µ C I gn B a 50 1.E-06 1µ ffset 1.t ME-07 100n 0 1.rrenE-0 108 n +125°C as, O u +85°C Bi I -50 OS 1.t CE-09 1n +25°C 1.puE-10 -40°C 100p Input -100 In 1.E-1 101p .5 5 0 0 5 -0 0.0 0. 1. 1.5 2.0 2.5 3.0 3.5 4. 4. 5.0 5.5 6.0 -1.0 -0.9 -0.8 -0.7 -0.6 -0.5 -0.4 -0.3 -0.2 -0.1 0.0 Common Mode Input Voltage (V) Input Voltage (V) FIGURE 2-14:

Input Bias and Offset

FIGURE 2-17:

Input Bias Current vs. Input Currents vs. Common Mode Input Voltage with Voltage (below VSS). TA = +85°C.

2000 ) A 1800 TA = +125°C 1600 VDD = 5.5V ts (p 1400 rren 1200 u 1000 et C 800 IB ffs 600 , O 400 as 200 t Bi 0 IOS u p -200 In -400 0 5 0 -0.5 0.0 0.5 1.0 1.5 2. 2.5 3.0 3.5 4.0 4. 5. 5.5 6.0 Common Mode Input Voltage (V) FIGURE 2-15:

Input Bias and Offset Currents vs. Common Mode Input Voltage with TA = +125°C. DS25007B-page 10 © 2011 Microchip Technology Inc. Document Outline 1.0 Electrical Characteristics 1.1 Absolute Maximum Ratings † 1.2 Specifications TABLE 1-1: DC Electrical Specifications TABLE 1-2: AC Electrical Specifications TABLE 1-3: Digital Electrical Specifications TABLE 1-4: Temperature Specifications 1.3 Timing Diagrams FIGURE 1-1: Amplifier Start Up. FIGURE 1-2: Offset Correction Settling Time. FIGURE 1-3: Output Overdrive Recovery. FIGURE 1-4: Chip Select (MCP6V28). 1.4 Test Circuits FIGURE 1-5: AC and DC Test Circuit for Most Non-Inverting Gain Conditions. FIGURE 1-6: AC and DC Test Circuit for Most Inverting Gain Conditions. FIGURE 1-7: Test Circuit for Dynamic Input Behavior. 2.0 Typical Performance Curves 2.1 DC Input Precision FIGURE 2-1: Input Offset Voltage. FIGURE 2-2: Input Offset Voltage Drift. FIGURE 2-3: Input Offset Voltage Quadratic Temperature Coefficient. FIGURE 2-4: Input Offset Voltage vs. Power Supply Voltage with VCM = VCML. FIGURE 2-5: Input Offset Voltage vs. Power Supply Voltage with VCM = VCMH. FIGURE 2-6: Input Offset Voltage vs. Output Voltage. FIGURE 2-7: Input Offset Voltage vs. Common Mode Voltage with VDD = 2.3V. FIGURE 2-8: Input Offset Voltage vs. Common Mode Voltage with VDD = 5.5V. FIGURE 2-9: CMRR. FIGURE 2-10: PSRR. FIGURE 2-11: DC Open-Loop Gain. FIGURE 2-12: CMRR and PSRR vs. Ambient Temperature. FIGURE 2-13: DC Open-Loop Gain vs. Ambient Temperature. FIGURE 2-14: Input Bias and Offset Currents vs. Common Mode Input Voltage with TA = +85°C. FIGURE 2-15: Input Bias and Offset Currents vs. Common Mode Input Voltage with TA = +125°C. FIGURE 2-16: Input Bias and Offset Currents vs. Ambient Temperature with VDD = +5.5V. FIGURE 2-17: Input Bias Current vs. Input Voltage (below VSS). 2.2 Other DC Voltages and Currents FIGURE 2-18: Input Common Mode Voltage Headroom (Range) vs. Ambient Temperature. FIGURE 2-19: Output Voltage Headroom vs. Output Current. FIGURE 2-20: Output Voltage Headroom vs. Ambient Temperature. FIGURE 2-21: Output Short Circuit Current vs. Power Supply Voltage. FIGURE 2-22: Supply Current vs. Power Supply Voltage. FIGURE 2-23: Power On Reset Trip Voltage. FIGURE 2-24: Power On Reset Voltage vs. Ambient Temperature. 2.3 Frequency Response FIGURE 2-25: CMRR and PSRR vs. Frequency. FIGURE 2-26: Open-Loop Gain vs. Frequency with VDD = 2.3V. FIGURE 2-27: Open-Loop Gain vs. Frequency with VDD = 5.5V. FIGURE 2-28: Gain Bandwidth Product and Phase Margin vs. Ambient Temperature. FIGURE 2-29: Gain Bandwidth Product and Phase Margin vs. Common Mode Input Voltage. FIGURE 2-30: Gain Bandwidth Product and Phase Margin vs. Output Voltage. FIGURE 2-31: Closed-Loop Output Impedance vs. Frequency with VDD = 2.3V. FIGURE 2-32: Closed-Loop Output Impedance vs. Frequency with VDD = 5.5V. FIGURE 2-33: Channel-to-Channel Separation vs. Frequency. FIGURE 2-34: Maximum Output Voltage Swing vs. Frequency. 2.4 Input Noise and Distortion FIGURE 2-35: Input Noise Voltage Density and Integrated Input Noise Voltage vs. Frequency. FIGURE 2-36: Input Noise Voltage Density vs. Input Common Mode Voltage. FIGURE 2-37: Intermodulation Distortion vs. Frequency with VCM Disturbance (see Figure 1-7). FIGURE 2-38: Intermodulation Distortion vs. Frequency with VDD Disturbance (see Figure 1-7). FIGURE 2-39: Input Noise vs. Time with 1 Hz and 10 Hz Filters and VDD =2.3V. FIGURE 2-40: Input Noise vs. Time with 1 Hz and 10 Hz Filters and VDD =5.5V. 2.5 Time Response FIGURE 2-41: Input Offset Voltage vs. Time with Temperature Change. FIGURE 2-42: Input Offset Voltage vs. Time at Power Up. FIGURE 2-43: The MCP6V26/7/8 Device Shows No Input Phase Reversal with Overdrive. FIGURE 2-44: Non-inverting Small Signal Step Response. FIGURE 2-45: Non-inverting Large Signal Step Response. FIGURE 2-46: Inverting Small Signal Step Response. FIGURE 2-47: Inverting Large Signal Step Response. FIGURE 2-48: Slew Rate vs. Ambient Temperature. FIGURE 2-49: Output Overdrive Recovery vs. Time with G = -100 V/V. FIGURE 2-50: Output Overdrive Recovery Time vs. Inverting Gain. 2.6 Chip Select Response (MCP6V28 only) FIGURE 2-51: Chip Select Current vs. Power Supply Voltage. FIGURE 2-52: Power Supply Current vs. Chip Select Voltage with VDD = 2.3V. FIGURE 2-53: Power Supply Current vs. Chip Select Voltage with VDD = 5.5V. FIGURE 2-54: Chip Select Current vs. Chip Select Voltage. FIGURE 2-55: Chip Select Voltage, Output Voltage vs. Time with VDD = 2.3V. FIGURE 2-56: Chip Select Voltage, Output Voltage vs. Time with VDD = 5.5V. FIGURE 2-57: Chip Select Relative Logic Thresholds vs. Ambient Temperature. FIGURE 2-58: Chip Select Hysteresis. FIGURE 2-59: Chip Select Turn On Time vs. Ambient Temperature. FIGURE 2-60: Chip Select’s Pull-down Resistor (RPD) vs. Ambient Temperature. FIGURE 2-61: Quiescent Current in Shutdown vs. Power Supply Voltage. 3.0 Pin Descriptions TABLE 3-1: Pin Function Table 3.1 Analog Outputs 3.2 Analog Inputs 3.3 Power Supply Pins 3.4 Chip Select (CS) Digital Input 3.5 Exposed Thermal Pad (EP) 4.0 Applications 4.1 Overview of Auto-Zeroing Operation FIGURE 4-1: Simplified Auto-Zeroed Op Amp Functional Diagram. FIGURE 4-2: Normal Mode of Operation (f1); Equivalent Amplifier Diagram. FIGURE 4-3: Auto-zeroing Mode of Operation (f2); Equivalent Diagram. 4.2 Other Functional Blocks FIGURE 4-4: Simplified Analog Input ESD Structures. FIGURE 4-5: Protecting the Analog Inputs Against High Voltages. FIGURE 4-6: Protecting the Analog Inputs Against High Currents. 4.3 Application Tips FIGURE 4-7: Output Resistor, RISO, Stabilizes Capacitive Loads. FIGURE 4-8: Recommended RISO values for Capacitive Loads. FIGURE 4-9: Output Load. FIGURE 4-10: Amplifier with Parasitic Capacitance. FIGURE 4-11: Additional Supply Filtering. 4.4 Typical Applications FIGURE 4-12: Simple Design. FIGURE 4-13: High Performance Design. FIGURE 4-14: RTD Sensor. FIGURE 4-15: Thermocouple Sensor; Simplified Circuit. FIGURE 4-16: Thermocouple Sensor. FIGURE 4-17: Offset Correction. FIGURE 4-18: Precision Comparator. 5.0 Design Aids 5.1 SPICE Macro Model 5.2 FilterLab® Software 5.3 Microchip Advanced Part Selector (MAPS) 5.4 Analog Demonstration and Evaluation Boards 5.5 Application Notes 6.0 Packaging Information 6.1 Package Marking Information Appendix A: Revision History Appendix B: Offset Related Test Screens Product Identification System Trademarks Worldwide Sales and Service

Купить MCP6V27T-E/SN на РадиоЛоцман.Цены — от 59 до 274 ₽

Купить MCP6V27T-E/SN на РадиоЛоцман.Цены — от 59 до 274 ₽