Datasheet MCP6071, MCP6072, MCP6074 (Microchip) - 10

| Производитель | Microchip |

| Описание | The MCP6071 operational amplifier (op amps) has a low input offset voltage (±150 µV, maximum) and rail-to-rail input and output operation |

| Страниц / Страница | 40 / 10 — MCP6071/2/4. Note:. 150. 1.8. 180. 145. 1.6. 160. Gain Bandwidth Product. … |

| Формат / Размер файла | PDF / 1.3 Мб |

| Язык документа | английский |

MCP6071/2/4. Note:. 150. 1.8. 180. 145. 1.6. 160. Gain Bandwidth Product. (d 140. duc. 1.4. 140. (°). a 135. 1.2. 120. 130. z) 1.0. 100. arg. op G 125. 0.8. (MH. e M

Модельный ряд для этого даташита

Текстовая версия документа

MCP6071/2/4 Note:

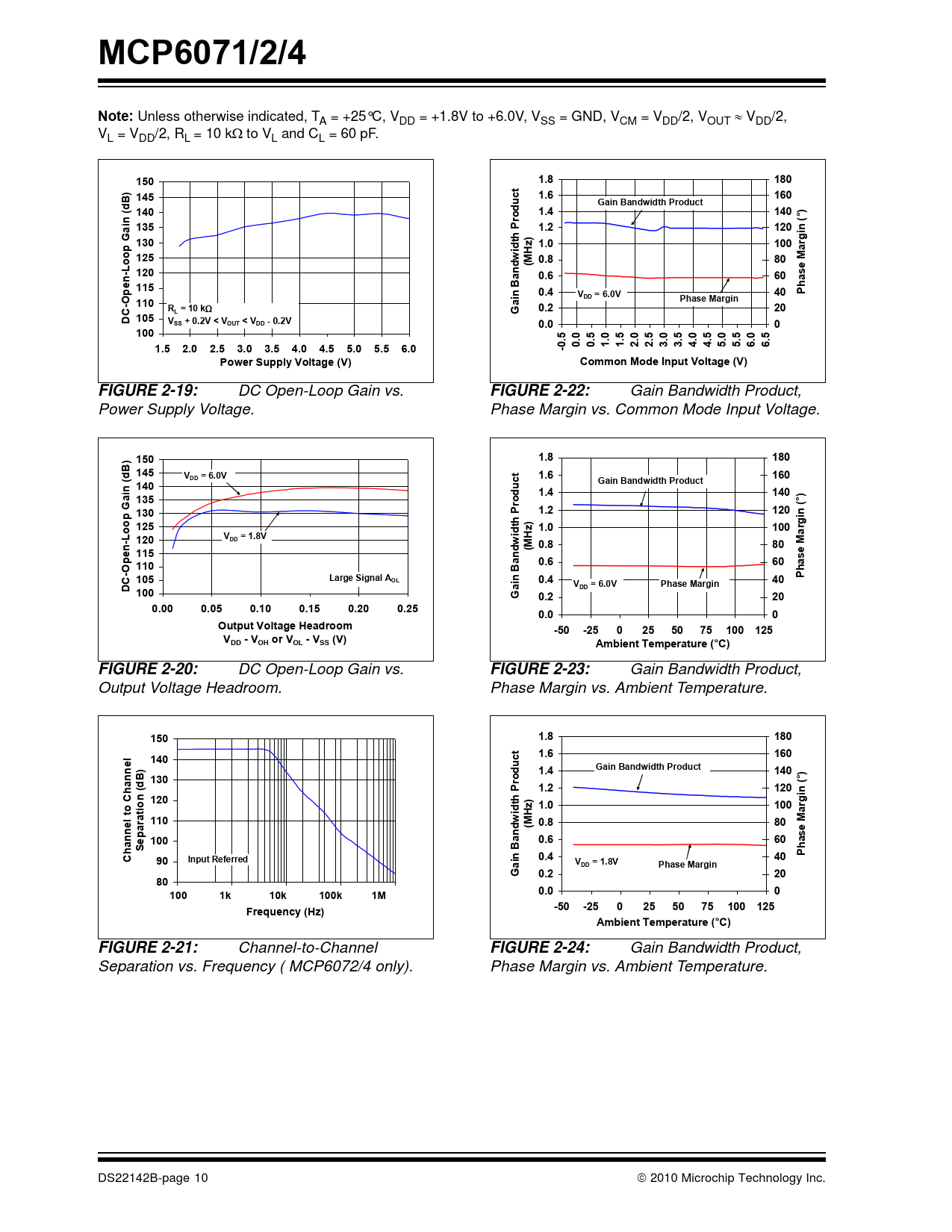

Unless otherwise indicated, T ≈ A = +25°C, VDD = +1.8V to +6.0V, VSS = GND, VCM = VDD/2, VOUT VDD/2, VL = VDD/2, RL = 10 kΩ to VL and CL = 60 pF.

150 1.8 180 ) t 145 B 1.6 160 Gain Bandwidth Product (d 140 duc 1.4 o 140 in (°) a 135 Pr 1.2 120 h in 130 dt z) 1.0 100 arg op G 125 o wi 0.8 (MH 80 e M 120 nd n-L a 0.6 60 as 115 pe B 0.4 in V 40 Ph DD = 6.0V -O 110 Phase Margin C R 0.2 20 L = 10 kΩ Ga D 105 VSS + 0.2V < VOUT < VDD - 0.2V 0.0 0 100 .5 0 5 0 5 0 5 0 5 0 5 0 5 0 5 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 -0 0. 0. 1. 1. 2. 2. 3. 3. 4. 4. 5. 5. 6. 6. Power Supply Voltage (V) Common Mode Input Voltage (V) FIGURE 2-19:

DC Open-Loop Gain vs.

FIGURE 2-22:

Gain Bandwidth Product, Power Supply Voltage. Phase Margin vs. Common Mode Input Voltage.

) 150 1.8 180 B 145 V t 1.6 160 (d DD = 6.0V 140 Gain Bandwidth Product in a duc 1.4 140 135 o G (°) 130 Pr 1.2 120 h in 125 oop z) 1.0 dt 100 rg a L 120 VDD = 1.8V wi n- (MH 0.8 80 115 nd pe se M 110 a 0.6 60 a -O B Ph C 105 Large Signal AOL 0.4 40 D ain VDD = 6.0V Phase Margin 100 G 0.2 20 0.00 0.05 0.10 0.15 0.20 0.25 0.0 0 Output Voltage Headroom -50 -25 0 25 50 75 100 125 VDD - VOH or VOL - VSS (V) Ambient Temperature (°C) FIGURE 2-20:

DC Open-Loop Gain vs.

FIGURE 2-23:

Gain Bandwidth Product, Output Voltage Headroom. Phase Margin vs. Ambient Temperature.

150 1.8 180 t l 140 1.6 160 e n ) duc 1.4 Gain Bandwidth Product 140 n B 130 a d ro (°) ( 1.2 120 in Ch n 120 h P o z) 1.0 100 tio idt arg l t ra 110 e w (MH 0.8 80 n e M n pa 100 as a and 0.6 60 Se B h P Ch 90 Input Referred n 0.4 40 VDD = 1.8V Phase Margin Gai 0.2 20 80 0.0 0 1.00E +0 100 2 1 .00E 1k + 03 1.00E 10 + k 0 4 1. 1 00E 00k +05 1.00 1M E+06 Frequency (Hz) -50 -25 0 25 50 75 100 125 Ambient Temperature (°C) FIGURE 2-21:

Channel-to-Channel

FIGURE 2-24:

Gain Bandwidth Product, Separation vs. Frequency ( MCP6072/4 only). Phase Margin vs. Ambient Temperature. DS22142B-page 10 © 2010 Microchip Technology Inc. Document Outline MCP6071/2/4 Features Applications Design Aids Typical Application Description Package Types Notes: 1.0 Electrical Characteristics 1.1 Absolute Maximum Ratings † 1.2 Specifications TABLE 1-1: DC electrical specifications TABLE 1-2: AC Electrical Specifications TABLE 1-3: temperature specifications Note 1: The internal junction temperature (TJ) must not exceed the absolute maximum specification of +150°C. 1.3 Test Circuits EQUATION 1-1: FIGURE 1-1: AC and DC Test Circuit for Most Specifications. Notes: 2.0 Typical Performance Curves FIGURE 2-1: Input Offset Voltage with VDD = 3.0V. FIGURE 2-2: Input Offset Voltage Drift with VDD = 3.0V and TA £ +85°C. FIGURE 2-3: Input Offset Voltage Drift with VDD = 3.0V and TA ³ +85°C. FIGURE 2-4: Input Offset Voltage vs. Common Mode Input Voltage with VDD = 6.0V. FIGURE 2-5: Input Offset Voltage vs. Common Mode Input Voltage with VDD = 3.0V. FIGURE 2-6: Input Offset Voltage vs. Common Mode Input Voltage with VDD = 1.8V. FIGURE 2-7: Input Offset Voltage vs. Output Voltage. FIGURE 2-8: Input Offset Voltage vs. Power Supply Voltage. FIGURE 2-9: Input Noise Voltage Density vs. Frequency. FIGURE 2-10: Input Noise Voltage Density vs. Common Mode Input Voltage. FIGURE 2-11: CMRR, PSRR vs. Frequency. FIGURE 2-12: CMRR, PSRR vs. Ambient Temperature. FIGURE 2-13: Common Mode Input Voltage Range Limit vs. Ambient Temperature. FIGURE 2-14: Input Bias, Offset Currents vs. Ambient Temperature. FIGURE 2-15: Input Bias Current vs. Common Mode Input Voltage. FIGURE 2-16: Quiescent Current vs Ambient Temperature with VCM = 0.9VDD. FIGURE 2-17: Quiescent Current vs. Power Supply Voltage with VCM = 0.9VDD. FIGURE 2-18: Open-Loop Gain, Phase vs. Frequency. FIGURE 2-19: DC Open-Loop Gain vs. Power Supply Voltage. FIGURE 2-20: DC Open-Loop Gain vs. Output Voltage Headroom. FIGURE 2-21: Channel-to-Channel Separation vs. Frequency ( MCP6072/4 only). FIGURE 2-22: Gain Bandwidth Product, Phase Margin vs. Common Mode Input Voltage. FIGURE 2-23: Gain Bandwidth Product, Phase Margin vs. Ambient Temperature. FIGURE 2-24: Gain Bandwidth Product, Phase Margin vs. Ambient Temperature. FIGURE 2-25: Ouput Short Circuit Current vs. Power Supply Voltage. FIGURE 2-26: Output Voltage Swing vs. Frequency. FIGURE 2-27: Ratio of Output Voltage Headroom to Output Current vs. Output Current. FIGURE 2-28: Output Voltage Headroom vs. Ambient Temperature. FIGURE 2-29: Slew Rate vs. Ambient Temperature. FIGURE 2-30: Small Signal Non-Inverting Pulse Response. FIGURE 2-31: Small Signal Inverting Pulse Response. FIGURE 2-32: Large Signal Non-Inverting Pulse Response. FIGURE 2-33: Large Signal Inverting Pulse Response. FIGURE 2-34: The MCP6071/2/4 Shows No Phase Reversal. FIGURE 2-35: Closed Loop Output Impedance vs. Frequency. FIGURE 2-36: Measured Input Current vs. Input Voltage (below VSS). 3.0 Pin Descriptions TABLE 3-1: Pin Function Table 3.1 Analog Outputs 3.2 Analog Inputs 3.3 Power Supply Pins 3.4 Exposed Thermal Pad (EP) Notes: 4.0 Application Information 4.1 Rail-to-Rail Input 4.1.1 Phase ReversaL 4.1.2 Input Voltage Limits FIGURE 4-1: Simplified Analog Input ESD Structures. FIGURE 4-2: Protecting the Analog Inputs. 4.1.3 Input Current Limits FIGURE 4-3: Protecting the Analog Inputs. 4.1.4 Normal Operation 4.2 Rail-to-Rail Output 4.3 Capacitive Loads FIGURE 4-4: Output Resistor, RISO Stabilizes Large Capacitive Loads. FIGURE 4-5: Recommended RISO Values for Capacitive Loads. 4.4 Supply Bypass 4.5 Unused Op Amps FIGURE 4-6: Unused Op Amps. 4.6 PCB Surface Leakage FIGURE 4-7: Example Guard Ring Layout for Inverting Gain. 1. Non-inverting Gain and Unity-Gain Buffer: a. Connect the non-inverting pin (VIN+) to the input with a wire that does not touch the PCB surface. b. Connect the guard ring to the inverting input pin (VIN–). This biases the guard ring to the common mode input voltage. 2. Inverting Gain and Transimpedance Gain Amplifiers (convert current to voltage, such as photo detectors): a. Connect the guard ring to the non-inverting input pin (VIN+). This biases the guard ring to the same reference voltage as the op amp (e.g., VDD/2 or ground). b. Connect the inverting pin (VIN–) to the input with a wire that does not touch the PCB surface. 4.7 Application Circuits 4.7.1 Gyrator FIGURE 4-8: Gyrator. 4.7.2 Instrumentation Amplifier FIGURE 4-9: Two Op Amp Instrumentation Amplifier. 4.7.3 Precision Comparator FIGURE 4-10: Precision, Non-inverting Comparator. 5.0 Design Aids 5.1 SPICE Macro Model 5.2 FilterLab® Software 5.3 MAPS (Microchip Advanced Part Selector) 5.4 Analog Demonstration and Evaluation Boards 5.5 Application Notes Notes: 6.0 Packaging Information 6.1 Package Marking Information 110 µA, High Precision Op Amps Appendix A: REVISION HISTORY Revision B (December 2010) 1. Added new SOT-23-5 package type for MCP6071 device. 2. Corrected Figures 2-13, 2-22, 2-23, 2-24, 2-28, 2-29 and 2-34 in Section 2.0 “Typical Performance Curves”. 3. Modified Table 3-1 to show the pin column for MCP6071, SOT-23-5 package. 4. Updated Section 4.1.2 “Input Voltage Limits”. 5. Added Section 4.1.3 “Input Current Limits”. 6. Added new document item in Section 5.5 “Application Notes”. 7. Updated the Product Identification System page. Revision A (March 2009) Notes: a) MCP6071T-E/OT: Tape and Reel, 5LD SOT-23 pkg b) MCP6071-E/SN: 8LD SOIC pkg c) MCP6071T-E/SN: Tape and Reel, 8LD SOIC pkg d) MCP6071T-E/MNY: Tape and Reel, 8LD 2x3 TDFN pkg a) MCP6072-E/SN: 8LD SOIC pkg b) MCP6072T-E/SN: Tape and Reel, 8LD SOIC pkg c) MCP6072T-E/MNY: Tape and Reel 8LD 2x3 TDFN pkg a) MCP6074-E/SL: 14LD SOIC pkg b) MCP6074T-E/SL: Tape and Reel, 14LD SOIC pkg c) MCP6074-E/ST: 14LD TSSOP pkg d) MCP6074T-E/ST: Tape and Reel, 14LD TSSOP pkg Notes: Worldwide Sales and Service Trademarks Worldwide Sales

Купить MCP6072T-E/MNY на РадиоЛоцман.Цены — от 24 до 216 ₽

Купить MCP6072T-E/MNY на РадиоЛоцман.Цены — от 24 до 216 ₽