| Производитель | Analog Devices |

| Описание | Quad, 12-Bit DAC Voltage Output with Readback |

| Страниц / Страница | 20 / 5 — Data Sheet. DAC8412/DAC8413. Parameter. Symbol. Conditions. Min. Typ. … |

| Версия | G |

| Формат / Размер файла | PDF / 484 Кб |

| Язык документа | английский |

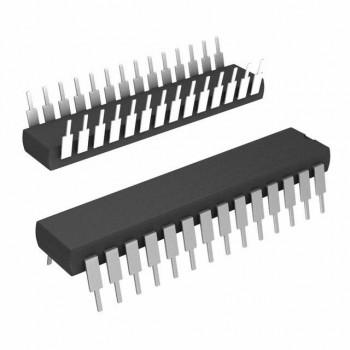

Купить DAC8412EPZ на РадиоЛоцман.Цены — от 279 до 21 257 ₽ Купить DAC8412EPZ на РадиоЛоцман.Цены — от 279 до 21 257 ₽23 предложений от 14 поставщиков ANALOG DEVICES DAC8412EPZ Digital to Analog Converter, Quad, 12Bit, 5V to ± 15V, DIP, 28Pins | |||

| DAC8412EPZ Analog Devices | от 279 ₽ | ||

| DAC8412EPZ Analog Devices | 3 866 ₽ | ||

| DAC8412EPZ Analog Devices | 13 945 ₽ | ||

| DAC8412EPZ Analog Devices | от 21 257 ₽ | ||