Datasheet AD7722 (Analog Devices) - 6

| Производитель | Analog Devices |

| Описание | 16-Bit, 195 kSPS CMOS, Sigma-Delta ADC |

| Страниц / Страница | 25 / 6 — AD7722. (AVDD = 5 V. 5%, DVDD = 5 V. 5%, AGND = DGND = 0 V, CL = 50 pF, … |

| Версия | C |

| Формат / Размер файла | PDF / 478 Кб |

| Язык документа | английский |

AD7722. (AVDD = 5 V. 5%, DVDD = 5 V. 5%, AGND = DGND = 0 V, CL = 50 pF, TA = TMIN to TMAX,

29 предложений от 16 поставщиков Single Channel Single ADC Delta-Sigma 195.3ksps 16-bit Parallel/Serial 44-Pin MQFP Tray |

| AD7722ASZ

Analog Devices | от 533 ₽ | |

| AD7722ASZ

Analog Devices | 1 864 ₽ | |

| AD7722ASZ

Analog Devices | 3 178 ₽ | |

| AD7722ASZ

Analog Devices | от 3 691 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

AD7722 (AVDD = 5 V

ⴞ

5%, DVDD = 5 V

ⴞ

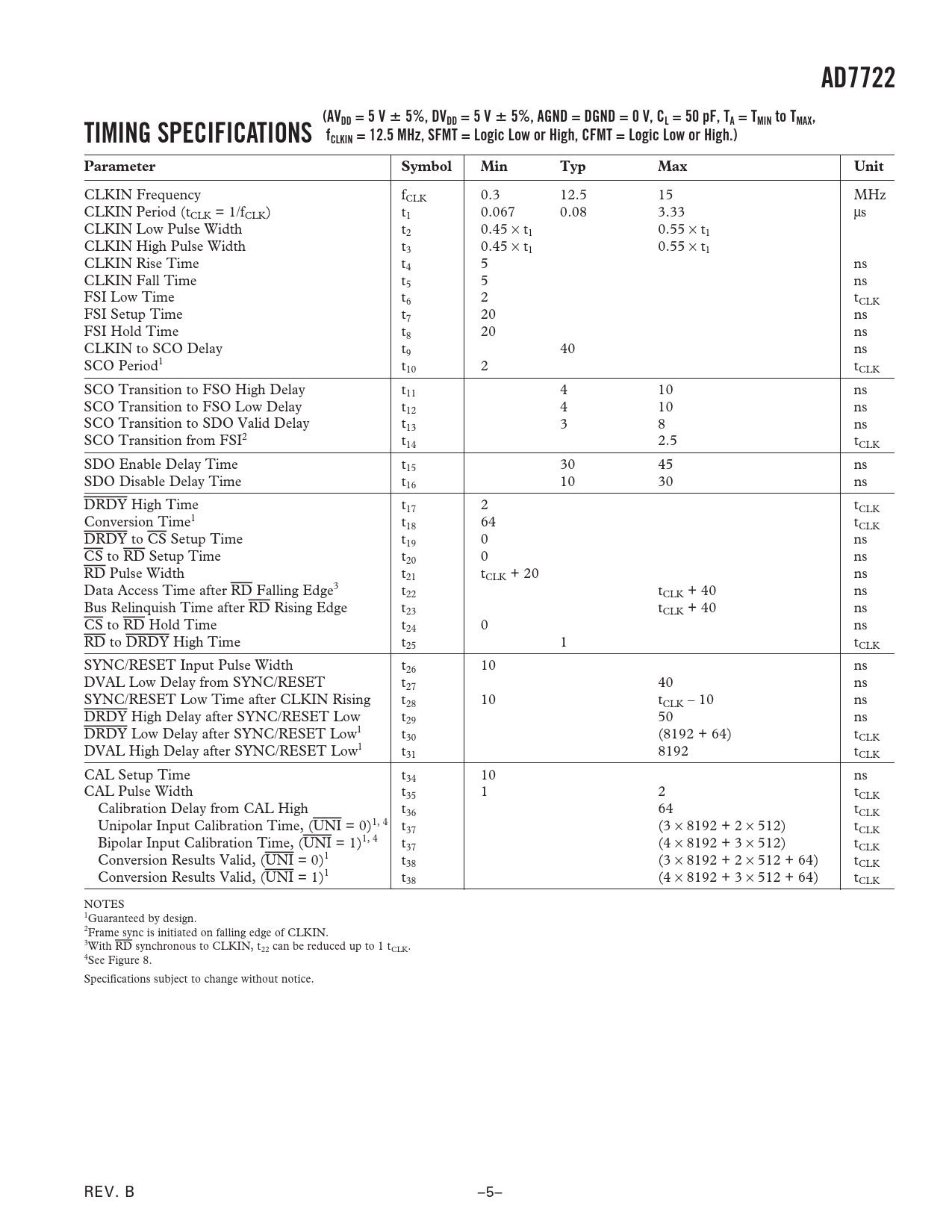

5%, AGND = DGND = 0 V, CL = 50 pF, TA = TMIN to TMAX, TIMING SPECIFICATIONS fCLKIN = 12.5 MHz, SFMT = Logic Low or High, CFMT = Logic Low or High.) Parameter Symbol Min Typ Max Unit

CLKIN Frequency fCLK 0.3 12.5 15 MHz CLKIN Period (tCLK = 1/fCLK) t1 0.067 0.08 3.33 µs CLKIN Low Pulse Width t2 0.45 × t1 0.55 × t1 CLKIN High Pulse Width t3 0.45 × t1 0.55 × t1 CLKIN Rise Time t4 5 ns CLKIN Fall Time t5 5 ns FSI Low Time t6 2 tCLK FSI Setup Time t7 20 ns FSI Hold Time t8 20 ns CLKIN to SCO Delay t9 40 ns SCO Period1 t10 2 tCLK SCO Transition to FSO High Delay t11 4 10 ns SCO Transition to FSO Low Delay t12 4 10 ns SCO Transition to SDO Valid Delay t13 3 8 ns SCO Transition from FSI2 t14 2.5 tCLK SDO Enable Delay Time t15 30 45 ns SDO Disable Delay Time t16 10 30 ns DRDY High Time t17 2 tCLK Conversion Time1 t18 64 tCLK DRDY to CS Setup Time t19 0 ns CS to RD Setup Time t20 0 ns RD Pulse Width t21 tCLK + 20 ns Data Access Time after RD Falling Edge3 t22 tCLK + 40 ns Bus Relinquish Time after RD Rising Edge t23 tCLK + 40 ns CS to RD Hold Time t24 0 ns RD to DRDY High Time t25 1 tCLK SYNC/RESET Input Pulse Width t26 10 ns DVAL Low Delay from SYNC/RESET t27 40 ns SYNC/RESET Low Time after CLKIN Rising t28 10 tCLK – 10 ns DRDY High Delay after SYNC/RESET Low t29 50 ns DRDY Low Delay after SYNC/RESET Low1 t30 (8192 + 64) tCLK DVAL High Delay after SYNC/RESET Low1 t31 8192 tCLK CAL Setup Time t34 10 ns CAL Pulse Width t35 1 2 tCLK Calibration Delay from CAL High t36 64 tCLK Unipolar Input Calibration Time, (UNI = 0)1, 4 t37 (3 × 8192 + 2 × 512) tCLK Bipolar Input Calibration Time, (UNI = 1)1, 4 t37 (4 × 8192 + 3 × 512) tCLK Conversion Results Valid, (UNI = 0)1 t38 (3 × 8192 + 2 × 512 + 64) tCLK Conversion Results Valid, (UNI = 1)1 t38 (4 × 8192 + 3 × 512 + 64) tCLK NOTES 1Guaranteed by design. 2Frame sync is initiated on falling edge of CLKIN. 3With RD synchronous to CLKIN, t22 can be reduced up to 1 tCLK. 4See Figure 8. Specifications subject to change without notice. REV. B –5– Document Outline FEATURES FUNCTIONAL BLOCK DIAGRAM GENERAL DESCRIPTION SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS ORDERING GUIDE TIMING SPECIFICATIONS PIN FUNCTION DESCRIPTIONS PIN CONFIGURATION PARALLEL MODE PIN FUNCTION DESCRIPTIONS SERIAL MODE PIN FUNCTION DESCRIPTIONS TERMINOLOGY Signal-to-Noise Plus Distortion Ratio (S/(N+D)) Total Harmonic Distortion (THD) Spurious-Free Dynamic Range (SFDR) Intermodulation Distortion Pass-Band Ripple Pass-Band Frequency Cutoff Frequency Stop-Band Frequency Stop-Band Attenuation Integral Nonlinearity Differential Nonlinearity Common-Mode Rejection Ratio Unipolar Offset Error Bipolar Offset Error Gain Error Typical Performance Characteristics CIRCUIT DESCRIPTION APPLYING THE AD7722 Analog Input Range Differential Inputs Applying the Reference Input Circuits Clock Generation Varying the Master Clock SYSTEM SYNCHRONIZATION AND CONTROL SYNC Input DVAL Reset Input Power-On Reset Offset and Gain Calibration DATA INTERFACING Parallel Interface SERIAL INTERFACE 2-Channel Multiplexed Operation Serial Interfacing to DSPs OUTLINE DIMENSIONS Revision History

Купить AD7722ASZ на РадиоЛоцман.Цены — от 533 до 237 119 ₽

Купить AD7722ASZ на РадиоЛоцман.Цены — от 533 до 237 119 ₽