Datasheet AD7124-4 (Analog Devices) - 92

| Производитель | Analog Devices |

| Описание | 4-Channel, Low Noise, Low Power, 24-Bit, Sigma-Delta ADC with PGA and Reference |

| Страниц / Страница | 92 / 92 — Data Sheet. AD7124-4. OUTLINE DIMENSIONS. 5.10. 0.30. 5.00 SQ. 0.25. PIN … |

| Версия | D |

| Формат / Размер файла | PDF / 1.6 Мб |

| Язык документа | английский |

Data Sheet. AD7124-4. OUTLINE DIMENSIONS. 5.10. 0.30. 5.00 SQ. 0.25. PIN 1. 4.90. 0.18. INDICATOR. 0.50. BSC. EXPOSED. *3.75. PAD. 3.60 SQ 3.55. 0.25 MIN

Модельный ряд для этого даташита

Текстовая версия документа

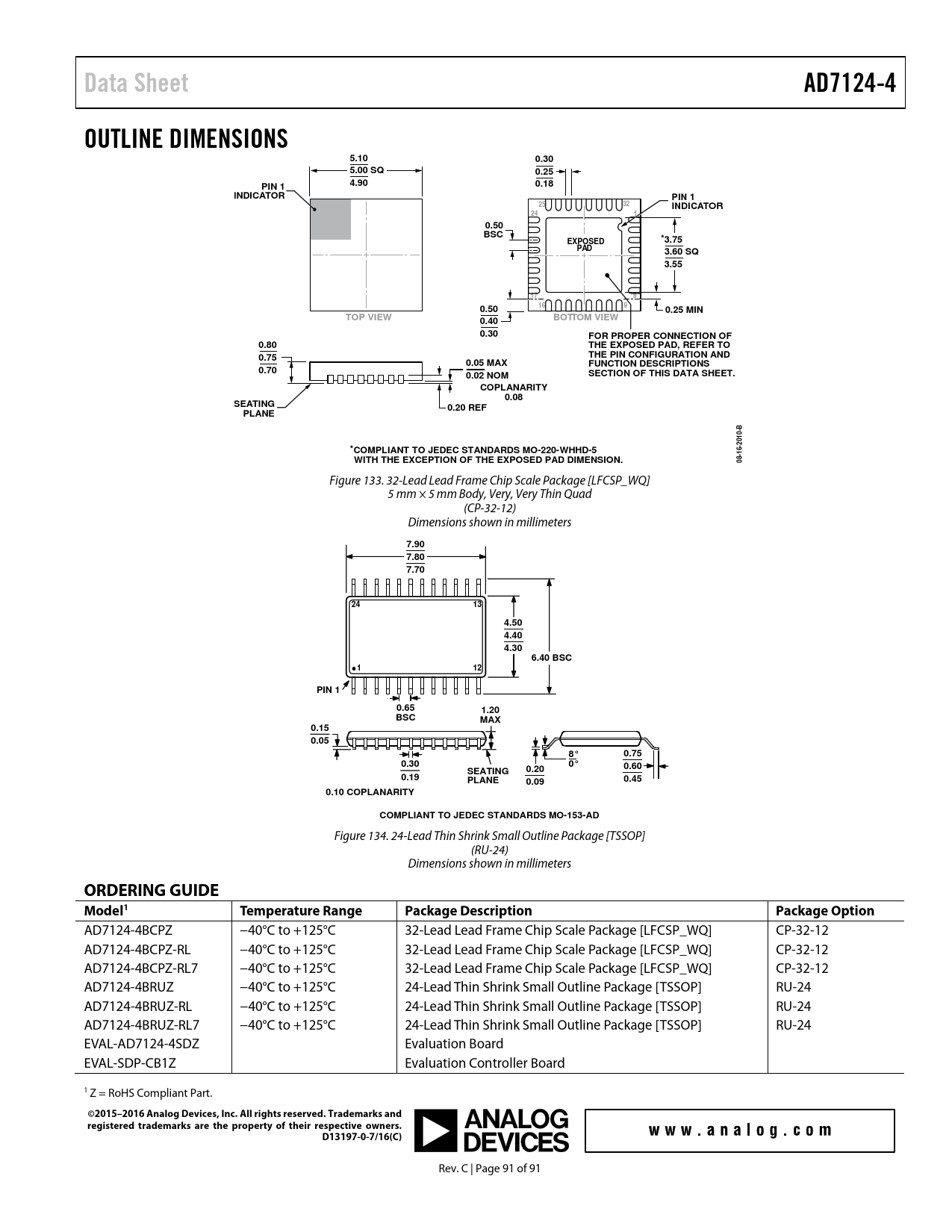

Data Sheet AD7124-4 OUTLINE DIMENSIONS 5.10 0.30 5.00 SQ 0.25 PIN 1 4.90 0.18 INDICATOR PIN 1 25 32 INDICATOR 24 1 0.50 BSC EXPOSED *3.75 PAD 3.60 SQ 3.55 17 8 16 9 0.50 0.25 MIN TOP VIEW BOTTOM VIEW 0.40 0.30 FOR PROPER CONNECTION OF 0.80 THE EXPOSED PAD, REFER TO 0.75 THE PIN CONFIGURATION AND 0.05 MAX FUNCTION DESCRIPTIONS 0.70 0.02 NOM SECTION OF THIS DATA SHEET. COPLANARITY 0.08 SEATING 0.20 REF PLANE B 2010- *COMPLIANT TO JEDEC STANDARDS MO-220-WHHD-5 16- WITH THE EXCEPTION OF THE EXPOSED PAD DIMENSION. 08-

Figure 133. 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] 5 mm × 5 mm Body, Very, Very Thin Quad (CP-32-12) Dimensions shown in millimeters

7.90 7.80 7.70 24 13 4.50 4.40 4.30 6.40 BSC 1 12 PIN 1 0.65 1.20 BSC MAX 0.15 0.05 8° 0.75 0.30 0° 0.20 0.60 SEATING 0.19 PLANE 0.09 0.45 0.10 COPLANARITY COMPLIANT TO JEDEC STANDARDS MO-153-AD

Figure 134. 24-Lead Thin Shrink Small Outline Package [TSSOP] (RU-24) Dimensions shown in millimeters

ORDERING GUIDE Model1 Temperature Range Package Description Package Option

AD7124-4BCPZ −40°C to +125°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-12 AD7124-4BCPZ-RL −40°C to +125°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-12 AD7124-4BCPZ-RL7 −40°C to +125°C 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-32-12 AD7124-4BRUZ −40°C to +125°C 24-Lead Thin Shrink Small Outline Package [TSSOP] RU-24 AD7124-4BRUZ-RL −40°C to +125°C 24-Lead Thin Shrink Small Outline Package [TSSOP] RU-24 AD7124-4BRUZ-RL7 −40°C to +125°C 24-Lead Thin Shrink Small Outline Package [TSSOP] RU-24 EVAL-AD7124-4SDZ Evaluation Board EVAL-SDP-CB1Z Evaluation Controller Board 1 Z = RoHS Compliant Part.

©2015–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D13197-0-7/16(C)

Rev. C | Page 91 of 91 Document Outline FEATURES APPLICATIONS FUNCTIONAL BLOCK DIAGRAM TABLE OF CONTENTS REVISION HISTORY GENERAL DESCRIPTION SPECIFICATIONS TIMING CHARACTERISTICS Timing Diagrams ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS TERMINOLOGY RMS NOISE AND RESOLUTION FULL POWER MODE Sinc4 Sinc3 Post Filters Fast Settling Filter (Sinc4 + Sinc1) Fast Settling Filter (Sinc3 + Sinc1) MID POWER MODE Sinc4 Sinc3 Post Filters Fast Settling Filter (Sinc4 + Sinc1) Fast Settling Filter (Sinc3 + Sinc1) LOW POWER MODE Sinc4 Sinc3 Post Filters Fast Settling Filter (Sinc4 + Sinc1) Fast Settling Filter (Sinc3 + Sinc1) GETTING STARTED OVERVIEW Power Modes Analog Inputs Multiplexer Reference Programmable Gain Array (PGA) Burnout Currents Σ-Δ ADC and Filter Channel Sequencer Per Channel Configuration Serial Interface Clock Temperature Sensor Digital Outputs Calibration Excitation Currents Bias Voltage Bridge Power Switch (PSW) Diagnostics POWER SUPPLIES Single Supply Operation (AVSS = DGND) Split Supply Operation (AVSS ≠ DGND) DIGITAL COMMUNICATION Accessing the ADC Register Map CONFIGURATION OVERVIEW Channel Configuration Channel Registers ADC Setups Configuration Registers Filter Registers Offset Registers Gain Registers Diagnostics ADC Control Register Understanding Configuration Flexibility ADC CIRCUIT INFORMATION ANALOG INPUT CHANNEL EXTERNAL IMPEDANCE WHEN USING A GAIN OF 1 PROGRAMMABLE GAIN ARRAY (PGA) REFERENCE BIPOLAR/UNIPOLAR CONFIGURATION DATA OUTPUT CODING EXCITATION CURRENTS BRIDGE POWER-DOWN SWITCH LOGIC OUTPUTS BIAS VOLTAGE GENERATOR CLOCK POWER MODES STANDBY AND POWER-DOWN MODES DIGITAL INTERFACE Single Conversion Mode Continuous Conversion Mode Continuous Read Mode DATA_STATUS SERIAL INTERFACE RESET (DOUT__DEL AND _EN BITS) RESET CALIBRATION SPAN AND OFFSET LIMITS SYSTEM SYNCHRONIZATION DIGITAL FILTER SINC4 FILTER Sinc4 Output Data Rate/Settling Time Sinc4 Zero Latency Sequencer Sinc4 50 Hz and 60 Hz Rejection SINC3 FILTER Sinc3 Output Data Rate and Settling Time Sinc3 Zero Latency Sequencer Sinc3 50 Hz and 60 Hz Rejection FAST SETTLING MODE (SINC4 + SINC1 FILTER) Output Data Rate and Settling Time, Sinc4 + Sinc1 Filter Sequencer 50 Hz and 60 Hz Rejection, Sinc4 + Sinc1 Filter FAST SETTLING MODE (SINC3 + SINC1 FILTER) Output Data Rate and Settling Time, Sinc3 + Sinc1 Filter Sequencer 50 Hz and 60 Hz Rejection, Sinc3 + Sinc1 Filter POST FILTERS SUMMARY OF FILTER OPTIONS DIAGNOSTICS SIGNAL CHAIN CHECK REFERENCE DETECT CALIBRATION, CONVERSION, AND SATURATION ERRORS OVERVOLTAGE/UNDERVOLTAGE DETECTION POWER SUPPLY MONITORS LDO MONITORING Power Supply Monitor LDO Capacitor Detect MCLK COUNTER SPI SCLK COUNTER SPI READ/WRITE ERRORS SPI_IGNORE ERROR CHECKSUM PROTECTION MEMORY MAP CHECKSUM PROTECTION ROM CHECKSUM PROTECTION CRC Calculation Example of a Polynomial CRC Calculation—24-Bit Word: 0x654321 (8-Bit Command and 16-Bit Data) BURNOUT CURRENTS TEMPERATURE SENSOR GROUNDING AND LAYOUT APPLICATIONS INFORMATION TEMPERATURE MEASUREMENT USING A THERMOCOUPLE TEMPERATURE MEASUREMENT USING AN RTD FLOWMETER ON-CHIP REGISTERS COMMUNICATIONS REGISTER STATUS REGISTER ADC_CONTROL REGISTER DATA REGISTER IO_CONTROL_1 REGISTER IO_CONTROL_2 REGISTER ID REGISTER ERROR REGISTER ERROR_EN REGISTER MCLK_COUNT REGISTER CHANNEL REGISTERS CONFIGURATION REGISTERS FILTER REGISTERS OFFSET REGISTERS GAIN REGISTERS OUTLINE DIMENSIONS ORDERING GUIDE

Купить AD7124-4TRUZ-EP на РадиоЛоцман.Цены — от 1 317 до 185 974 ₽

Купить AD7124-4TRUZ-EP на РадиоЛоцман.Цены — от 1 317 до 185 974 ₽