Datasheet AD7761 (Analog Devices) - 10

| Производитель | Analog Devices |

| Описание | 8-Channel, 16-Bit, Simultaneous Sampling ADC with Power Scaling, 110.8 kHz BW |

| Страниц / Страница | 76 / 10 — Data Sheet. AD7761. Parameter. Test Conditions/Comments. Min. Typ. Max. … |

| Версия | A |

| Формат / Размер файла | PDF / 1.5 Мб |

| Язык документа | английский |

Data Sheet. AD7761. Parameter. Test Conditions/Comments. Min. Typ. Max. Unit

IC ADC 16BIT SIGMA-DELTA 64LQFP |

| AD7761BSTZ-RL7

Analog Devices | 4 724 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

link to page 11 link to page 11 link to page 11 link to page 11

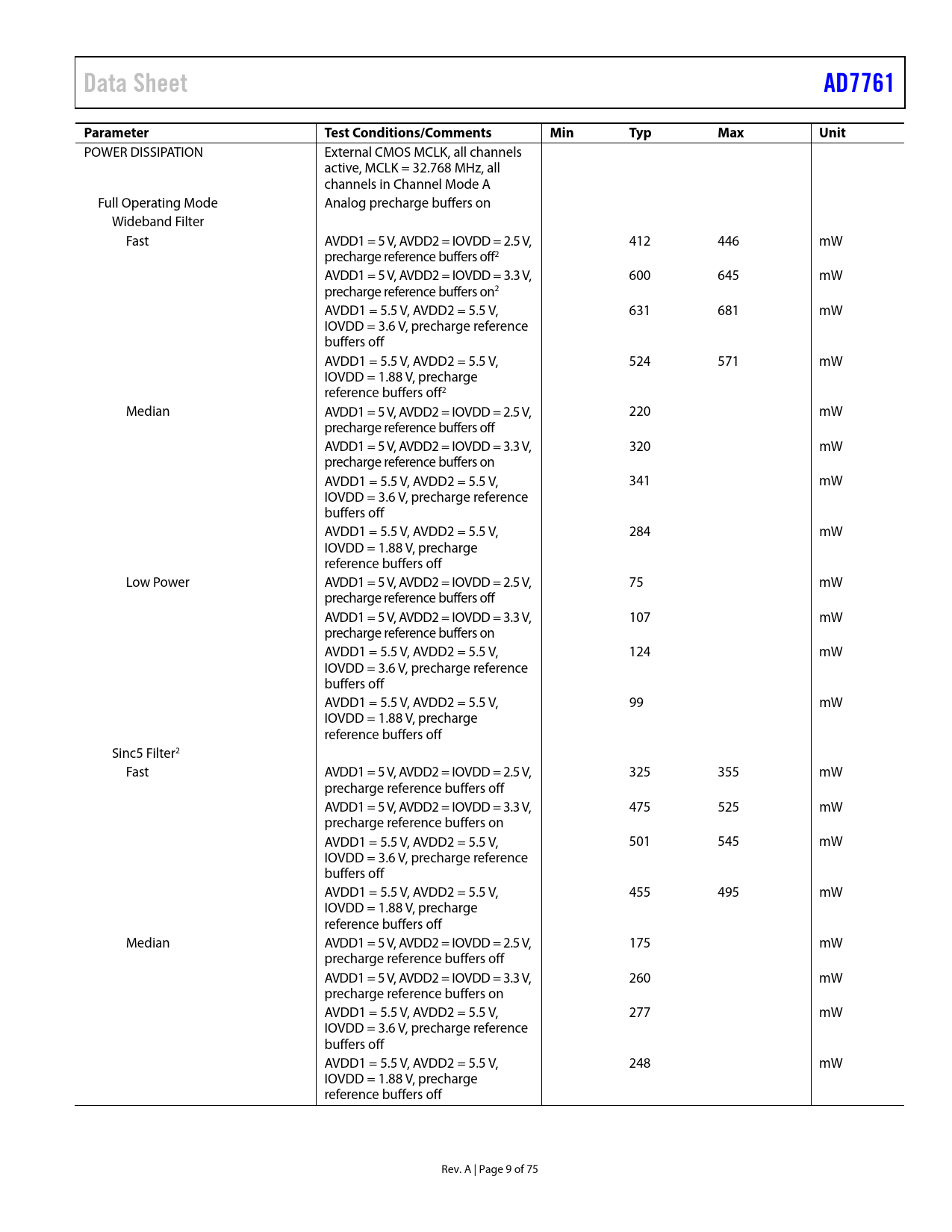

Data Sheet AD7761 Parameter Test Conditions/Comments Min Typ Max Unit

POWER DISSIPATION External CMOS MCLK, all channels active, MCLK = 32.768 MHz, all channels in Channel Mode A Full Operating Mode Analog precharge buffers on Wideband Filter Fast AVDD1 = 5 V, AVDD2 = IOVDD = 2.5 V, 412 446 mW precharge reference buffers off2 AVDD1 = 5 V, AVDD2 = IOVDD = 3.3 V, 600 645 mW precharge reference buffers on2 AVDD1 = 5.5 V, AVDD2 = 5.5 V, 631 681 mW IOVDD = 3.6 V, precharge reference buffers off AVDD1 = 5.5 V, AVDD2 = 5.5 V, 524 571 mW IOVDD = 1.88 V, precharge reference buffers off2 Median AVDD1 = 5 V, AVDD2 = IOVDD = 2.5 V, 220 mW precharge reference buffers off AVDD1 = 5 V, AVDD2 = IOVDD = 3.3 V, 320 mW precharge reference buffers on AVDD1 = 5.5 V, AVDD2 = 5.5 V, 341 mW IOVDD = 3.6 V, precharge reference buffers off AVDD1 = 5.5 V, AVDD2 = 5.5 V, 284 mW IOVDD = 1.88 V, precharge reference buffers off Low Power AVDD1 = 5 V, AVDD2 = IOVDD = 2.5 V, 75 mW precharge reference buffers off AVDD1 = 5 V, AVDD2 = IOVDD = 3.3 V, 107 mW precharge reference buffers on AVDD1 = 5.5 V, AVDD2 = 5.5 V, 124 mW IOVDD = 3.6 V, precharge reference buffers off AVDD1 = 5.5 V, AVDD2 = 5.5 V, 99 mW IOVDD = 1.88 V, precharge reference buffers off Sinc5 Filter2 Fast AVDD1 = 5 V, AVDD2 = IOVDD = 2.5 V, 325 355 mW precharge reference buffers off AVDD1 = 5 V, AVDD2 = IOVDD = 3.3 V, 475 525 mW precharge reference buffers on AVDD1 = 5.5 V, AVDD2 = 5.5 V, 501 545 mW IOVDD = 3.6 V, precharge reference buffers off AVDD1 = 5.5 V, AVDD2 = 5.5 V, 455 495 mW IOVDD = 1.88 V, precharge reference buffers off Median AVDD1 = 5 V, AVDD2 = IOVDD = 2.5 V, 175 mW precharge reference buffers off AVDD1 = 5 V, AVDD2 = IOVDD = 3.3 V, 260 mW precharge reference buffers on AVDD1 = 5.5 V, AVDD2 = 5.5 V, 277 mW IOVDD = 3.6 V, precharge reference buffers off AVDD1 = 5.5 V, AVDD2 = 5.5 V, 248 mW IOVDD = 1.88 V, precharge reference buffers off Rev. A | Page 9 of 75 Document Outline FEATURES APPLICATIONS FUNCTIONAL BLOCK DIAGRAM TABLE OF CONTENTS REVISION HISTORY GENERAL DESCRIPTION SPECIFICATIONS TIMING SPECIFICATIONS 1.8 V IOVDD TIMING SPECIFICATIONS Timing Diagrams ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS TERMINOLOGY THEORY OF OPERATION CLOCKING, SAMPLING TREE, AND POWER SCALING Example of Power vs. Noise Performance Optimization Configuration A Configuration B Clocking Out the ADC Conversion Results (DCLK) NOISE PERFORMANCE AND RESOLUTION APPLICATIONS INFORMATION POWER SUPPLIES Recommended Power Supply Configuration 1.8 V IOVDD Operation Analog Supply Internal Connectivity DEVICE CONFIGURATION Interface Data Format PIN CONTROL MODE Setting the Filter Setting the Decimation Rate Operating Mode Diagnostics Configuration Example Channel Standby SPI CONTROL Accessing the ADC Register Map SPI Interface Details SPI Control Interface Error Handling SPI Reset Configuration SPI CONTROL FUNCTIONALITY Channel Configuration Channel Modes Reset over SPI Control Interface Sleep Mode Channel Standby Mode Clocking Selections MCLK Source Selection Interface Configuration CRC Protection ADC Synchronization over SPI Analog Input Precharge Buffers Reference Precharge Buffers Per Channel Calibration Gain, Offset, and Sync Phase GPIOs SPI CONTROL MODE EXTRA DIAGNOSTIC FEATURES RAM Built In Self Test Revision Identification Number Diagnostic Meter Mode CIRCUIT INFORMATION CORE SIGNAL CHAIN ADC Power Modes ANALOG INPUTS VCM REFERENCE INPUT CLOCK SELECTION DIGITAL FILTERING Sinc5 Filter Wideband Low Ripple Filter Filter Settling Time DECIMATION RATE CONTROL ANTIALIASING Modulator Sampling Frequency Modulator Chopping Frequency Modulator Saturation Point CALIBRATION Offset Adjustment Gain Adjustment Sync Phase Offset Adjustment DATA INTERFACE SETTING THE FORMAT OF DATA OUTPUT ADC CONVERSION OUTPUT: HEADER AND DATA ERROR_FLAGGED Filter Not Settled Repeated Data Filter Type Filter Saturated Channel ID Data Interface: Standard Conversion Operation Data Interface: One-Shot Conversion Operation Daisy-Chaining Synchronization CRC Check on Data Interface CRC Code Example FUNCTIONALITY GPIO FUNCTIONALITY REGISTER MAP DETAILS (SPI CONTROL) REGISTER MAP CHANNEL STANDBY REGISTER CHANNEL MODE A REGISTER CHANNEL MODE B REGISTER CHANNEL MODE SELECT REGISTER POWER MODE SELECT REGISTER GENERAL DEVICE CONFIGURATION REGISTER DATA CONTROL: SOFT RESET, SYNC, AND SINGLE-SHOT CONTROL REGISTER INTERFACE CONFIGURATION REGISTER DIGITAL FILTER RAM BUILT IN SELF TEST (BIST) REGISTER STATUS REGISTER REVISION IDENTIFICATION REGISTER GPIO CONTROL REGISTER GPIO WRITE DATA REGISTER GPIO READ DATA REGISTER ANALOG INPUT PRECHARGE BUFFER ENABLE REGISTER CHANNEL 0 TO CHANNEL 3 ANALOG INPUT PRECHARGE BUFFER ENABLE REGISTER CHANNEL 4 TO CHANNEL 7 POSITIVE REFERENCE PRECHARGE BUFFER ENABLE REGISTER NEGATIVE REFERENCE PRECHARGE BUFFER ENABLE REGISTER OFFSET REGISTERS GAIN REGISTERS SYNC PHASE OFFSET REGISTERS ADC DIAGNOSTIC RECEIVE SELECT REGISTER ADC DIAGNOSTIC CONTROL REGISTER MODULATOR DELAY CONTROL REGISTER CHOPPING CONTROL REGISTER OUTLINE DIMENSIONS ORDERING GUIDE