Datasheet AD7779 (Analog Devices) - 9

| Производитель | Analog Devices |

| Описание | 8-Channel, 24-Bit, Simultaneous Sampling ADC |

| Страниц / Страница | 101 / 9 — AD7779. Data Sheet. Parameter. Test Conditions/Comments. Min. Typ. Max. … |

| Версия | C |

| Формат / Размер файла | PDF / 1.8 Мб |

| Язык документа | английский |

AD7779. Data Sheet. Parameter. Test Conditions/Comments. Min. Typ. Max. Unit

31 предложений от 13 поставщиков Микросхема Преобразователь AD, Octal Channel Octal ADC Delta-Sigma 16KSPS 24Bit Serial 64Pin LFCSP EP T/R |

| AD7779ACPZ-RL

Analog Devices | от 122 ₽ | |

| AD7779ACPZ

Analog Devices | 821 ₽ | |

| AD7779ACPZ-RL

Analog Devices | 1 431 ₽ | |

| AD7779ACPZ-RL

Analog Devices | от 2 013 ₽ | |

Модельный ряд для этого даташита

Текстовая версия документа

link to page 10

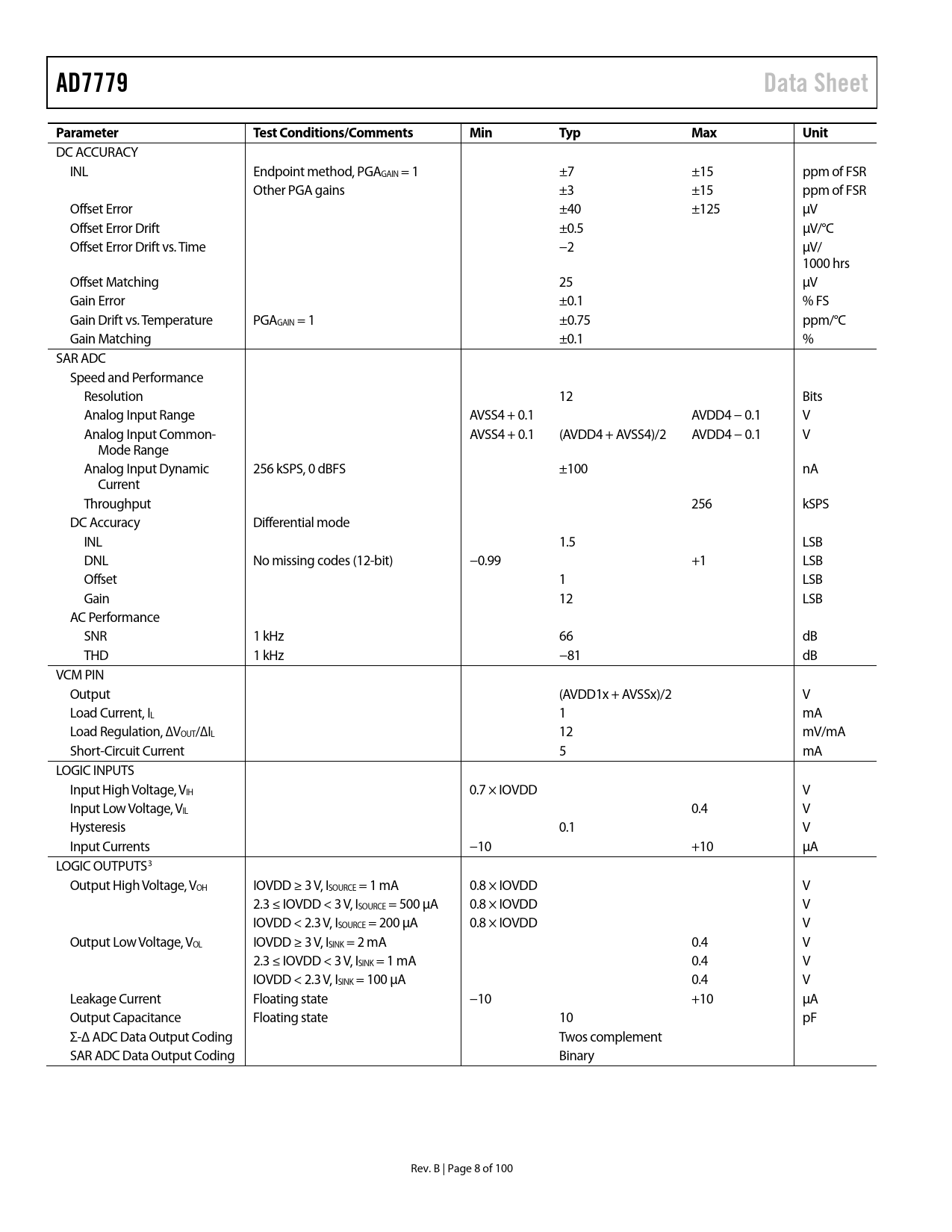

AD7779 Data Sheet Parameter Test Conditions/Comments Min Typ Max Unit

DC ACCURACY INL Endpoint method, PGAGAIN = 1 ±7 ±15 ppm of FSR Other PGA gains ±3 ±15 ppm of FSR Offset Error ±40 ±125 µV Offset Error Drift ±0.5 µV/°C Offset Error Drift vs. Time −2 µV/ 1000 hrs Offset Matching 25 µV Gain Error ±0.1 % FS Gain Drift vs. Temperature PGAGAIN = 1 ±0.75 ppm/°C Gain Matching ±0.1 % SAR ADC Speed and Performance Resolution 12 Bits Analog Input Range AVSS4 + 0.1 AVDD4 − 0.1 V Analog Input Common- AVSS4 + 0.1 (AVDD4 + AVSS4)/2 AVDD4 − 0.1 V Mode Range Analog Input Dynamic 256 kSPS, 0 dBFS ±100 nA Current Throughput 256 kSPS DC Accuracy Differential mode INL 1.5 LSB DNL No missing codes (12-bit) −0.99 +1 LSB Offset 1 LSB Gain 12 LSB AC Performance SNR 1 kHz 66 dB THD 1 kHz −81 dB VCM PIN Output (AVDD1x + AVSSx)/2 V Load Current, IL 1 mA Load Regulation, ∆VOUT/∆IL 12 mV/mA Short-Circuit Current 5 mA LOGIC INPUTS Input High Voltage, VIH 0.7 × IOVDD V Input Low Voltage, VIL 0.4 V Hysteresis 0.1 V Input Currents −10 +10 µA LOGIC OUTPUTS3 Output High Voltage, VOH IOVDD ≥ 3 V, ISOURCE = 1 mA 0.8 × IOVDD V 2.3 ≤ IOVDD < 3 V, ISOURCE = 500 µA 0.8 × IOVDD V IOVDD < 2.3 V, ISOURCE = 200 µA 0.8 × IOVDD V Output Low Voltage, VOL IOVDD ≥ 3 V, ISINK = 2 mA 0.4 V 2.3 ≤ IOVDD < 3 V, ISINK = 1 mA 0.4 V IOVDD < 2.3 V, ISINK = 100 µA 0.4 V Leakage Current Floating state −10 +10 µA Output Capacitance Floating state 10 pF Σ-Δ ADC Data Output Coding Twos complement SAR ADC Data Output Coding Binary Rev. B | Page 8 of 100 Document Outline FEATURES APPLICATIONS GENERAL DESCRIPTION REVISION HISTORY FUNCTIONAL BLOCK DIAGRAM SPECIFICATIONS DOUTx TIMING CHARACTERISTISTICS SPI TIMING CHARACTERISTISTICS SYNCHRONIZATION PINS AND RESET TIMING CHARACTERISTICS SAR ADC TIMING CHARACTERISTISTICS GPIO SRC UPDATE TIMING CHARACTERISTISTICS ABSOLUTE MAXIMUM RATINGS THERMAL RESISTANCE ESD CAUTION PIN CONFIGURATION AND FUNCTION DESCRIPTIONS TYPICAL PERFORMANCE CHARACTERISTICS TERMINOLOGY RMS NOISE AND RESOLUTION HIGH RESOLUTION MODE LOW POWER MODE THEORY OF OPERATION ANALOG INPUTS TRANSFER FUNCTION CORE SIGNAL CHAIN CAPACITIVE PGA INTERNAL REFERENCE AND REFERENCE BUFFERS INTEGRATED LDOs CLOCKING AND SAMPLING DIGITAL RESET AND SYNCHRONIZATION PINS DIGITAL FILTERING SHUTDOWN MODE CONTROLLING THE AD7779 PIN CONTROL MODE SPI CONTROL Functionality Available in SPI Mode Offset and Gain Correction SPI Control Functionality Global Control Functions Per Channel Functions Phase Adjustment PGA Gain Decimation GPIO Pins Σ-∆ Reference Configuration Power Modes LDO Bypassing DIGITAL SPI INTERFACE SPI CRC—Checksum Protection (SPI Control Mode) SPI Read/Write Register Mode (SPI Control Mode) SPI SAR Diagnostic Mode (SPI Control Mode) Σ-∆ Data, ADC Mode SPI Software Reset DIAGNOSTICS AND MONITORING SELF DIAGNOSTICS ERROR General Errors MCLK Switch Error (SPI Control Mode) Reset Detection Internal LDO Status ROM and MEMMAP CRC Σ-∆ ADC Errors Reference Detect (SPI Control Mode) Overvoltage and Undervoltage Events Modulator Saturation Filter Saturation Output Saturation SPI Transmission Errors (SPI Control Mode) CRC Checksum Error SCLK Counter Invalid Read Invalid Write MONITORING USING THE AD7779 SAR ADC(SPI CONTROL MODE) Temperature Sensor Σ-Δ ADC DIAGNOSTICS (SPI CONTROL MODE) Σ-∆ OUTPUT DATA ADC CONVERSION OUTPUT—HEADER AND DATA CRC Header ERROR Header (SPI Control Mode) SAMPLE RATE CONVERTER (SRC) (SPI CONTROL MODE) SRC Bandwidth SRC Group Delay and Latency Settling Time DATA OUTPUT INTERFACE DOUT3 to DOUT0 Data Interface Standalone Mode Daisy-Chain Mode Minimum DCLKx Frequency SPI Interface CALCULATING THE CRC CHECKSUM Σ-∆ CRC Checksum SPI Control Mode Checksum REGISTER SUMMARY REGISTER DETAILS CHANNEL 0 CONFIGURATION REGISTER CHANNEL 1 CONFIGURATION REGISTER CHANNEL 2 CONFIGURATION REGISTER CHANNEL 3 CONFIGURATION REGISTER CHANNEL 4 CONFIGURATION REGISTER CHANNEL 5 CONFIGURATION REGISTER CHANNEL 6 CONFIGURATION REGISTER CHANNEL 7 CONFIGURATION REGISTER DISABLE CLOCKS TO ADC CHANNEL REGISTER CHANNEL 0 SYNC OFFSET REGISTER CHANNEL 1 SYNC OFFSET REGISTER CHANNEL 2 SYNC OFFSET REGISTER CHANNEL 3 SYNC OFFSET REGISTER CHANNEL 4 SYNC OFFSET REGISTER CHANNEL 5 SYNC OFFSET REGISTER CHANNEL 6 SYNC OFFSET REGISTER CHANNEL 7 SYNC OFFSET REGISTER GENERAL USER CONFIGURATION 1 REGISTER GENERAL USER CONFIGURATION 2 REGISTER GENERAL USER CONFIGURATION 3 REGISTER DATA OUTPUT FORMAT REGISTER MAIN ADC METER AND REFERENCE MUX CONTROL REGISTER GLOBAL DIAGNOSTICS MUX REGISTER GPIO CONFIGURATION REGISTER GPIO DATA REGISTER BUFFER CONFIGURATION 1 REGISTER BUFFER CONFIGURATION 2 REGISTER CHANNEL 0 OFFSET UPPER BYTE REGISTER CHANNEL 0 OFFSET MIDDLE BYTE REGISTER CHANNEL 0 OFFSET LOWER BYTE REGISTER CHANNEL 0 GAIN UPPER BYTE REGISTER CHANNEL 0 GAIN MIDDLE BYTE REGISTER CHANNEL 0 GAIN LOWER BYTE REGISTER CHANNEL 1 OFFSET UPPER BYTE REGISTER CHANNEL 1 OFFSET MIDDLE BYTE REGISTER CHANNEL 1 OFFSET LOWER BYTE REGISTER CHANNEL 1 GAIN UPPER BYTE REGISTER CHANNEL 1 GAIN MIDDLE BYTE REGISTER CHANNEL 1 GAIN LOWER BYTE REGISTER CHANNEL 2 OFFSET UPPER BYTE REGISTER CHANNEL 2 OFFSET MIDDLE BYTE REGISTER CHANNEL 2 OFFSET LOWER BYTE REGISTER CHANNEL 2 GAIN UPPER BYTE REGISTER CHANNEL 2 GAIN MIDDLE BYTE REGISTER CHANNEL 2 GAIN LOWER BYTE REGISTER CHANNEL 3 OFFSET UPPER BYTE REGISTER CHANNEL 3 OFFSET MIDDLE BYTE REGISTER CHANNEL 3 OFFSET LOWER BYTE REGISTER CHANNEL 3 GAIN UPPER BYTE REGISTER CHANNEL 3 GAIN MIDDLE BYTE REGISTER CHANNEL 3 GAIN LOWER BYTE REGISTER CHANNEL 4 OFFSET UPPER BYTE REGISTER CHANNEL 4 OFFSET MIDDLE BYTE REGISTER CHANNEL 4 OFFSET LOWER BYTE REGISTER CHANNEL 4 GAIN UPPER BYTE REGISTER CHANNEL 4 GAIN MIDDLE BYTE REGISTER CHANNEL 4 GAIN LOWER BYTE REGISTER CHANNEL 5 OFFSET UPPER BYTE REGISTER CHANNEL 5 OFFSET MIDDLE BYTE REGISTER CHANNEL 5 OFFSET LOWER BYTE REGISTER CHANNEL 5 GAIN UPPER BYTE REGISTER CHANNEL 5 GAIN MIDDLE BYTE REGISTER CHANNEL 5 GAIN LOWER BYTE REGISTER CHANNEL 6 OFFSET UPPER BYTE REGISTER CHANNEL 6 OFFSET MIDDLE BYTE REGISTER CHANNEL 6 OFFSET LOWER BYTE REGISTER CHANNEL 6 GAIN UPPER BYTE REGISTER CHANNEL 6 GAIN MIDDLE BYTE REGISTER CHANNEL 6 GAIN LOWER BYTE REGISTER CHANNEL 7 OFFSET UPPER BYTE REGISTER CHANNEL 7 OFFSET MIDDLE BYTE REGISTER CHANNEL 7 OFFSET LOWER BYTE REGISTER CHANNEL 7 GAIN UPPER BYTE REGISTER CHANNEL 7 GAIN MIDDLE BYTE REGISTER CHANNEL 7 GAIN LOWER BYTE REGISTER CHANNEL 0 STATUS REGISTER CHANNEL 1 STATUS REGISTER CHANNEL 2 STATUS REGISTER CHANNEL 3 STATUS REGISTER CHANNEL 4 STATUS REGISTER CHANNEL 5 STATUS REGISTER CHANNEL 6 STATUS REGISTER CHANNEL 7 STATUS REGISTER CHANNEL 0/CHANNEL 1 DSP ERRORS REGISTER CHANNEL 2/CHANNEL 3 DSP ERRORS REGISTER CHANNEL 4/CHANNEL 5 DSP ERRORS REGISTER CHANNEL 6/CHANNEL 7 DSP ERRORS REGISTER CHANNEL 0 TO CHANNEL 7 ERROR REGISTER ENABLE REGISTER GENERAL ERRORS REGISTER 1 GENERAL ERRORS REGISTER 1 ENABLE GENERAL ERRORS REGISTER 2 GENERAL ERRORS REGISTER 2 ENABLE ERROR STATUS REGISTER 1 ERROR STATUS REGISTER 2 ERROR STATUS REGISTER 3 DECIMATION RATE (N) MSB REGISTER DECIMATION RATE (N) LSB REGISTER DECIMATION RATE (IF) MSB REGISTER DECIMATION RATE (IF) LSB REGISTER SRC LOAD SOURCE AND LOAD UPDATE REGISTER OUTLINE DIMENSIONS ORDERING GUIDE

Купить AD7779ACPZ на РадиоЛоцман.Цены — от 79 до 2 087 ₽

Купить AD7779ACPZ на РадиоЛоцман.Цены — от 79 до 2 087 ₽