Datasheet Texas Instruments CDC111FN — Даташит

| Производитель | Texas Instruments |

| Серия | CDC111 |

| Модель | CDC111FN |

Дифференциальный драйвер тактового сигнала 3,3 В LVPECL 28-PLCC

Datasheets

1-Line To 9-Line Differential LVPECL Clock Driver datasheet

PDF, 417 Кб, Версия: G, Файл опубликован: 28 авг 1999

Выписка из документа

Цены

Купить CDC111FN на РадиоЛоцман.Цены — от 4.75 до 13 055 ₽ Купить CDC111FN на РадиоЛоцман.Цены — от 4.75 до 13 055 ₽15 предложений от 12 поставщиков Интегральные микросхемы Тактовые микросхемы - Тактовые буферы и управляющие микросхемы | |||

| CDC111FN Texas Instruments | от 4.75 ₽ | ||

| CDC111FN Texas Instruments | от 657 ₽ | ||

| CDC111FN Texas Instruments | от 4 333 ₽ | ||

| CDC111FN Texas Instruments | по запросу | ||

Статус

| Статус продукта | В производстве (Рекомендуется для новых разработок) |

| Доступность образцов у производителя | Да |

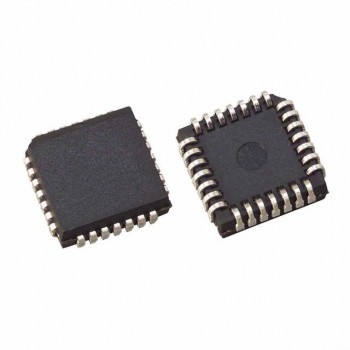

Корпус / Упаковка / Маркировка

| Pin | 28 |

| Package Type | FN |

| Industry STD Term | PLCC |

| JEDEC Code | S-PQCC-J |

| Package QTY | 37 |

| Carrier | TUBE |

| Маркировка | CDC111FN |

| Width (мм) | 11.51 |

| Length (мм) | 11.51 |

| Thickness (мм) | 4.06 |

| Pitch (мм) | 1.27 |

| Max Height (мм) | 4.57 |

| Mechanical Data | Скачать |

Параметры

| Input Frequency(Max) | 500 МГц |

| Input Level | LVPECL |

| Количество выходов | 9 |

| Output Frequency(Max) | 500 МГц |

| Output Level | LVPECL |

| Package Group | PLCC |

| Package Size: mm2:W x L | 28PLCC: 132 mm2: 11.51 x 11.51(PLCC) PKG |

| Rating | Catalog |

| VCC | 3.3 В |

| VCC Out | 3.3 В |

Экологический статус

| RoHS | Совместим |

Application Notes

- Using TI's CDC111/CDCVF111 W/ TLK3104SA Serial Transceiver for Gigabit EthernetPDF, 79 Кб, Файл опубликован: 31 окт 2001

This application report discusses jitter transfer of TI's CDC111/CDCVF111 clock drivers when driving TI's TLK3104 serial gigabit transceiver. This report summarizes worst case peak-to-peak and RMS jitter measurements taken at various points, as indicated in Figures 1 and 2. Two different clock sources are used to provide the reference clock signal for the clock drivers, and the output of each cloc - Jitter Performance of TI's CDC111/CDCVF111PDF, 149 Кб, Файл опубликован: 29 окт 2001

This application report discusses various jitter measurements of TI?s CDC111/CDCVF111 while being driven by three different clock sources (VCXOs). The data contained in this report shows that the CDC111/CDCVF111 does not add more than 3 ps of peak-to-peak jitter. Hence, the CDC111 and CDCVF111 are ideal for various SONET and Gigabit Ethernet applications where skew and jitter are of major concern. - Output Jitter of CDC111/CDCVF111 in ASIC Networking ApplicationPDF, 361 Кб, Файл опубликован: 2 ноя 2001

This report contains a number of peak-to-peak and cycle-to-cycle jitter measurements of TI?s CDC111 and CDCVF111 clock driver. In this ASIC event, both the CDC111/CDCVF111 clock drivers are used as a master clock distribution for the Gandalf Macro Family Testchip. Comprehensive jitter data as well as output signal levels were taken and thus are included for completeness. - DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CMLPDF, 135 Кб, Файл опубликован: 19 фев 2003

- AC Coupling Between Differential LVPECL, LVDS, HSTL and CML (Rev. C)PDF, 417 Кб, Версия: C, Файл опубликован: 17 окт 2007

This report provides a quick reference of ac-coupling techniques for interfacing between different logic levels. The four differential signaling levels found in this reportare low-voltage positive-referenced emitter coupled logic (LVPECL), low-voltage differential signals (LVDS), high-speed transceiver logic (HSTL), and current-modelogic (CML). From these four differential signaling levels, 16

Модельный ряд

Серия: CDC111 (1)

- CDC111FN

Классификация производителя

- Semiconductors > Clock and Timing > Clock Buffers > Differential