Datasheet Texas Instruments 66AK2L06XCMSA — Даташит

| Производитель | Texas Instruments |

| Серия | 66AK2L06 |

| Модель | 66AK2L06XCMSA |

Многоядерная однокристальная система DSP+ARM KeyStone II (SoC) 900-FCBGA от -40 до 100

Datasheets

66AK2L06 Multicore DSP+ARM KeyStone II System-on-Chip (SoC) datasheet

PDF, 1.9 Мб, Файл опубликован: 21 апр 2015

Выписка из документа

Цены

Купить 66AK2L06XCMSA на РадиоЛоцман.Цены — от 14 652 до 129 095 ₽ Купить 66AK2L06XCMSA на РадиоЛоцман.Цены — от 14 652 до 129 095 ₽13 предложений от 11 поставщиков Цифровой сигнальный процессор DSP, DSP Fixed-Point/Floating-Point 1.2GHz Medical 900Pin FCBGA | |||

| 66AK2L06XCMSA2 Texas Instruments | 52 460 ₽ | ||

| 66AK2L06XCMSA Texas Instruments | от 53 511 ₽ | ||

| 66AK2L06XCMSA Texas Instruments | 55 501 ₽ | ||

| 66AK2L06XCMSA Texas Instruments | по запросу | ||

Статус

| Статус продукта | В производстве (Рекомендуется для новых разработок) |

| Доступность образцов у производителя | Да |

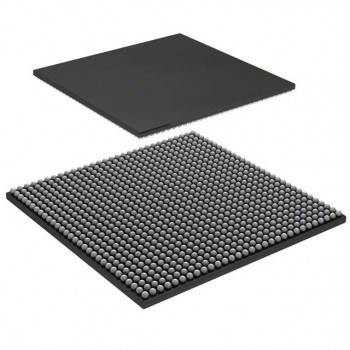

Корпус / Упаковка / Маркировка

| Pin | 900 | 900 | 900 |

| Package Type | CMS | CMS | CMS |

| Package QTY | 44 | 44 | 44 |

| Маркировка | A1GHZ | @2013 | 66AK2L06XCMS |

| Width (мм) | 25 | 25 | 25 |

| Length (мм) | 25 | 25 | 25 |

| Thickness (мм) | 2.98 | 2.98 | 2.98 |

| Mechanical Data | Скачать | Скачать | Скачать |

Параметры

| ARM CPU | 2 ARM Cortex-A15 |

| ARM MHz | 1200 Max. |

| Applications | Avionics and Defense,Medical,Test and Measurement |

| DRAM | DDR3,DDR3L |

| DSP | 4 C66x |

| DSP MHz | 1200 Max. |

| EMAC | 4-port 1Gb Switch |

| Hardware Accelerators | FFT Coprocessor,Digital Front End |

| I2C | 3 |

| JESD204B | 4 Lanes |

| On-Chip L2 Cache | 1024 KB (ARM Cluster),1024 KB (per C66x DSP core) |

| Operating Systems | Integrity,Linux,SYS/BIOS,VxWorks |

| Рабочий диапазон температур | от -40 до 100,0 до 100 C |

| Other On-Chip Memory | 3072 KB |

| PCI/PCIe | 2 PCIe Gen2 |

| Rating | Catalog |

| SPI | 3 |

| UART | 4 SCI |

| USB | 1 |

Экологический статус

| RoHS | Совместим |

Комплекты разработчика и оценочные наборы

- JTAG Emulators/ Analyzers: TMDSEMU560V2STM-U

XDS560v2 System Trace USB Debug Probe

Статус продукта: В производстве (Рекомендуется для новых разработок) - JTAG Emulators/ Analyzers: TMDSEMU560V2STM-UE

XDS560v2 System Trace USB & Ethernet Debug Probe

Статус продукта: В производстве (Рекомендуется для новых разработок) - JTAG Emulators/ Analyzers: TMDSEMU200-U

XDS200 USB Debug Probe

Статус продукта: В производстве (Рекомендуется для новых разработок) - Evaluation Modules & Boards: XEVMK2LX

66AK2L06 Evaluation Module

Статус продукта: В производстве (Рекомендуется для новых разработок)

Application Notes

- TPS544Bxx/TPS544Cxx Powering TCI6630K2L in Smart Reflex Class 0 TC ModePDF, 154 Кб, Файл опубликован: 18 сен 2015

This application report describes an application circuit example of the TPS544B/Cxx family of power management IC (PMIC) powering the Smart-Reflex digital core supply of the TCI6630K2L SoC. Smart-Reflex Class 0 Temperature Compensation (Class 0 TC) mode of operation of the TCI6630K2L device is emphasized. Assumption is that temperature compensation mode is enabled using the function provided in th - 66AK2L06 JESD Attach to ADC12J4000/DAC38J84 Getting Started Guide (Rev. B)PDF, 8.8 Мб, Версия: B, Файл опубликован: 20 июн 2016

- Keystone EDMA FAQPDF, 1.3 Мб, Файл опубликован: 1 сен 2016

This document is a collection of frequently asked questions (FAQs) on enhanced direct memory access (EDMA) on KeyStoneв„ў I (KS1) and KeyStone II (KS2) devices, along with useful collateral and software reference links. - System solution for avionics & defensePDF, 1.2 Мб, Файл опубликован: 23 сен 2015

- Keystone II DDR3 InitializationPDF, 73 Кб, Файл опубликован: 26 янв 2015

This application report provides a step-to-step initialization guide for the Keystone II device DDR3 SDRAM controller. - Power Management of KS2 Device (Rev. C)PDF, 61 Кб, Версия: C, Файл опубликован: 15 июл 2016

This application report lists the steps to enable Class 0 Temperature Compensation (Class 0 TC) mode of SmartReflexв„ў Subsystem (SRSS) module available on such devices. - Throughput Performance Guide for KeyStone II Devices (Rev. B)PDF, 866 Кб, Версия: B, Файл опубликован: 22 дек 2015

This application report analyzes various performance measurements of the KeyStone II family of processors. It provides a throughput analysis of the various support peripherals to different end-points and memory access. - Keystone II DDR3 Debug GuidePDF, 143 Кб, Файл опубликован: 16 окт 2015

This guide provides tools for use when debugging a failing DDR3 interface on a KeyStone II device. - Hardware Design Guide for KeyStone II DevicesPDF, 1.8 Мб, Файл опубликован: 24 мар 2014

- SERDES Link Commissioning on KeyStone I and II DevicesPDF, 138 Кб, Файл опубликован: 13 апр 2016

The serializer-deserializer (SerDes) performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU. This application report explains the SerDes transmit and receive parameters tuning, tools and some debug techniques for TI Keystone I and Keystone II devices. - PCIe Use Cases for KeyStone DevicesPDF, 320 Кб, Файл опубликован: 13 дек 2011

- Optimizing Loops on the C66x DSPPDF, 585 Кб, Файл опубликован: 9 ноя 2010

- The C6000 Embedded Application Binary Interface Migration Guide (Rev. A)PDF, 20 Кб, Версия: A, Файл опубликован: 10 ноя 2010

The C6000 compiler tools support a new ELF-based ABI named EABI. Prior to this time, the compiler only supported a single ABI, which is now named COFF ABI. The following compelling best-in-class features are available under the C6000 EABI:GeneralZero-init globals: “int gvar;” gets set to 0 before main runs.Dynamic linking: Add code to a running system.Native ROM - Clocking Design Guide for KeyStone DevicesPDF, 1.5 Мб, Файл опубликован: 9 ноя 2010

- DDR3 Design Requirements for KeyStone Devices (Rev. B)PDF, 582 Кб, Версия: B, Файл опубликован: 5 июн 2014

- Multicore Programming Guide (Rev. B)PDF, 1.8 Мб, Версия: B, Файл опубликован: 29 авг 2012

As application complexity continues to grow, we have reached a limit on increasing performance by merely scaling clock speed. To meet the ever-increasing processing demand, modern System-On-Chip solutions contain multiple processing cores. The dilemma is how to map applications to multicore devices. In this paper, we present a programming methodology for converting applications to run on multicore - TI DSP BenchmarkingPDF, 62 Кб, Файл опубликован: 13 янв 2016

This application report provides benchmarks for the C674x DSP core, the C66x DSP core and the ARMВ®CortexВ®-A15 core. This document also shows how to reproduce these benchmarks on specific hardware platforms.

Модельный ряд

Серия: 66AK2L06 (4)

- 66AK2L06XCMS 66AK2L06XCMS2 66AK2L06XCMSA 66AK2L06XCMSA2

Классификация производителя

- Semiconductors > Processors > Digital Signal Processors > C6000 DSP + ARM Processors > 66AK2x